[芯片制造] 芯片测试:WAT、CP、FT. 日期:2025-11-24 22:46:08 点击:237 好评:0

[芯片制造] 芯片测试:WAT、CP、FT. 日期:2025-11-24 22:46:08 点击:237 好评:0

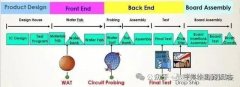

WAT WAT(Wafer Acceptance Test)测试,也叫PCM(Process Control Monitoring),对Wafer 划片槽(Scribe Line)测试键(Test Key)的测试,通过电性参数来监控各步工艺是否正常和稳定. 例如CMOS的电容,电...

[芯片制造] 电子元器件失效的常规分类、检测及案例分析 日期:2025-11-24 20:21:00 点击:216 好评:0

[芯片制造] 电子元器件失效的常规分类、检测及案例分析 日期:2025-11-24 20:21:00 点击:216 好评:0

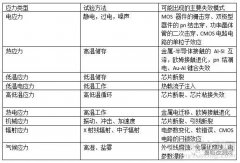

元器件设计、材料、结构、工艺缺陷引起的失效是元器件常见失效之一,其失效由元器件自身缺陷决定,应用环境和工作中施加的条件是失效的外因,不管应用环境和工作中施加的条件...

[芯片制造] 芯测之声(第六期) 日期:2025-11-18 19:13:00 点击:219 好评:0

[芯片制造] 芯测之声(第六期) 日期:2025-11-18 19:13:00 点击:219 好评:0

数字芯片测试全流程解析 一.测试前准备 1.了解测试机及如何操作 2.了解所测芯片的芯片手册 二.测试要求 1.明确测试项目 2.编写测试向量表 3.画PCB板,进行硬件测试 三.芯片测试是确保产...

[芯片制造] 芯测之声(第七期) 日期:2025-11-18 17:06:00 点击:146 好评:0

[芯片制造] 芯测之声(第七期) 日期:2025-11-18 17:06:00 点击:146 好评:0

芯片测试四大核心技术解析!连接性 / 功能 / 钳位电压 / 漏电流原理大揭秘 芯片从设计到量产,测试是保障品质的关键环节。其中连接性、功能、输入钳位电压和漏电流测试,堪称芯片...

[芯片制造] 一文看懂AI SoC芯片 日期:2025-11-17 18:17:40 点击:362 好评:0

[芯片制造] 一文看懂AI SoC芯片 日期:2025-11-17 18:17:40 点击:362 好评:0

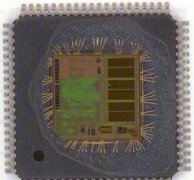

什么是SoC? 作为智能手机、汽车电子、人工智能、工业控制等领域的大脑,SoC (System on Chip, 片上系统) 是一种将计算核心、存储系统、通信接口以及各种外设集成到一个单一芯片上的高...

[芯片制造] 芯片失效分析原理及步骤 日期:2025-11-13 21:24:11 点击:253 好评:0

[芯片制造] 芯片失效分析原理及步骤 日期:2025-11-13 21:24:11 点击:253 好评:0

失效分析近年开始从军工向普通企业普及。它一般根据失效模式和现象,通过分析和验证,模拟重现失效的现象,找出失效的原因,挖掘出失效的机理的活动。在提高产品质量,技术开...

[芯片制造] 失效分析的概念、主要步骤及解决方案 日期:2025-11-13 20:20:00 点击:236 好评:0

[芯片制造] 失效分析的概念、主要步骤及解决方案 日期:2025-11-13 20:20:00 点击:236 好评:0

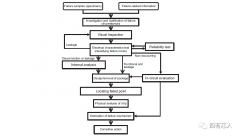

失效分析是一门发展中的新兴学科,近年开始从军工向普通企业普及。它一般根据失效模式和现象,通过分析和验证,模拟重现失效的现象,找出失效的原因,挖掘出失效的机理的活动...

[芯片制造] 集成电路失效分析步骤 日期:2025-11-13 19:09:00 点击:253 好评:0

[芯片制造] 集成电路失效分析步骤 日期:2025-11-13 19:09:00 点击:253 好评:0

1. 开封前检查,外观检查,X光检查,扫描声学显微镜检查。 2. 开封显微镜检查。 3. 电性能分析,缺陷定位技术、电路分析及微探针分析。 4. 物理分析,剥层、聚焦离子束(FIB),扫描电...

[芯片制造] 芯片故障分析流程-failure analysis flow 日期:2025-11-13 18:44:00 点击:213 好评:0

[芯片制造] 芯片故障分析流程-failure analysis flow 日期:2025-11-13 18:44:00 点击:213 好评:0

1. 芯片故障分析流程: 01.接收故障件并收集相关失效信息。 02.Level-1: 非破坏性实验,如目检,X-ray等。 03.Level-2:电气故障分析,尝试复现失效模式。如Open/Short,Decap,EMMI/InGaAs,OBIR...

[芯片制造] 关于芯片设计的一些基本知识 日期:2025-11-12 20:09:00 点击:124 好评:0

[芯片制造] 关于芯片设计的一些基本知识 日期:2025-11-12 20:09:00 点击:124 好评:0

引言:之前给大家介绍了芯片的制造和封装。今天这篇,我们来看看芯片的设计。 █ 芯片的设计理念 众所周知,芯片拥有极为复杂的结构。 以英伟达的B200芯片为例,在巴掌大的面积...