[芯片制造] Cpk是什么?一个数字告诉你芯片批次稳不稳 日期:2026-04-26 21:29:48 点击:102 好评:0

[芯片制造] Cpk是什么?一个数字告诉你芯片批次稳不稳 日期:2026-04-26 21:29:48 点击:102 好评:0

拿到一批芯片的测试数据,良率98%,看起来不错。 但客户用了之后反馈,有些芯片性能飘忽,时好时坏。 问题出在哪?良率告诉你有多少芯片合格,但没告诉你这批芯片的一致性怎么...

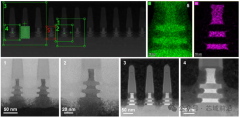

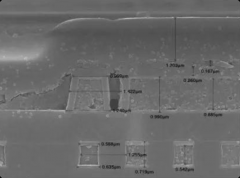

[芯片制造] 一文了解新型晶体管(环栅晶体管GAA)制造技术 日期:2026-04-26 20:53:26 点击:127 好评:0

[芯片制造] 一文了解新型晶体管(环栅晶体管GAA)制造技术 日期:2026-04-26 20:53:26 点击:127 好评:0

一、 CMOS晶体管发展方向 金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transistors,MOSFETs)是一种广泛应用于模拟电路与数字电路的基本单元,它在构建集成电路中扮演...

[芯片制造] 半导体 Process Flow 第一关:Pad Oxide Growth 日期:2026-04-19 17:55:00 点击:170 好评:0

[芯片制造] 半导体 Process Flow 第一关:Pad Oxide Growth 日期:2026-04-19 17:55:00 点击:170 好评:0

看懂芯片制造第一步:Pad Oxide Growth 为何薄到看不见,却关键到不能错 在很多经典 CMOS(Complementary Metal-Oxide-Semiconductor,互补金属氧化物半导体)前道工艺里,AA(Active Area,有源区)模...

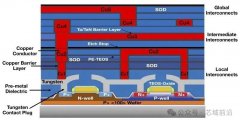

[芯片制造] 为啥W的Barrier Layer是Ti/TiN顺序而Cu是TaN/Ta? 日期:2026-04-19 16:42:00 点击:106 好评:0

[芯片制造] 为啥W的Barrier Layer是Ti/TiN顺序而Cu是TaN/Ta? 日期:2026-04-19 16:42:00 点击:106 好评:0

芯域前沿 聚焦半导体行业最新动态、技术解析与深度科普,覆盖芯片设计、制造、封测全产业链。 无论您是工程师、投资者还是科技爱好者,在这里都能读懂中国芯的崛起逻辑与未来...

[芯片制造] 半导体失效分析(Failure Analysis)简介 日期:2026-04-19 15:03:00 点击:106 好评:4

[芯片制造] 半导体失效分析(Failure Analysis)简介 日期:2026-04-19 15:03:00 点击:106 好评:4

为什么先进芯片越难做,越离不开FA?半导体失效分析全景图 很多人第一次听到半导体失效分析FA(Failure Analysis),脑子里会自动浮现一个画面:工程师拿着工具,把坏芯片切开、磨开...

[芯片制造] 车规芯片到底比普通芯片多测了什么? 日期:2026-04-07 21:50:11 点击:144 好评:0

[芯片制造] 车规芯片到底比普通芯片多测了什么? 日期:2026-04-07 21:50:11 点击:144 好评:0

今天就先聊两个最核心的测试组: A组(环境应力)和 B组(寿命与封装可靠性) 。 一、A组:环境应力测试 A组的逻辑其实很简单: 模拟汽车环境。 车里的芯片环境有多恶劣? 东北的...

[芯片制造] 晶圆CP开发调试与量产测试流程 日期:2026-03-29 20:44:22 点击:117 好评:0

[芯片制造] 晶圆CP开发调试与量产测试流程 日期:2026-03-29 20:44:22 点击:117 好评:0

晶圆探针测试(Chip Probe Test,晶圆探针测试)是在晶圆切割前,对每一个裸片(Die)进行电性能和基本功能的筛选。它的作用是尽早剔除不良Die,降低封装成本、提升成品率和出货质量...

[芯片制造] 生活中常见的芯片类型有哪些? 日期:2026-03-05 18:35:00 点击:105 好评:0

[芯片制造] 生活中常见的芯片类型有哪些? 日期:2026-03-05 18:35:00 点击:105 好评:0

在智能化时代的今天,芯片无处不在。它们融入到手机、家电、汽车、医疗设备、办公用品等各种各样的智能电子设备里。芯片为现代生活带来了便捷与智能。那么,生活中都有哪些常...

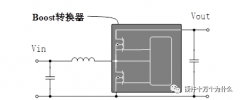

[芯片制造] Boost电路的工作过程 日期:2025-12-07 17:49:00 点击:324 好评:2

[芯片制造] Boost电路的工作过程 日期:2025-12-07 17:49:00 点击:324 好评:2

Boost电源电路是一种DC-DC升压电路,能够将低电压升高到较高电压。其基本原理是利用电感储能和电容储能的方式,通过开关管的开关控制,将输入电压进行短时间内的变化,从而使输出...

[芯片制造] 芯片失效分析(FA)介绍 日期:2025-12-05 21:39:41 点击:278 好评:2

[芯片制造] 芯片失效分析(FA)介绍 日期:2025-12-05 21:39:41 点击:278 好评:2

失效分析 (Failure Analysis,简称FA) 是对已失效的半导体器件进行的一种事后检查活动。它依据失效模式和现象,通过电测试及必要的物理、化学分析技术,探究并验证失效行为,最终...