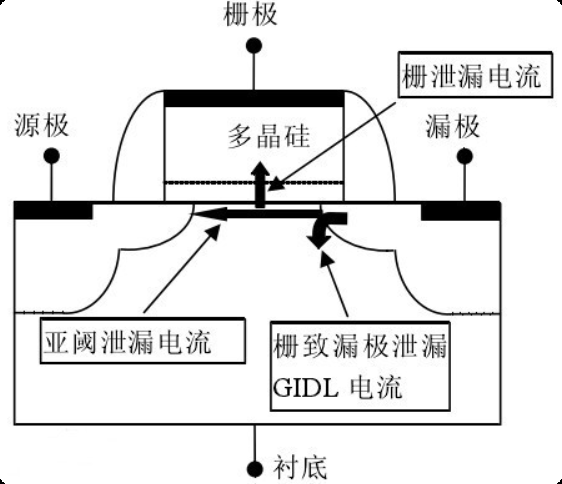

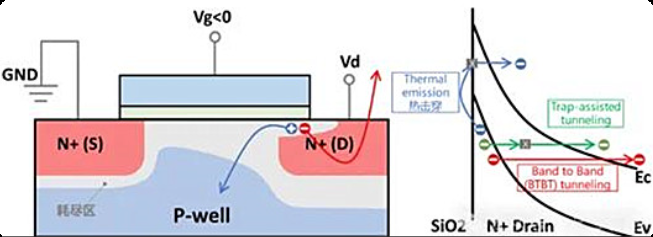

栅致漏极泄漏(Gate Induced Drain Leakage,简称GIDL)是金属氧化物半导体场效应晶体管(MOSFET)在关断状态下发生的一种重要漏电机制。该效应主要出现在栅极与漏极的交叠区域,由带间隧穿(Band-To-Band Tunneling, BTBT)引起,并随着器件尺寸的缩小与栅氧化层厚度的减薄而愈发显著,已成为影响深亚微米及以下工艺器件可靠性与功耗的关键因素之一。GIDL是如何发生的 GIDL的产生需要满足几个条件:首先,栅极与漏极必须存在实际工艺导致的交叠(overlap);另外,器件工作于亚阈值区;最后,漏端需要施加较高的电压以形成强电场。以NMOS为例,当栅压为负、漏端电压较高时,在栅漏交叠区下方会形成耗尽区。在强电场作用下,硅与二氧化硅界面处的缺陷可作为产生-复合中心,辅助载流子从价带经陷阱态跃迁至导带。若电场足够强,电子可直接通过量子隧穿从价带穿越禁带进入导带,发生带间隧穿。隧穿产生的电子被漏极收集,空穴则被扫入衬底,从而形成从漏极流向衬底的泄漏电流。  从物理本质看,GIDL源于量子隧穿效应。当栅-漏电压差较大时,栅下电场显著增强,导致漏端附近半导体能带剧烈弯曲,使价带顶与导带底在空间上接近。价带电子无需热激发,即可直接隧穿进入导带,形成额外漏电流。这一机制与传统热激发导电不同,是纳米尺度MOS器件中不可忽略的现象。 什么因素会影响GIDL GIDL电流的强弱受多种器件结构参数与工作条件的影响。在结构方面,栅氧化层厚度至关重要:氧化层越薄,栅极电场越强,能带弯曲程度越大,GIDL电流随之急剧增加。栅与漏的交叠程度也会显著影响GIDL,交叠越大效应越明显,这与侧墙宽度以及轻掺杂漏/晕环注入工艺相关。硅/氧化硅界面损伤、栅氧中存在F-N隧穿等因素也会加剧GIDL。衬底掺杂浓度同样起作用,较高掺杂会使能带更易弯曲,增强GIDL效应。在工作条件上,漏极电压的升高会直接加大栅漏间电场,为隧穿提供更有利条件,导致GIDL电流显著上升。  GIDL会带来哪些问题 GIDL效应给集成电路带来多方面的挑战。在功耗方面,GIDL电流是静态泄漏电流的重要组成部分,在器件处于关态或等待状态时往往占主导地位,这会增加芯片的整体静态功耗,对低功耗设计及电池续航能力构成威胁。在性能与可靠性层面,GIDL可引起阈值电压漂移,影响器件开关特性与电路逻辑准确性,长期作用还会加速器件老化,缩短芯片使用寿命,增加故障风险与维护成本。对于存储器件,GIDL还会影响其擦写操作可靠性。随着工艺进入超深亚微米时代,器件尺寸不断缩小,GIDL引发的可靠性问题日益严重。 如何抑制GIDL效应 为缓解GIDL带来的问题,可从器件结构与电路设计两方面入手。在器件层面,采用高介电常数(高k)栅介质材料替代传统二氧化硅,可在保持栅电容的同时适当增加介质层厚度,从而降低栅极电场强度;通过优化工艺调整衬底掺杂分布,特别是降低漏端附近的掺杂浓度,有助于减轻能带弯曲、抑制隧穿发生。在电路设计方面,合理设置工作偏置电压,避免出现过大的栅-漏电压差,可以从源头上减弱GIDL效应;采用先进的电路架构与设计方法也有助于提升电路对GIDL的抗干扰能力。 |