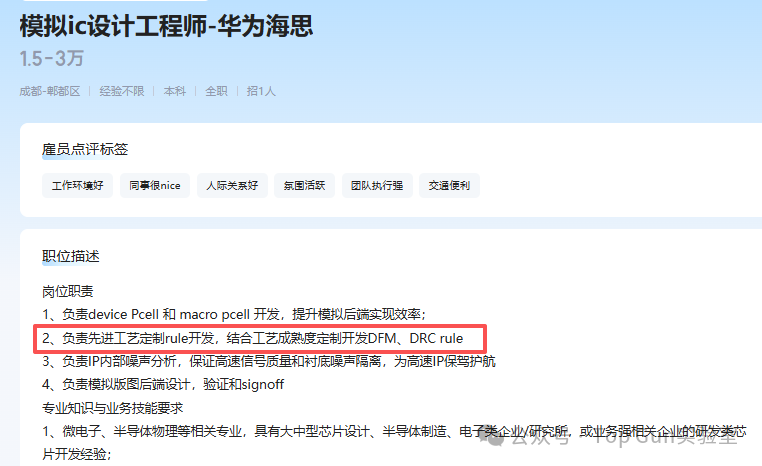

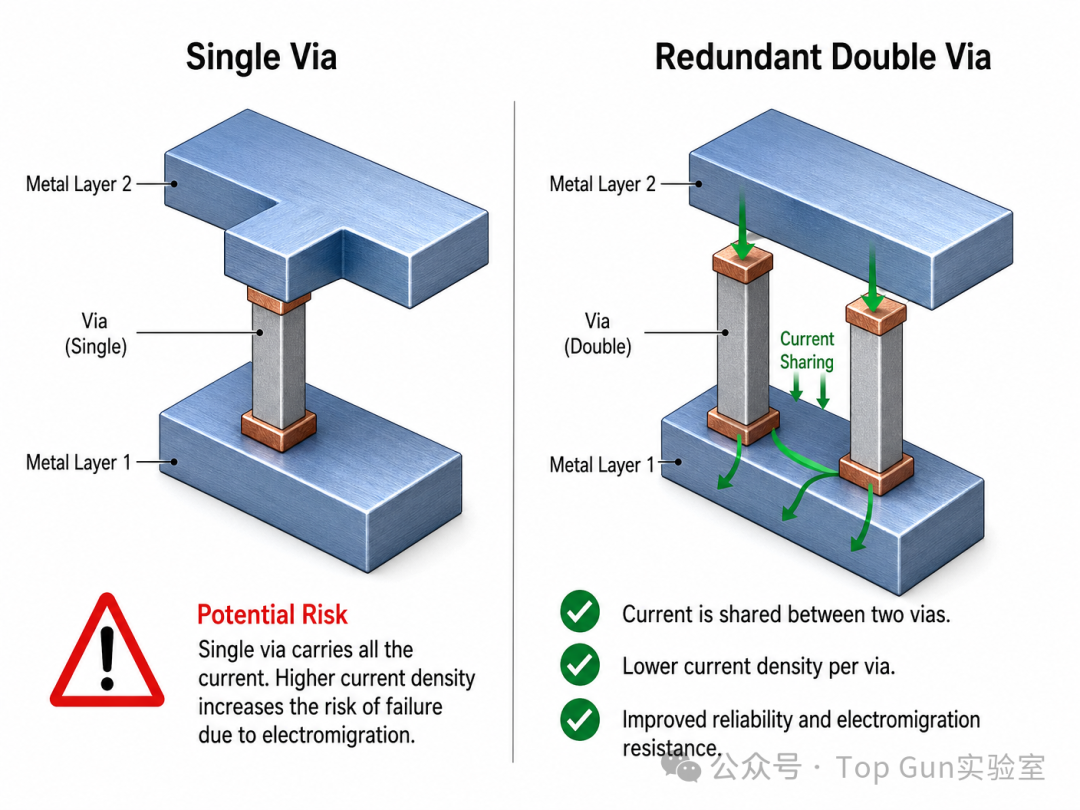

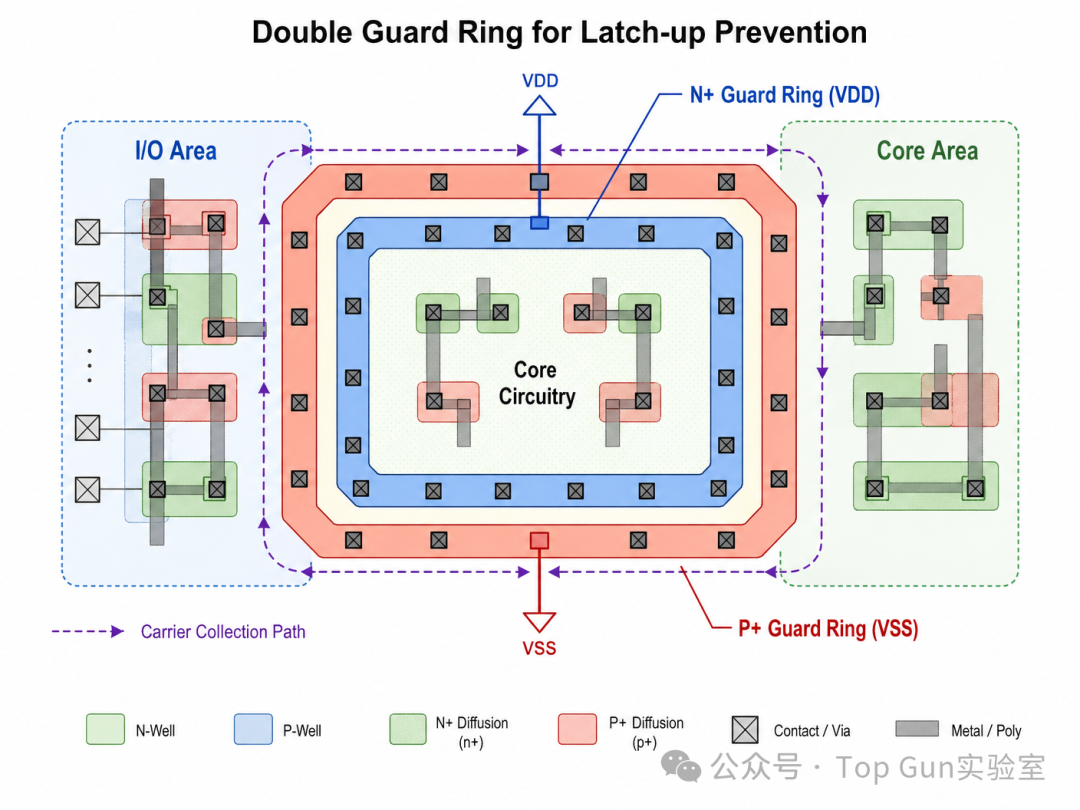

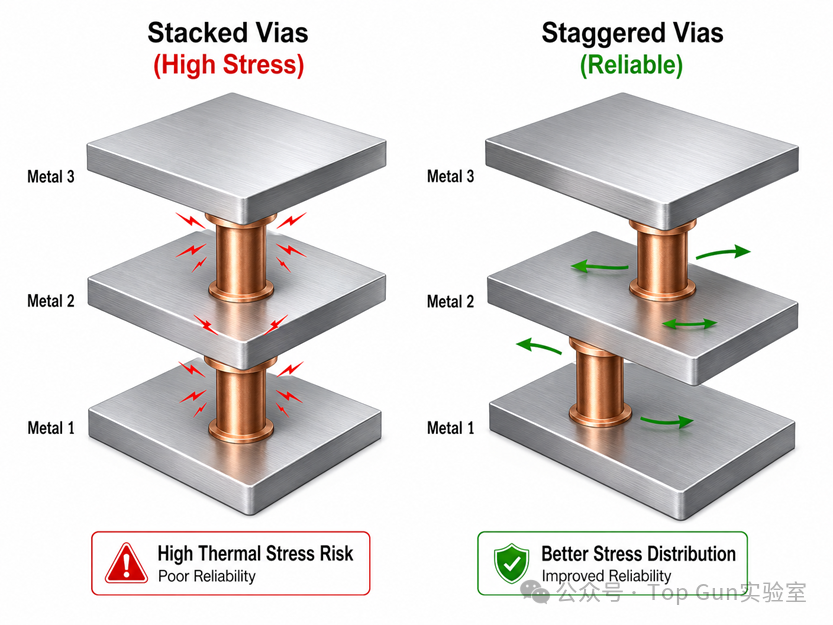

芯片设计工程师都清楚Foundry(晶圆厂)提供的Design Rule Manual和配套的DRC(设计规则检查)工具是基本法。DRC过了,LVS(版图电路一致性检查)也过了,是不是就意味着可以高枕无忧,等着流片成功了?答案往往是残酷的:不一定。 尤其是在先进工艺节点,Foundry的DRC规则是普适性的,旨在覆盖大多数设计场景。但对于特定产品、特定应用,或者在追求极致性能和可靠性时,这些“通用规则”就显得力不从心了。 大厂如华为海思,可能与Foundry有深度合作,获得定制甚至“加严版”的DRC规则;而对于更多中小型Design House来说,这些“加强版”规则不会主动送上门。小厂能做的,就是通过一次次流片、一次次失效分析,用血泪教训去沉淀出自己的“内部DFX Checklist”,在Foundry DRC的基础上,对某些关键参数进行“加严”,从而筑起自己的“护城河”。  下面结合一些实际案例,聊聊那些经验总结出来的“加严规则”和它们背后的故事。 一、 可靠性的“血泪教训”:Via、LDE与Latch-up 1. Via冗余:为什么Foundry说一个Via够了,我们却坚持打两个? Foundry的DRC告诉你,连接两层金属,一个Via就够了。但有的公司的Checklist会强制要求:关键路径、大电流路径,以及所有40nm以下工艺的Via,必须打双孔(Redundant Via)。  背后的故事:早期流片,某公司发现一些芯片在高温老化后失效。失效分析发现,是单个Via在长期大电流冲击下发生了电迁移(Electromigration, EM),导致开路。Foundry的DRC认为单个Via满足电流密度要求,但他们没考虑到该公司产品在极端工况下的长期可靠性需求。 2. LDE (Layout Dependent Effects) 效应:那些肉眼难辨的“隐形杀手” Foundry的DRC对管子间距、Well边缘距离有基本要求。但对于模拟电路中的匹配管,这些规则远远不够。 WPE (Well Proximity Effect) 加严:Foundry可能允许匹配管距离Well Edge 0.5μm,但某公司的Checklist会要求至少2μm,甚至5μm以上。  背后的故事:离子注入时,光刻胶侧壁的散射效应会导致Well边缘附近的掺杂浓度不均匀。某公司曾因匹配管靠近Well边缘,导致Vt漂移,差分对失配,最终影响了ADC的线性度。 3. Latch-up预防:I/O与Core之间的“柏林墙”Foundry的DRC会检查Latch-up相关的间距。但某公司内部的Checklist会更进一步:I/O单元与内部Core之间,必须有至少20μm-50μm的隔离区,且中间必须打上两道“背靠背”的Guard Ring(N+ Ring连VDD,P+ Ring连VSS)。  背后的故事:某公司的产品在ESD(静电放电)测试中,曾出现过Latch-up现象,导致芯片永久性损坏。虽然I/O端的ESD保护电路正常工作,但注入的载流子还是通过衬底“渗透”到了Core区域。双重Guard Ring就像一道“柏林墙”,能更有效地收集这些载流子,防止它们触发Core区域的寄生SCR路径。 二、 封装与可靠性的“生存法则”:Via 为什么不能直着叠? Foundry的DRC允许Via Stacking(通孔堆叠),但在某公司的加严Checklist中,这往往是重点关照的对象。 加严Checklist规则:严禁在大面积或关键路径上进行多层Via的直接垂直堆叠 (Stacked Via),必须采用Offset(偏移)布局,形成阶梯状(Staggered Via)。  背后的故事:垂直堆叠的Via在制造和封装过程中,会因为金属与介质材料的热膨胀系数(CTE)不匹配而产生巨大的热应力集中。在芯片经历热循环测试时,直叠式Via就像一个脆弱的“支柱”,极易在应力最集中的连接处产生微裂纹甚至断裂。我们曾遇到过封装回来的芯片在老化测试中失效,开封后发现就是Via堆叠处断了。从此,我们的Checklis规定:除非空间极度受限,否则必须做Offset布局,以分散应力,确保长期可靠性。 三、 良率与性能的“隐形博弈”:Dummy与屏蔽 1. Dummy Fill的艺术:不只是为了CMP Foundry的DRC关注Dummy Fill的密度,以保证CMP(化学机械抛光)的平坦度。但某公司的Checklist有更精细的要求:在敏感信号线旁2μm范围内,严禁放置Dummy。背后的故事:早期该公司严格按照Foundry规则填充Dummy,却发现一些高频模拟信号的性能不达标。分析发现,Dummy Metal引入了额外的寄生电容,改变了信号的传输特性。从此,Dummy Fill不再是简单的“填空”,而是一门需要权衡寄生效应的艺术。 2. 屏蔽与隔离:数字噪声的“渗透” 在数模混合芯片中,数字电路的噪声对模拟电路是致命的。Foundry会提供一些隔离建议,但我们往往需要更强的措施。 DNW(Deep N-Well) 隔离加严:某公司的Checklist规定:所有敏感模拟模块必须包裹在DNW中,且DNW的偏置电压必须经过独立的RC滤波。因为即使有DNW,如果其偏置电压直接取自受数字电路污染的电源,噪声依然会通过DNW传导。独立的滤波网络,能为模拟电路提供一个“干净”的偏置环境。 Shielding Via密度:Foundry的DRC可能只要求Shielding Metal连接到地。但某公司的Checklist会要求:时钟线两侧的Shielding金属,必须每隔5μm打一个Via到地。因为如果Shielding Metal接地不充分,它本身就可能成为一个“悬空天线”,反而引入噪声。高密度的Via接地,确保了Shielding的有效性。 四、构建你自己的“护城河”:Checklist的诞生与演进这些“加严规则”并非一蹴而就,它们是Design House在无数次流片、测试、失效分析中,用真金白银和宝贵时间换来的经验结晶。每一次失败,都是一次学习的机会,促使我们去思考:Foundry的规则为什么不够?我们还需要补充什么? 对于中小型Design House而言,没有大厂与Foundry深度定制规则的优势,更需要主动去构建和完善自己的DFX Checklist。这个Checklist不仅仅是规则的堆砌,更是对产品特性、应用场景、工艺弱点的深刻理解。它会随着工艺的演进、产品的迭代而不断更新,成为公司最宝贵的技术资产。 互动话题:在你的设计生涯中,有没有遇到过Foundry DRC过了,但最终还是“翻车”的经历?你们公司有哪些类似的“私域加严规则”?欢迎在评论区分享你的“避坑指南”,让我们一起学习,共同进步! |