[芯片制造] Loadboard上的去耦电容:放多少、放哪、放多大? 日期:2026-05-11 21:59:11 点击:139 好评:0

[芯片制造] Loadboard上的去耦电容:放多少、放哪、放多大? 日期:2026-05-11 21:59:11 点击:139 好评:0

芯片测试时,有时会遇到这种情况:直流参数正常,一跑功能测试就出错;或者同一批Loadboard,有的工位稳,有的工位飘。 查程序、查座子、查机台,都没问题。最后发现是板子上的去...

[相关技术] 电机电容测量方法及标准电容器比较 日期:2026-05-11 20:48:04 点击:75 好评:0

[相关技术] 电机电容测量方法及标准电容器比较 日期:2026-05-11 20:48:04 点击:75 好评:0

一站式智能化解决方案服务商,覆盖工业控制、工业互联、智能装备、工业软件、行业应用、电子测量、城市生命线等应用 ,欢迎扫二维码添加好友/私信联系,谢谢您的关注! 在电机...

[相关技术] 20pA的跳动,竟然只是因为旁边亮着一盏台灯? 日期:2026-05-11 19:32:00 点击:195 好评:0

[相关技术] 20pA的跳动,竟然只是因为旁边亮着一盏台灯? 日期:2026-05-11 19:32:00 点击:195 好评:0

芯片测试中,有些信号很小。比如微伏级的电压、皮安级的漏电流、毫微伏级的噪声。这种信号非常容易被干扰淹没。有时候程序和数据看起来都正常,但结果就是不稳定,今天测一个...

[芯片制造] 芯片可靠性之早期失效率 日期:2026-05-08 22:30:20 点击:158 好评:0

[芯片制造] 芯片可靠性之早期失效率 日期:2026-05-08 22:30:20 点击:158 好评:0

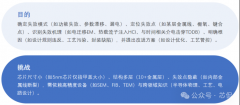

ELFR是半导体可靠性测试中的一个重要概念,英文全称:Early Life Failure Rate,中文译为早期失效率。目的是量化评估产品在浴盆曲线中早期失效期的失效率水平。代表了一种更先进、更高...

[芯片制造] 芯片失效分析解读 日期:2026-05-08 20:13:43 点击:164 好评:0

[芯片制造] 芯片失效分析解读 日期:2026-05-08 20:13:43 点击:164 好评:0

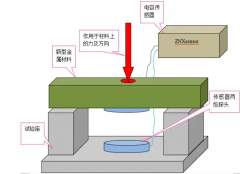

芯片失效分析(Chip Failure Analysis, Chip FA)是针对半导体集成电路(IC)失效的系统性排查过程,旨在通过多维度检测与逻辑推理,定位失效位置、揭示失效机理(如电迁移、栅氧击穿、...

[芯片制造] 先进制程晶圆厂:良率与利润的关系 日期:2026-05-07 22:15:54 点击:107 好评:0

[芯片制造] 先进制程晶圆厂:良率与利润的关系 日期:2026-05-07 22:15:54 点击:107 好评:0

以下文章来源于贝影Alpha-芯片新视界,作者贝影Alpha 贝影Alpha-芯片新视界 . 以理论物理博士的专业积淀,从多维度拆解市场动态,用第一性原理透视涨跌本质,分享独特投资心得。像分...

[芯片制造] 芯片设计的“隐秘角落” 日期:2026-04-27 22:36:29 点击:135 好评:0

[芯片制造] 芯片设计的“隐秘角落” 日期:2026-04-27 22:36:29 点击:135 好评:0

芯片设计工程师都清楚Foundry(晶圆厂)提供的Design Rule Manual和配套的DRC(设计规则检查)工具是基本法。DRC过了,LVS(版图电路一致性检查)也过了,是不是就意味着可以高枕无忧,等...

[芯片制造] Cpk是什么?一个数字告诉你芯片批次稳不稳 日期:2026-04-26 21:29:48 点击:162 好评:0

[芯片制造] Cpk是什么?一个数字告诉你芯片批次稳不稳 日期:2026-04-26 21:29:48 点击:162 好评:0

拿到一批芯片的测试数据,良率98%,看起来不错。 但客户用了之后反馈,有些芯片性能飘忽,时好时坏。 问题出在哪?良率告诉你有多少芯片合格,但没告诉你这批芯片的一致性怎么...

[芯片制造] 一文了解新型晶体管(环栅晶体管GAA)制造技术 日期:2026-04-26 20:53:26 点击:164 好评:0

[芯片制造] 一文了解新型晶体管(环栅晶体管GAA)制造技术 日期:2026-04-26 20:53:26 点击:164 好评:0

一、 CMOS晶体管发展方向 金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transistors,MOSFETs)是一种广泛应用于模拟电路与数字电路的基本单元,它在构建集成电路中扮演...

[芯片制造] 半导体 Process Flow 第一关:Pad Oxide Growth 日期:2026-04-19 17:55:00 点击:194 好评:2

[芯片制造] 半导体 Process Flow 第一关:Pad Oxide Growth 日期:2026-04-19 17:55:00 点击:194 好评:2

看懂芯片制造第一步:Pad Oxide Growth 为何薄到看不见,却关键到不能错 在很多经典 CMOS(Complementary Metal-Oxide-Semiconductor,互补金属氧化物半导体)前道工艺里,AA(Active Area,有源区)模...