[测试工程] 测试程序版本乱象:三个坏习惯,正在悄悄吃掉 日期:2026-04-26 17:45:00 点击:151 好评:0

[测试工程] 测试程序版本乱象:三个坏习惯,正在悄悄吃掉 日期:2026-04-26 17:45:00 点击:151 好评:0

版本号不更新、修改不写备注、测试机上的程序和服务器不同步这三个问题,你的团队有没有中招? 如果中了一个以上,恭喜你,你们的测试程序已经进入了混沌状态。 今天不说大道...

[测试工程] 半导体可靠性测试:V-ramp与J-ramp斜坡测试技术 日期:2026-04-19 19:20:10 点击:210 好评:0

[测试工程] 半导体可靠性测试:V-ramp与J-ramp斜坡测试技术 日期:2026-04-19 19:20:10 点击:210 好评:0

一颗芯片能不能活过十年,工程师往往先看这两条斜坡:V-ramp与J-ramp全解 JEDEC(Joint Electron Device Engineering Council,电子器件工程联合委员会)JESD35 把 V-ramp(Voltage Ramp,电压斜坡)和 J...

[可靠性测试] HTOL集成电路老化测试 日期:2026-04-03 22:10:52 点击:111 好评:2

[可靠性测试] HTOL集成电路老化测试 日期:2026-04-03 22:10:52 点击:111 好评:2

HTOL(High Temperature Operating Life)测试是评估集成电路(芯片)可靠性的一项关键性测试,主要通过高温激活失效机制来评估芯片寿命和长期通电运行的可靠性、稳定性。 主要的测试方法有...

[可靠性测试] HTOL&HAST可靠性测试 日期:2026-03-15 21:10:19 点击:221 好评:0

[可靠性测试] HTOL&HAST可靠性测试 日期:2026-03-15 21:10:19 点击:221 好评:0

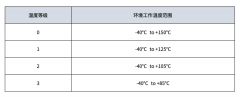

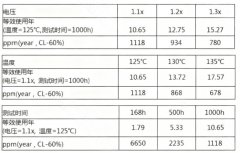

1. 前言 本次介绍上篇《芯片测试学习笔记》文章提到的可靠性测试项其中两项:HTOL和HAST测试。 2. HTOL(High Temperature Operation Life) HTOL测试是芯片电路可靠性的一项关键性的基础测试,采用...

[可靠性测试] 芯片可靠性之Burn-in 日期:2026-03-15 18:53:35 点击:119 好评:0

[可靠性测试] 芯片可靠性之Burn-in 日期:2026-03-15 18:53:35 点击:119 好评:0

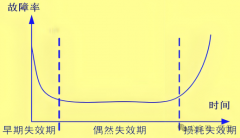

一. Burn-in 的概念 Burn-in的中文是老化或预烧。 核心原理:通过施加高于正常条件的电应力和热应力,让芯片在出厂前提前工作一段时间,从而迫使那些具有潜在缺陷、会早期失效的芯...

[测试工程] 芯片可靠性实验之HTOL 日期:2026-03-15 17:44:00 点击:129 好评:0

[测试工程] 芯片可靠性实验之HTOL 日期:2026-03-15 17:44:00 点击:129 好评:0

一 . HTOL 的概念 HTOL的英文全称为High Temperature Operation Life ,可以理解为芯片的加速老化实验。通过模拟芯片在几年甚至十几年(涵盖下图中早期失效期与使用寿命期)正常使用下可能出现...

[测试工程] 半导体ATE中高频高速接口测试的“速度与激情” 日期:2026-03-15 16:23:00 点击:118 好评:2

[测试工程] 半导体ATE中高频高速接口测试的“速度与激情” 日期:2026-03-15 16:23:00 点击:118 好评:2

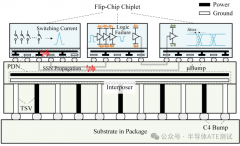

感恩科技的发展,AI 正在逐步改写我们的工作学习模式,Q4各家半导体设备厂商举办的技术峰会里,对AI的讨论也层出不穷。高速接口是谈及AI,一个无法绕过的话题。如今,数据传输速...

[可靠性测试] HTOL与Burn-in的差异点 日期:2026-03-10 23:01:58 点击:291 好评:0

[可靠性测试] HTOL与Burn-in的差异点 日期:2026-03-10 23:01:58 点击:291 好评:0

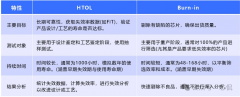

HTOL(高温工作寿命测试)和 Burn-in(老化测试)在半导体可靠性测试中关系密切,它们有显著的重叠,但侧重点不同。简单来说,Burn-in 是 HTOL 的一种应用形式。 主要区别: 以下是HTOL(...

[可靠性测试] 一文读懂芯片可靠性试验项目 日期:2026-03-10 20:14:00 点击:203 好评:0

[可靠性测试] 一文读懂芯片可靠性试验项目 日期:2026-03-10 20:14:00 点击:203 好评:0

可靠性试验的定义与重要性 可靠性试验是一种系统化的测试流程,通过模拟芯片在实际应用中可能遇到的各种环境条件和工作状态,对芯片的性能、稳定性和寿命进行全面评估。 在芯...

[可靠性测试] 芯片半导体可靠性测试项目 日期:2026-03-10 19:09:00 点击:95 好评:2

[可靠性测试] 芯片半导体可靠性测试项目 日期:2026-03-10 19:09:00 点击:95 好评:2

芯片半导体可靠性测试项目 服务背景 当今的世界技术高度依赖集成电路(IC),其广泛应用在智能家居、机器人、移动电话、汽车及航空航天的各种设备中。其中,整个IC的产业链是由...