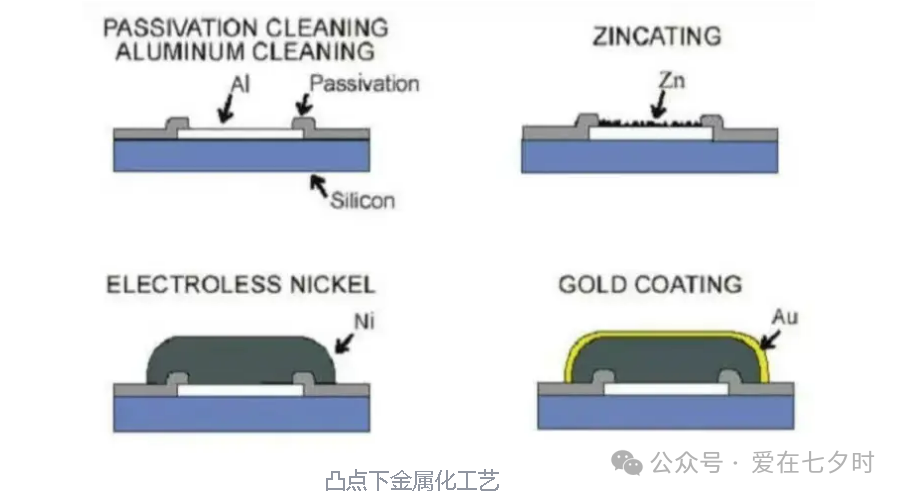

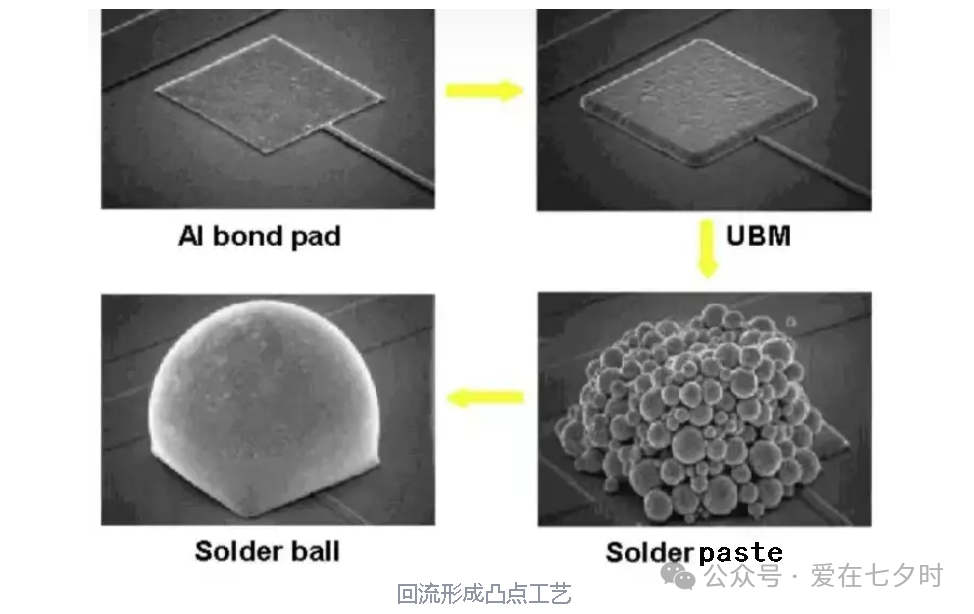

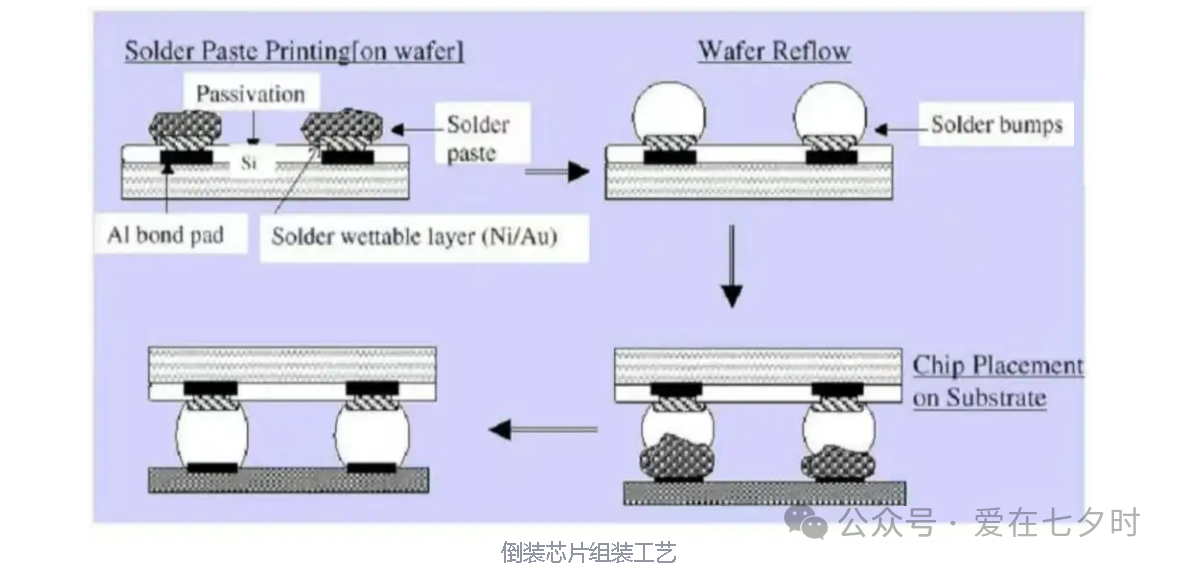

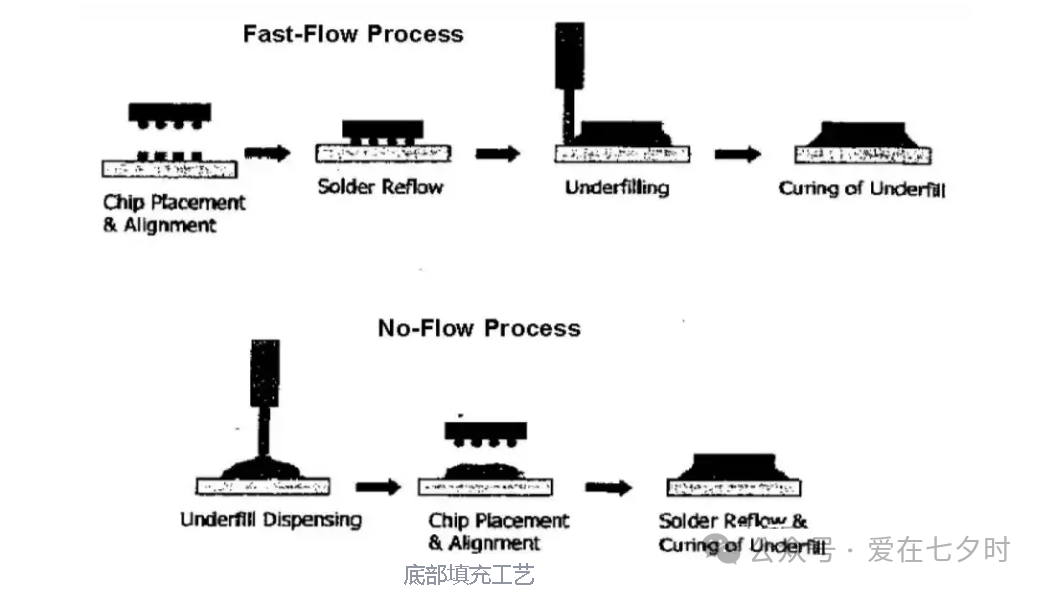

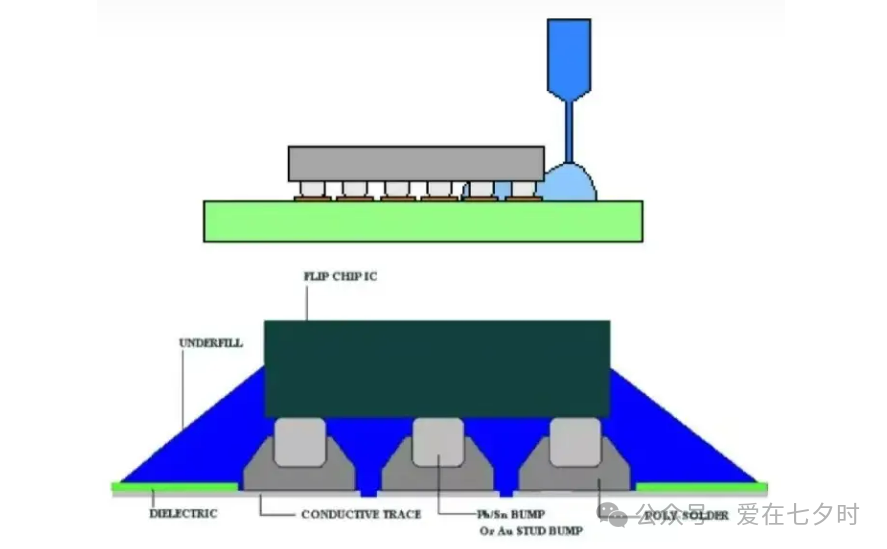

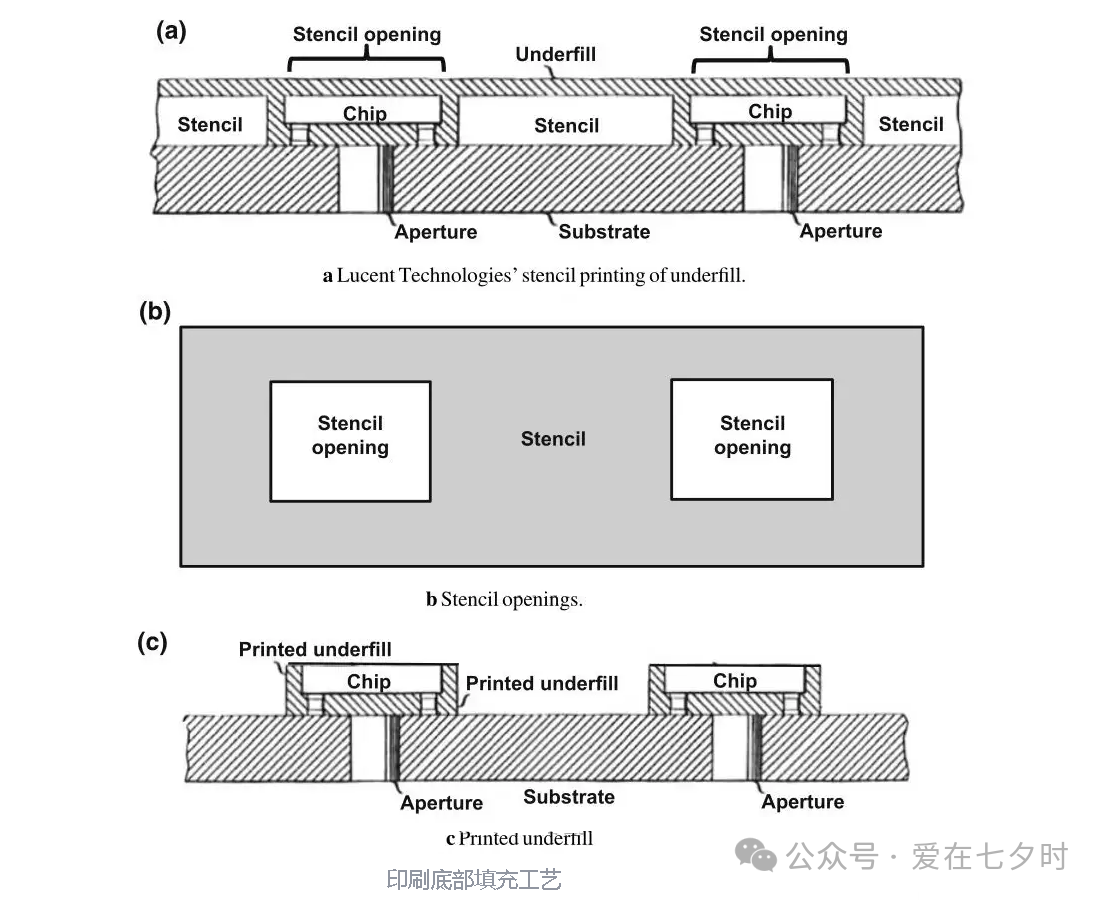

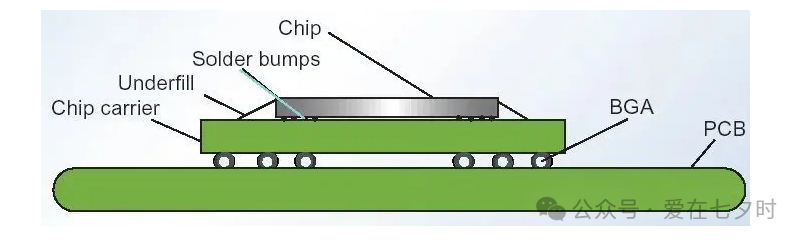

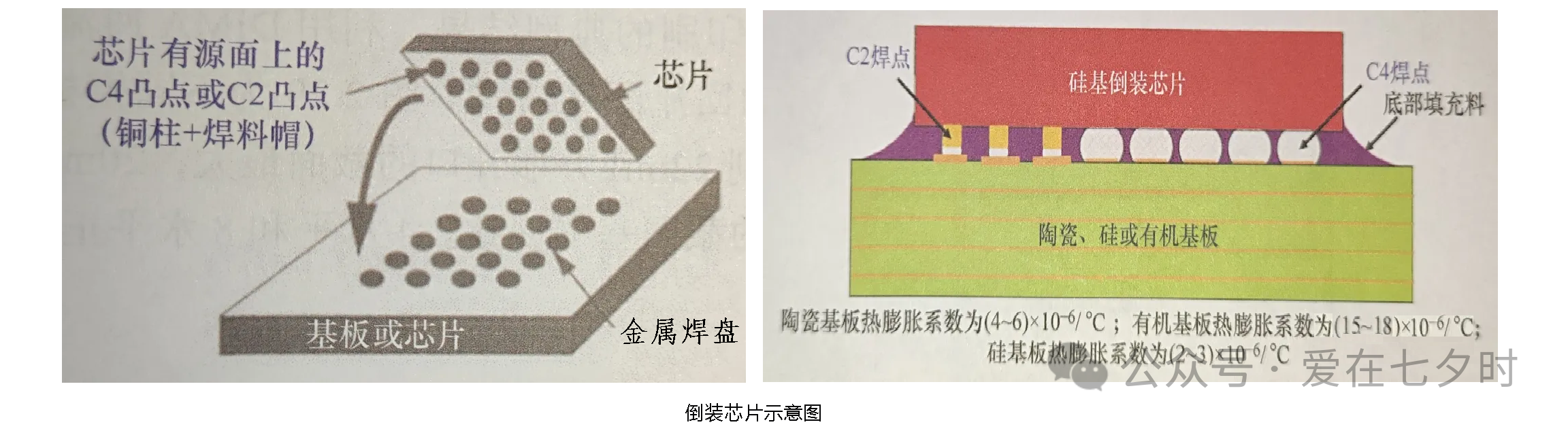

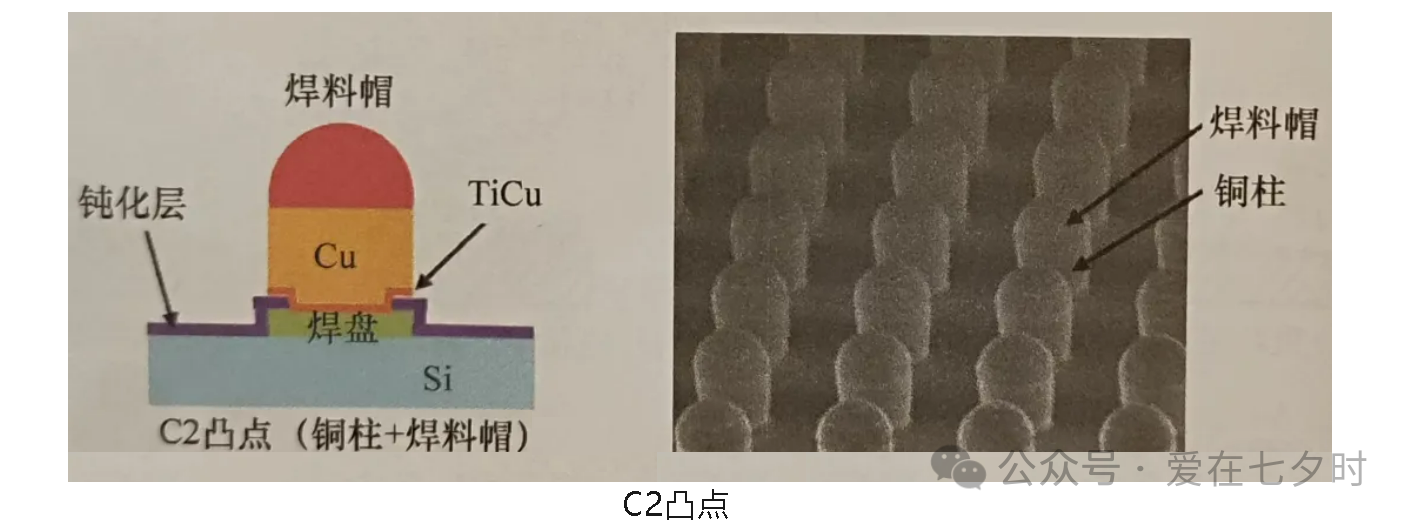

倒装芯片,英文全称:Flip Chip,简称:FC,倒装芯片(FC)封装技术为1960年IBM公司所开发,为了降低成本,提高速度,提高组件可靠性,FC使用在第1层芯片与载板接合封装,封装方式为芯片正面朝下向基板,无需引线键合,形成最短电路,降低电阻;采用金属球连接,缩小了封装尺寸,改善电性表现,解决了BGA为增加引脚数而需扩大体积的困扰。如下图所示。 芯片凸点是倒装芯片(Flip Chip)互联技术中的关键组成部分之一,它替代传统封装中的打线工艺,在芯片与基板之间形成电气连接,并提供良好的散热条件(凸点由铜制作,能把芯片热量通过凸点传递给基板或其他组件来散热)。凸点是实现多种先进封装技术(如倒装芯片(Flip-Chip)、三维堆叠(3D Stacking)、扇出型封装(Fan-Out)等)的基础。  一、倒装芯片(FC)封装技术的发展 30多年前,“倒装芯片”问世。当时为其冠名为“C4”(Controlled Collapse Chip Connection),即“可控熔塌芯片互连”技术。该技术首先采用铜,然后在芯片与基板之间制作高铅焊球。铜或高铅焊球与基板之间的连接通过易熔焊料来实现。此后不久出现了适用于汽车市场的“封帽上的柔性材料(FOC)”;还有人采用Sn封帽,即蒸发扩展易熔面或E3工艺对C4工艺做了进一步的改进。C4工艺尽管实现起来比较昂贵(包括许可证费用与设备的费用等),但它还是为封装技术提供了许多性能与成本优势。与引线键合工艺不同的是,倒装芯片可以批量完成,因此还是比较划算 。 由于新型封装技术和工艺不断以惊人的速度涌现,因此完成具有数千个凸点的芯片设计目前已不存在大的技术障碍小封装技术工程师可以运用新型模拟软件轻易地完成各种电、热、机械与数学模拟。此外,以前一些世界知名公司专为内部使用而设计的专用工具目前已得到广泛应用。为此设计人员完全可以利用这些新工具和新工艺最大限度地提高设计性,最大限度地缩短面市的时间。 无论人们对此抱何种态度,倒装芯片已经开始了一场工艺和封装技术革命,而且由于新材料和新工具的不断涌现使倒装芯片技术经过这么多年的发展以后仍能处于不断的变革之中。为了满足组装工艺和芯片设计不断变化的需求,基片技术领域正在开发新的基板技术,模拟和设计软件也不断更新升级。因此,如何平衡用最新技术设计产品的愿望与以何种适当款式投放产品之间的矛盾就成为一项必须面对的重大挑战。由于受互连网带宽不断变化以及下面列举的一些其它因素的影响,许多设计人员和公司不得不转向倒装芯片技术。 二、倒装芯片(FC)封装技术因素影响 1、减小信号电感——40Gbps(与基板的设计有关); 2、降低电源/接地电感; 3、提高信号的完整性; 4、最佳的热、电性能和最高的可靠性; 5、减少封装的引脚数量; 6、超出引线键合能力,外围或整个面阵设计的高凸点数量; 7、当节距接近200μm设计时允许;S片缩小(受焊点限制的芯片); 8、允许BOAC设计,即在有源电路上进行凸点设计 ; 因此,当前我们常见的芯片凸点就有了C4(Controlled Collapse Chip Connection)凸点和C2(Chip Connection)凸点。在芯片凸点制作中,金属沉积占到全部成本的50%以上。最为常见的金属沉积步骤是UBM(凸点下金属化层)的沉积和凸点本身的沉积,而UBM的沉积通常采用Sputter(溅射),Electroless(化学镀),Plating(电镀)方式实现;凸点本身的成型通常采用电镀,植球,印刷的方式实现。 三、UBM(Under Bump Metallurgy/凸点下金属化层) UBM的作用是提高凸点和芯片表面焊盘的黏附性;防止凸点材料和芯片金属焊盘发生化学反应或相互扩散以保持各自化学稳定性;在凸点成型过程中,UBM可以保护芯片表面免受化学和物理损伤;增强凸点的机械强度等等。 UBM层通常由多层金属薄膜组成,包括粘接层、种子层和阻挡层等,每层都有其特定的功能和作用。UBM层可以根据需要选择不同的材料组合,以适应不同类型的凸点材料,如焊料、铜柱、锡球等。 UBM 的制作主要由物理气相沉积 ( Physical Vapor Deposition,PVD) 工艺完成,蒸镀 ( Evaporation) 或溅射 ( Sputtering) ,蒸镀成本较高, 目前 UBM 多数由溅射工艺制作。  四、 C4凸点(可控塌陷芯片互联)成型技术 芯片C4凸点的电化学沉积或电镀工艺如下图所示,先在整片晶圆表面溅射一层Ti层或TiW层(0.1-0.2um),再溅射一层Cu层(0.3-0.8um),形成UBM,然后在UBM 层上涂覆光刻胶,再使用焊料凸点掩模板进行紫外线曝光,定义凸点的位置和形状,在凸点位置电镀一层 Cu(5um) 作为润湿层,然后电镀焊料。  为了确保凸点的厚度达到目标值,在电镀过程中控制凸点的电镀高度要超出旋涂的光刻层,让凸点形成一个蘑菇状。然后剥离光刻胶,并用过氧化氢或等离子蚀刻去除其他位置多余的 UBM,最后对晶圆进行回流,在表面张力的作用下形成光滑的球型 C4 焊料凸点,如下图。  电镀工艺进行焊料凸点制作的成本效益好、良率高、速度快且凸点密度高。焊料还可以通过焊膏的丝网印刷工艺来实现, 沉积 UBM 后,使用自动漏印板或丝网印刷结合精密漏印板,对特制的焊膏进行刮板印刷得到焊料 图形,并采用回流焊的方式使焊料凸点变为球型。这种方法虽然成本较低,但是所得凸点的形状粗 糙,且无法制作细节距凸点。 五、C2(芯片互联)凸点成型技术 随着IC集成度的提高,芯片引脚数增多,焊盘间距越来越小,芯片上相邻的C4焊球容易发生桥接短路的现象。因此使用带焊料帽的铜柱(C2凸点)结构替代C4凸点。C2凸点的的制作过程基本与C4凸点一致,只是在下图第4步中直接电镀铜柱(而不是像C4凸点成型第4步中电镀铜层只是作为湿润层),形成铜柱后再电镀焊料再回流得到C2凸点。  由于如下图中的C2凸点主要由Cu柱构成,相比C4凸点的焊料而言,有更好的热导率和电阻率,所以热电性能也更好。  六、倒装芯片(FC)封装工艺 其实,倒装芯片(FC)封装工艺主要包括四步:凸点金属化 、凸点制造、晶片组装和底部填充等。

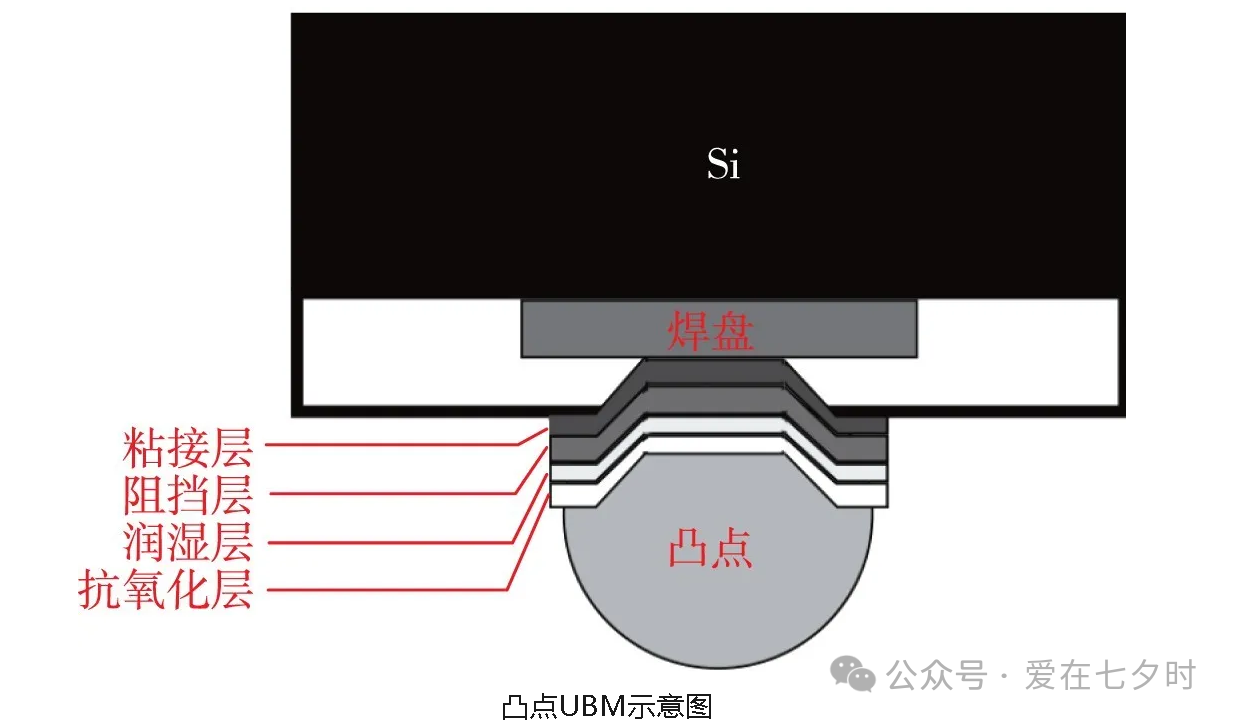

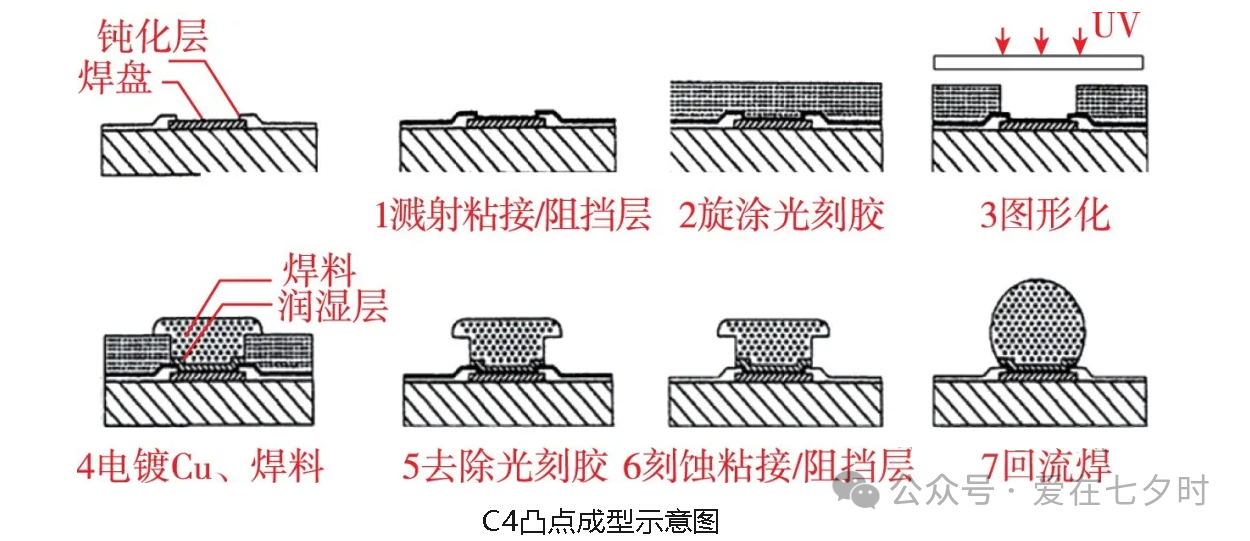

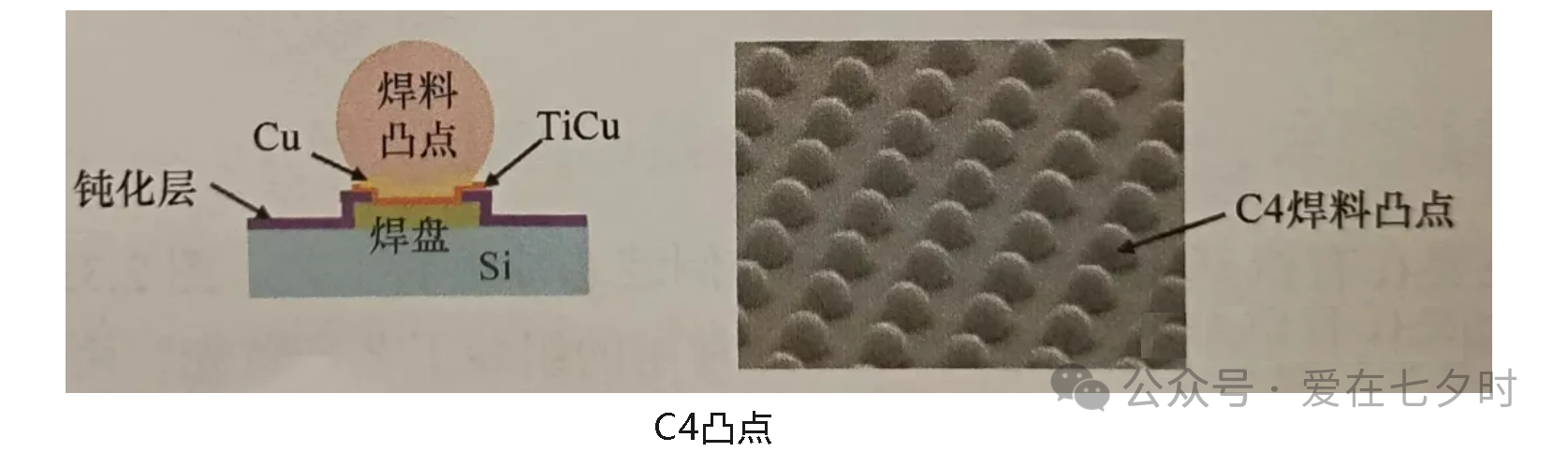

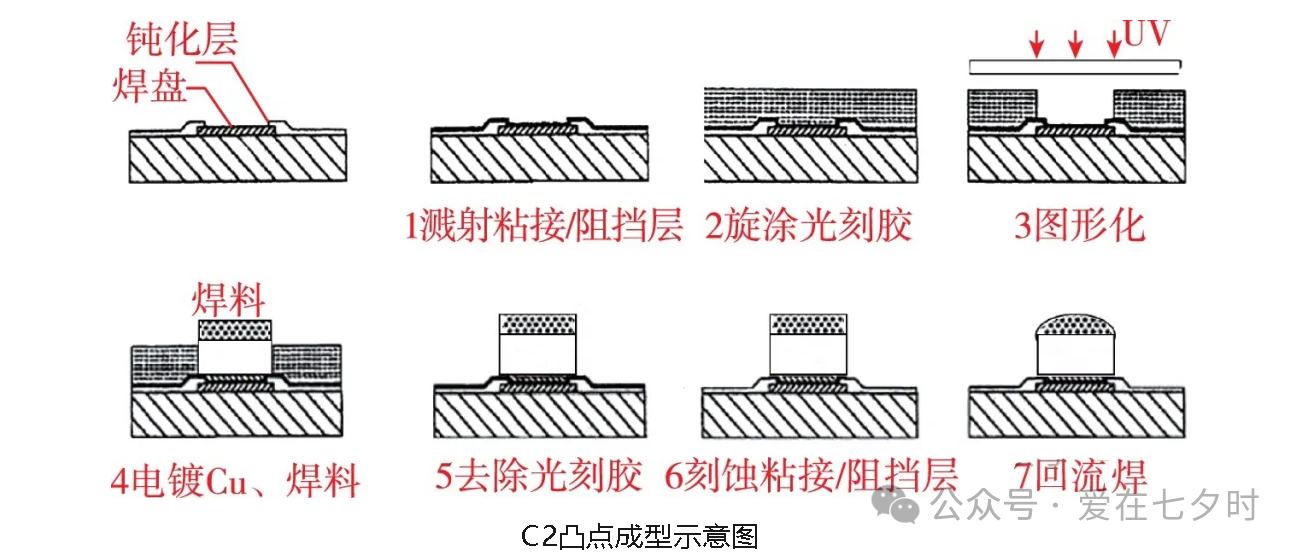

|