|

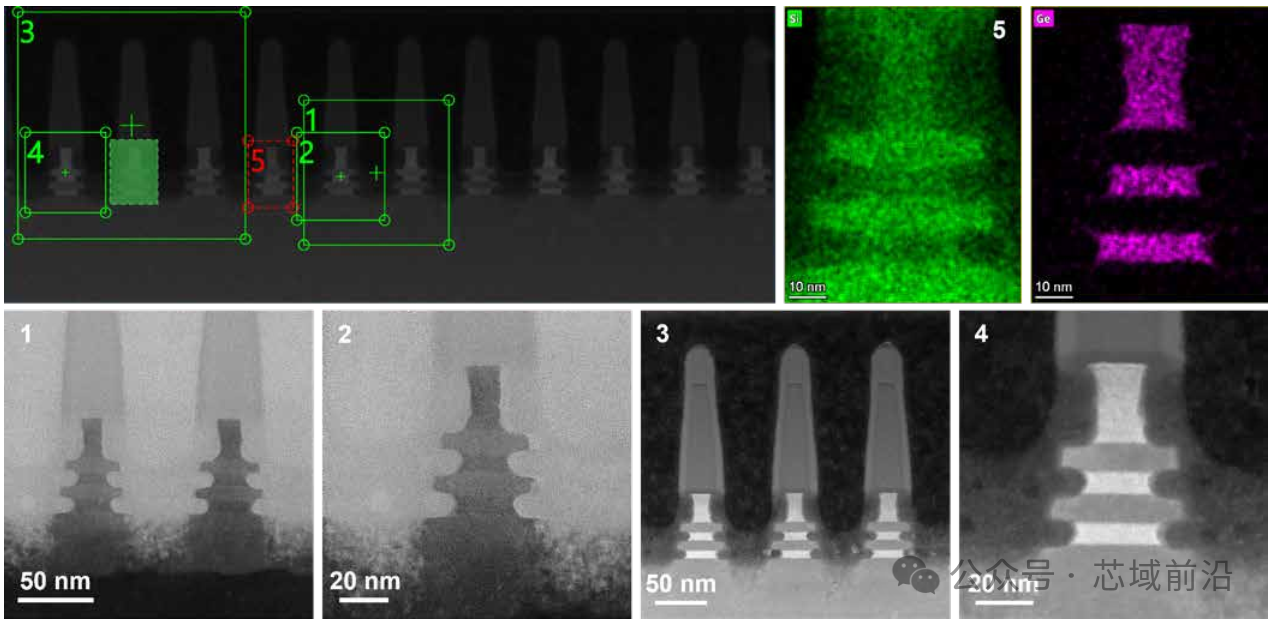

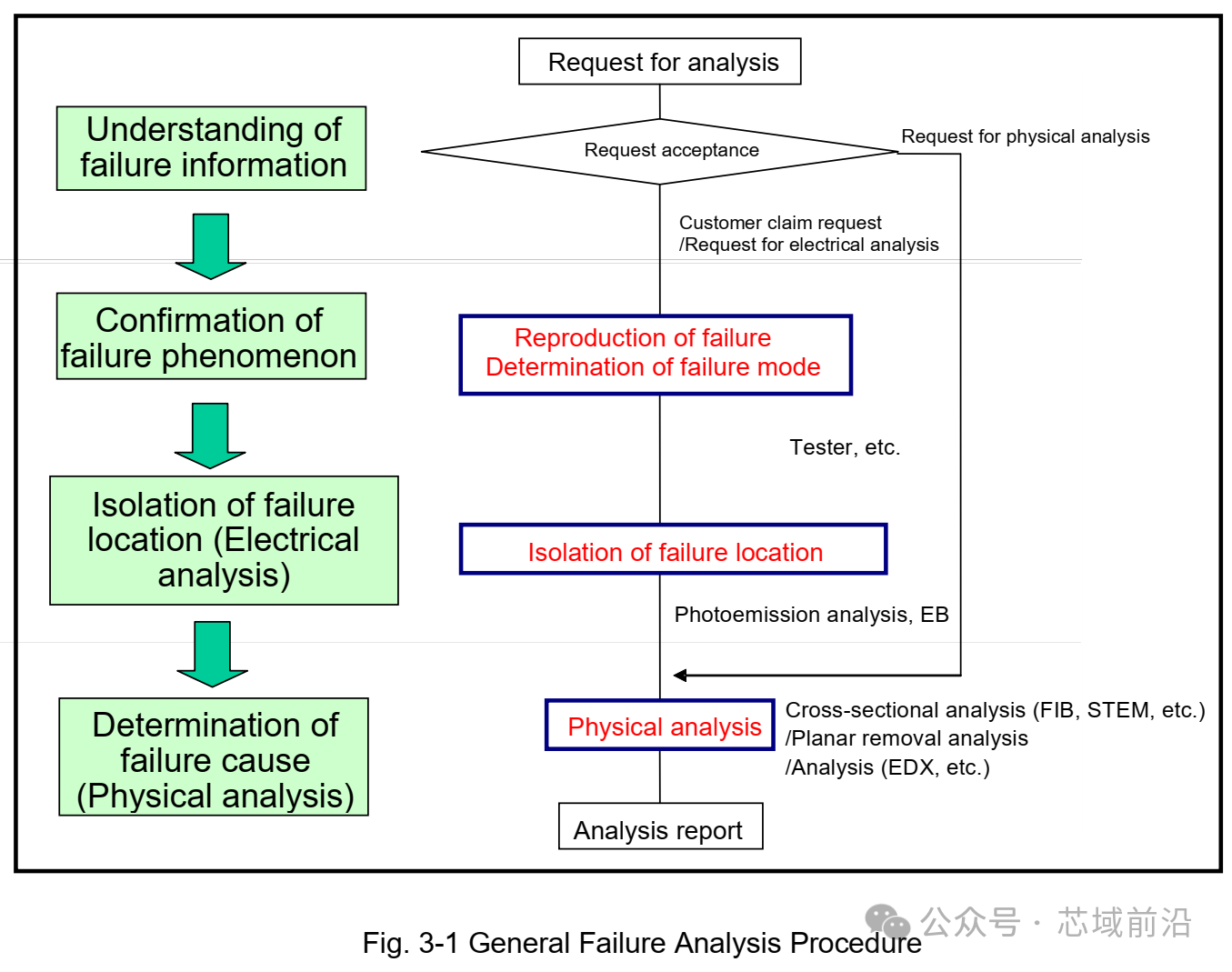

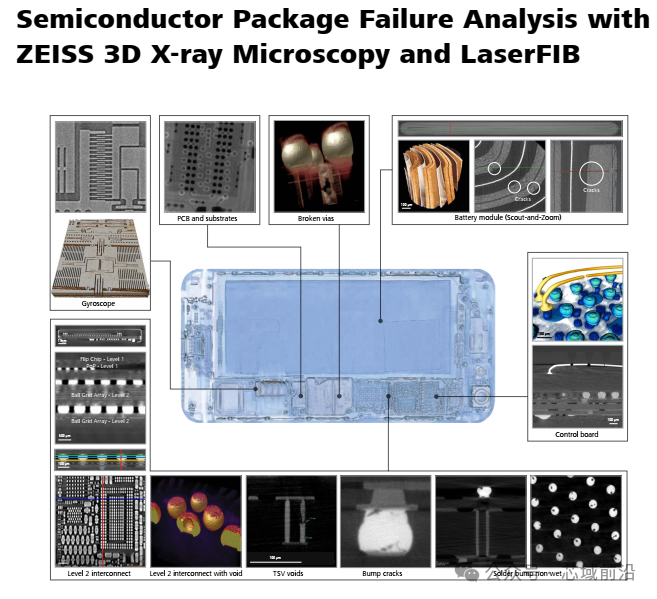

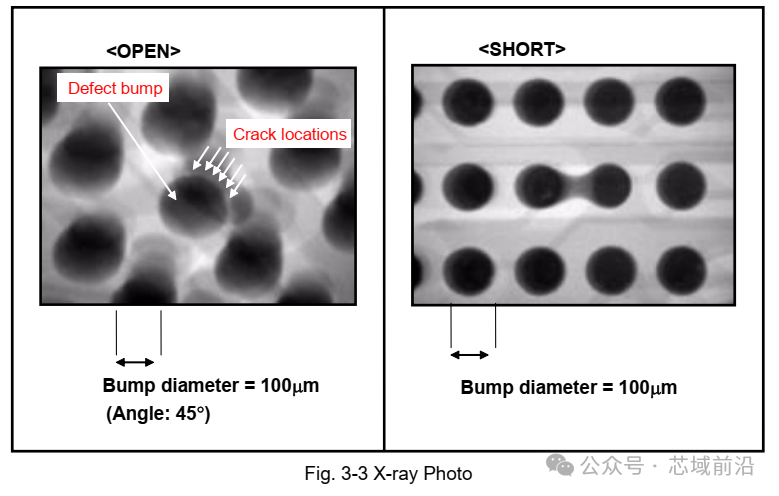

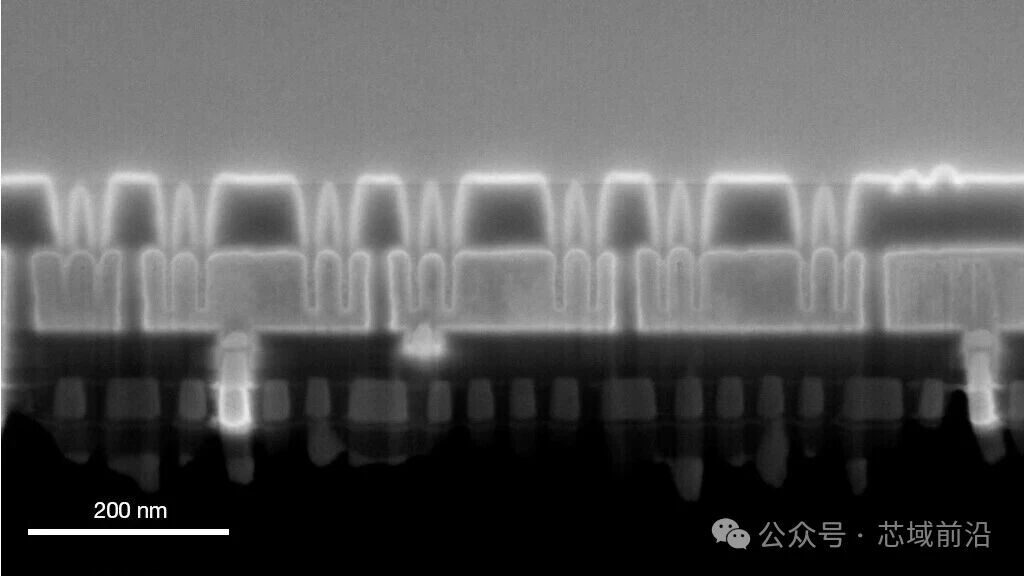

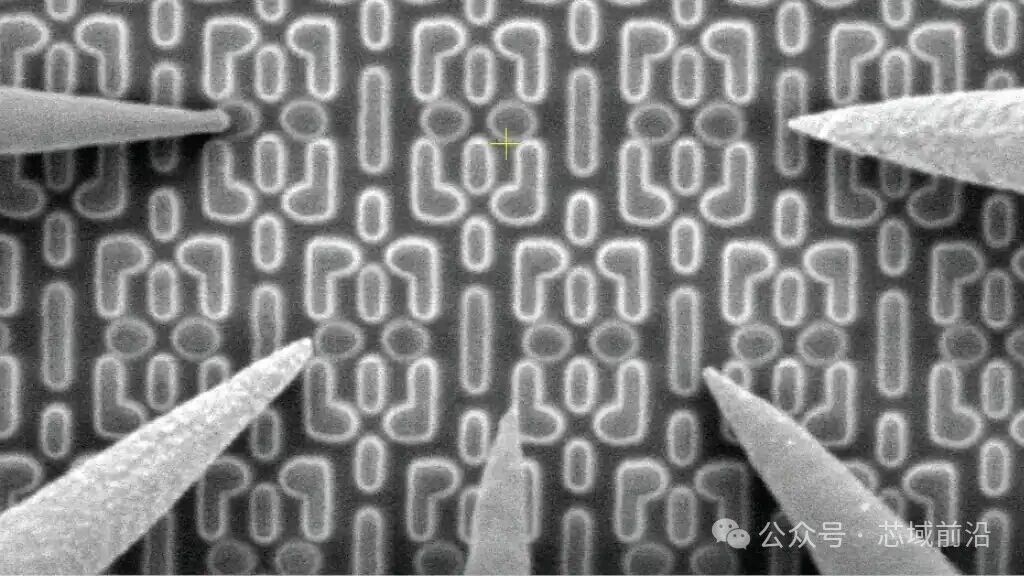

为什么先进芯片越难做,越离不开FA?半导体失效分析全景图 很多人第一次听到半导体失效分析FA(Failure Analysis),脑子里会自动浮现一个画面:工程师拿着工具,把坏芯片切开、磨开、看一看,然后找出哪里烧了、裂了、短了。 这个画面不算错,但只说对了最表层的一小部分。 真正的FA,更像一场“芯片法医”式破案。 它不是单纯证明“这颗芯片坏了”,而是要回答三个更难的问题: 坏在哪里、为什么会坏、怎样才能不再坏。 Intel 公开资料很早就指出,FA直接关系到产品量产爬坡、缺陷率和上市节奏; Sony 的失效分析资料则用一个非常形象的比喻来说明今天做FA有多难:在高集成芯片里,把失效位置缩到约1微米量级,难度就像在“一个棒球场大小、八层楼高的建筑里找一枚掉落的硬币”。 也正因为如此,FA从来不是“拿到坏样就上刀”。 相反,优秀的FA流程最看重两件事: 第一,尽量保留失效证据;第二,尽量在不破坏样品的情况下,把故障范围一步步缩小。 从收集失效背景、复现故障现象、判定失效模式,到电性定位、无损成像、局部开盖、逐层去层、截面观察、材料成分分析,最后再回到设计、工艺、封装、可靠性和测试环节去闭环,这才是现代半导体FA真正的样子。 文章篇幅原因,作者分享了几篇相关资料,感兴趣的小伙伴可以在公众号【芯域前沿】对话框输入:306,获取资料研读。一张表先看懂:FA到底在“干什么”

这张表综合了 Sony 的FA流程资料、SGS 的方法分类、Jim Colvin 的FA教程,以及 Thermo Fisher、Bruker 的器件分析资料。  01FA不是“把芯片切开”,而是先把问题问对 一颗芯片失效,表面上可能只是“功耗偏高”“不启动”“某个接口失灵”或者“通过老化后突然漏电”。 但在FA工程师眼里,这些都只是外在表现。 真正重要的是:它是稳定漏电还是偶发异常,是热相关还是时序相关 ,是电压一升就坏还是特定工作模式才坏。 Jim Colvin 的教程里提到,I-V特性实际上是选择后续分析路线的重要依据:线性响应更适合热方法,非线性问题往往更容易在光发射类方法里出现信号。 也就是说,FA第一步不是“拆”,而是“先把故障性格摸清楚”。 Sony 给出的通用流程也非常典型:先理解失效信息,再确认并复现失效现象,接着判定失效模式,之后才进入失效位置隔离,最后再做物理分析并形成报告。 这个顺序看似啰嗦,其实非常关键——因为一旦你在没有定位的情况下盲目去层、抛光或切截面,等于在一个本来就极小的嫌疑区域里又主动“抹掉现场”。 FA最怕的,不是找不到,而是把本来能找到的证据亲手破坏掉。  02先不拆:无损方法是FA里最像“医学影像科”的部分 现代FA的一个核心原则是: 能不破坏,就先不破坏。 因为封装一旦被打开、金属一旦被去掉、介质层一旦被刻蚀,原始失效状态就可能改变。所以很多分析会先从无损方法入手。 X-ray与3D XRM 最常见的一类是 X-ray(X射线)与 3D XRM(X-ray Microscopy,X射线显微成像)。 它们特别适合看封装级问题,比如焊线断裂、焊线偏移、焊点空洞、die attach(芯片贴装)异常、内部裂纹等。 Matsusada 的资料提到,在树脂封装后,细至20到30微米量级的焊线已经无法通过肉眼直接观察,只能依赖高分辨率X射线系统; ZEISS 的封装FA资料则说明,3D X-ray可以把一系列二维投影重建成三维体数据,实现数字化“虚拟切片”,在不真正切开器件的情况下查看内部结构。 C-SAM 第二类是 C-SAM(Confocal Scanning Acoustic Microscopy,共焦扫描声学显微镜)。 如果说 X-ray 更像“透视骨骼”,那 C-SAM 更像在找“层间脱粘”。 它利用声波在不同材料界面的反射差异,去识别封装内部的分层、空洞、die crack(芯片裂纹)、underfill(底部填充)空洞、bump(凸点)异常等问题。 Sage 的说明很直接:C-SAM 是一种非破坏、非侵入式方法,尤其适合在进入破坏性步骤之前,先确认这些界面缺陷是否原本就存在。 对封装分析来说,这一步很重要,因为它可以帮助区分“产品本来就坏了”与“样品在后续处理里被弄坏了”。 LIT 第三类是LIT(Lock-In Thermography,锁相热成像)。 Fraunhofer IISB 的资料显示,它通过给被测器件施加周期性激励,再用红外相机测量热响应的幅值和相位图,从而锁定电活性缺陷产生的热点。 短路、ESD(Electrostatic Discharge,静电放电)损伤、氧化层损伤、边缘终端缺陷、导电污染等,都可能在热图里露出马脚。 它的强项不是“看见金属长什么样”,而是“告诉你哪里在异常耗能”。在很多案例里,这一步恰恰是后续FIB截面的导航图。  03给芯片“通上电”追凶:EFA是把坏点缩到足够小的关键一步 如果无损方法解决的是“里面可能哪里有问题”,那么 EFA(Electrical Failure Analysis,电性失效分析)解决的就是“哪一块区域真的在电学上不正常”。 EMMI 其中最经典的方法之一,是 EMMI(Emission Microscope,发光显微镜), 也常被称作 PEM(Photon Emission Microscopy,光子发射显微镜)。 它的原理并不神秘:当器件内部某些缺陷区域在偏压下发生电子—空穴复合、结击穿或局部高场效应时,会发出极其微弱的光; EMMI 用高灵敏度探测器把这种“失效微光”抓出来,再叠加到版图或显微图上,工程师就能看到热点在哪里。 iST 和 MA-tek 的公开说明都指出,EMMI 对 gate oxide(栅氧)缺陷、ESD失效、latch-up(闩锁)、junction leakage(结漏电)等特别有用,但对纯欧姆短路、金属短路,或者被大面积金属遮挡的埋藏点,效果可能有限。 OBIRCH 另一把“电学手电筒”是 OBIRCH(Optical Beam Induced Resistance Change,光束诱导电阻变化)。 iST 的定义非常清楚:它在器件功能测试期间,用激光从正面或背面扫描芯片,激光造成的局部温升会让异常区域的电阻变化比正常区域更明显,系统再把这种变化转成图像,定位可疑缺陷。 说得更直白一点,EMMI擅长“找会发光的异常”,OBIRCH更擅长“找受热后电阻反应异常的地方”。 很多不太发光、但有局部高阻、微短、漏电路径的故障,用 OBIRCH 反而更容易抓住。 为什么很多先进器件喜欢从背面做这些分析? Springer 的经典章节给了答案: 硅对红外光有相对透明性 ,因此背面访问在不少情况下更容易接近电活性区域,尤其当正面被多层金属和复杂互连遮挡时,这一点格外重要。 也正因为工艺越来越先进、金属层越来越复杂,背面分析的重要性这几年只会越来越高,不会下降。  04真正剖开真相:PFA的本质,是把“怀疑”变成“证据” 当故障位置已经被缩小到足够小的范围,PFA(Physical Failure Analysis,物理失效分析)才真正登场。 这个阶段才是很多人想象中的“把芯片拆开看”。 但严格来说,它不是粗暴拆解,而是 带着定位信息的精密手术 。 开盖与逐层去层 PFA通常从 decap(开盖)开始。 Sony 的资料提到,针对常见树脂封装,基本思路是通过化学方法去除封装树脂,暴露芯片表面。 拿到芯片表面后,很多故障还看不见,因为真正的问题可能埋在多层互连和介质下面,于是就要做 delayering(逐层去层)。 这一步是把金属层和层间绝缘层一层一层拿掉,尽量保持表面平整、层次清楚。 Thermo Fisher 的页面进一步说明,先进的去层强调系统性、平坦性和端点控制,否则表面一旦起伏过大,原本极小的缺陷就会被“地形噪声”淹没。 FIB 接下来,FIB(Focused Ion Beam,聚焦离子束)往往是最关键的工具之一。 Sony 的说明显示,FIB通常以镓离子束为主,能把离子束聚焦到数百纳米量级,对指定区域做亚微米级蚀刻;它不只可以切截面,还能沉积导电膜或绝缘膜,甚至用于局部电路修补。 Thermo Fisher 也强调,FIB适合对先进逻辑器件做选择性截面,配合 SEM(Scanning Electron Microscopy,扫描电子显微镜)可以快速找到表面和近表面电学故障的物理根因。 通俗地说,FIB就是那把“只切你怀疑那一小刀”的手术刀。 TEM与EDX/EDS 如果还要继续往纳米甚至原子尺度深挖,就轮到 TEM(Transmission Electron Microscopy,透射电子显微镜)和 EDX/EDS(Energy Dispersive X-ray Spectroscopy,能量色散X射线谱)出场了。 Sony 资料写得很直接:先用 FIB 从目标区域切出超薄样片,再把它装到 TEM holder(透射电镜样品杆)里做细节观察; NIST 也指出,TEM 和 STEM(Scanning Transmission Electron Microscopy,扫描透射电子显微镜)已经是行业里识别结构与形貌特征的重要手段,只是随着结构越来越复杂,传统二维观察也面临挑战。 至于 EDX/EDS,本质上是在显微观察基础上再加一层“元素地图”,Bruker 的说明强调它特别适合做快速、可靠的半导体材料元素分析。 于是你不仅能看到“这里裂了”,还能进一步问: o 这里是不是混进了异常元素? o 阻挡层是不是缺了? o 金属组成是不是不对? 这时候,FA才真正从“看见异常”走到“证明异常”。  05最难的不是“看到坏点”,而是把坏点讲成一个完整故事 做FA的人都知道,最危险的误区,就是迷信某一种工具。 看到了热点,不等于知道根因;看到了裂纹,不等于知道裂纹为什么会在那里;检测到某个元素异常,也不等于已经证明确实是它导致失效。 Jim Colvin 在教程结尾特别强调, 不同FA数据之间的交叉验证非常重要 ,因为只有把电学、热学、光学、结构和材料证据互相对上,结论才真正站得住。 这也是为什么成熟的FA报告,通常不是“某图显示某点异常,所以结案”,而是会给出完整链条: 样品在什么条件下失效、失效是否可复现、无损手段把范围缩到哪里、EFA把热点或异常响应定位到哪一层附近、PFA在什么截面看到什么结构异常、成分分析发现了什么材料证据、这些证据如何回指到设计、工艺、封装或可靠性应力。 真正优秀的FA,最后不是产出一张漂亮的显微照片,而是产出一个经得起质疑的因果链。 而在先进制程与先进封装时代,这条因果链正在变得更难。 NIST 关于 TREM(Time-resolved Emission Microscopy,时间分辨发光显微)项目的公开说明指出,随着晶体管尺寸继续缩小、供电电压降低,发光信号变得更弱,而且一个衍射极限光斑内可能同时混入大量晶体管信号; 另一方面,NIST 也在推进面向复杂器件的电子断层与AI重建方法,试图让TEM/STEM从“看二维切片”升级到更可靠的三维定量表征。 ZEISS 的封装资料则说明,先进封装的层次复杂度已经在持续抬高无损定位和后续PFA的门槛。 换句话说,未来的FA不会减少工具,只会更强调 多模态联合、自动化、三维化和AI辅助解释 。  06结语 半导体失效分析FA(Failure Analysis,失效分析)真正迷人的地方,就在于它把看似冰冷的芯片,变成了一桩桩需要证据、逻辑与耐心的“技术案件”。 o 一颗异常漏电的芯片,背后可能是栅氧击穿; o 一个突然飙高的功耗,背后可能是局部短路; o 一个封装可靠性失效,背后可能是界面分层、焊点空洞或应力裂纹。 FA的价值,不只是找出“哪儿坏了”,更是把这次失败变成下一次设计、制造、封装和测试优化的起点。对今天的半导体行业来说,FA不是生产线末端的“补救动作”,而是贯穿研发、量产、可靠性与品质闭环的一种核心能力。 |