[芯片制造] 芯片早夭筛查(Early Failure Screening) 日期:2025-09-17 20:37:34 点击:335 好评:0

[芯片制造] 芯片早夭筛查(Early Failure Screening) 日期:2025-09-17 20:37:34 点击:335 好评:0

芯片的早夭(Infant Mortality),也称为早期失效,是电子产品失效率浴盆曲线(Bathtub Curve)的第一个阶段。这个阶段的失效主要由制造过程中引入的潜在缺陷(Latent Defects)导致,这些缺...

[芯片制造] 一文读懂芯片封装 日期:2025-08-25 19:53:00 点击:323 好评:0

[芯片制造] 一文读懂芯片封装 日期:2025-08-25 19:53:00 点击:323 好评:0

芯片封装 在摩尔定律趋近物理极限、功率器件制程仍停留在百纳米节点的产业背景下,芯片尺寸缩小与性能提升之间的矛盾愈发尖锐。封装环节被推到技术演进的核心:材料需同时满足...

[芯片制造] EMC常见问题整改的流程及经验总结 日期:2025-08-14 19:06:00 点击:350 好评:0

[芯片制造] EMC常见问题整改的流程及经验总结 日期:2025-08-14 19:06:00 点击:350 好评:0

EMC主要是通过测试产品在电磁方面的干扰大小和抗干扰能力的综合评定,是产品在质量安全认证重要的指标之一。很多产品在做产品安全认证时都会遇到产品测试不合格的情况,尤其是...

[芯片制造] 芯片的制造方法--前道工序 Frontend 日期:2025-08-12 19:39:00 点击:352 好评:0

[芯片制造] 芯片的制造方法--前道工序 Frontend 日期:2025-08-12 19:39:00 点击:352 好评:0

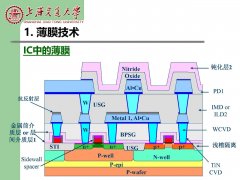

芯片制造的前道工序(Frontend of Line, FEOL)是芯片生产的核心阶段,主要在硅晶圆上构建晶体管、二极管等基础半导体器件,并形成初步的电路结构。这一阶段对工艺精度、材料控制和设...

[芯片制造] 上交大-教你怎样造芯片(100页PPT 收藏) 日期:2025-08-11 22:24:43 点击:227 好评:0

[芯片制造] 上交大-教你怎样造芯片(100页PPT 收藏) 日期:2025-08-11 22:24:43 点击:227 好评:0

...

[芯片制造] 一文了解芯片设计、制造及封装全流程 日期:2025-08-11 19:37:00 点击:301 好评:0

[芯片制造] 一文了解芯片设计、制造及封装全流程 日期:2025-08-11 19:37:00 点击:301 好评:0

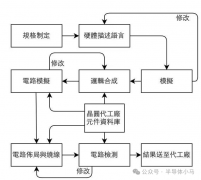

大家都是电子行业的人,对芯片,对各种封装都了解不少,但是你知道一个芯片是怎样设计出来的么?你又知道设计出来的芯片是怎么生产出来的么?看完这篇文章你就有大概的了解。...

[芯片制造] 55页PPT,看懂芯片半导体的制作流程! 日期:2025-08-10 17:30:40 点击:264 好评:6

[芯片制造] 55页PPT,看懂芯片半导体的制作流程! 日期:2025-08-10 17:30:40 点击:264 好评:6

...

[芯片制造] 芯片Layout中的Guard Ring是什么? 日期:2025-08-07 17:04:00 点击:369 好评:0

[芯片制造] 芯片Layout中的Guard Ring是什么? 日期:2025-08-07 17:04:00 点击:369 好评:0

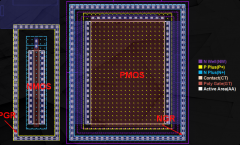

在芯片设计中,Guard Ring(保护环) 是一种环绕在敏感电路或器件(如模拟电路、高精度器件、存储器单元、I/O驱动器等)周围的版图结构,形成关键的隔离带。它的核心使命是 提高电...

[芯片制造] 面向前端设计的DFT基础介绍—Tessent MBIST 日期:2025-08-05 20:38:00 点击:468 好评:0

[芯片制造] 面向前端设计的DFT基础介绍—Tessent MBIST 日期:2025-08-05 20:38:00 点击:468 好评:0

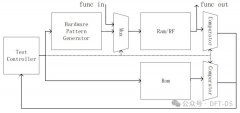

前言芯片由MPW试产进入量产阶段的时候,DFT可测性设计是前后端设计者都无法绕过的必修课。DFT的设计,既属于芯片功能设计的范畴,又对后端的设计流程有显性的影响。 前端设计者需...

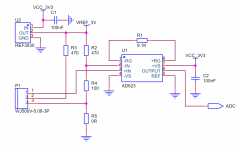

[芯片制造] PT100测温电路测温异常,一个原理图一堆错误 日期:2025-07-25 19:23:00 点击:223 好评:2

[芯片制造] PT100测温电路测温异常,一个原理图一堆错误 日期:2025-07-25 19:23:00 点击:223 好评:2

这期的电路来自隔壁群群友,电路图为群友的一个离职的同事画的,算是接手的别人的项目,电路为一个PT100的测温电路,也算是一个比较经典的错误,分享给大家。由于电路图来自群...