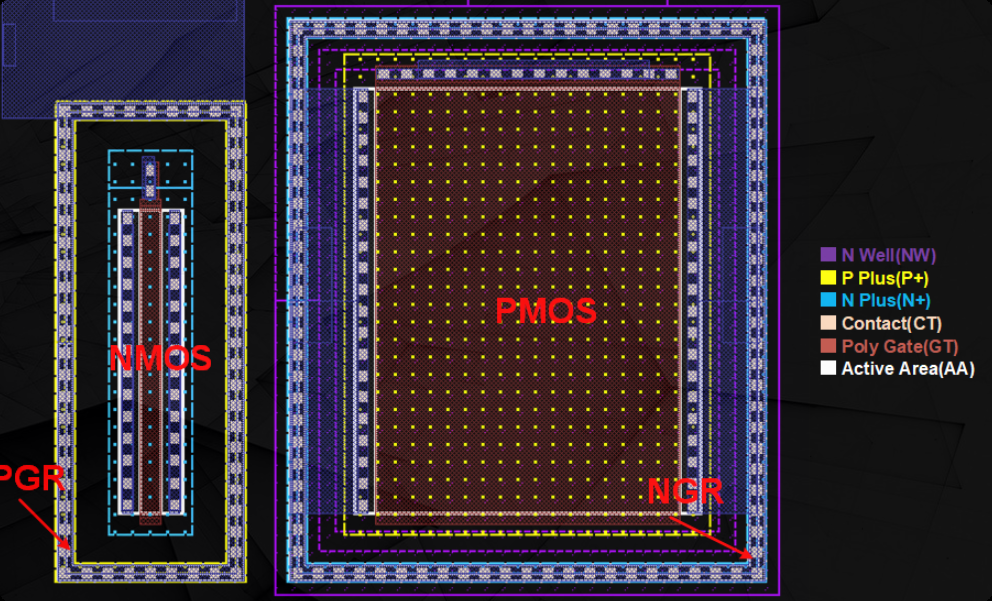

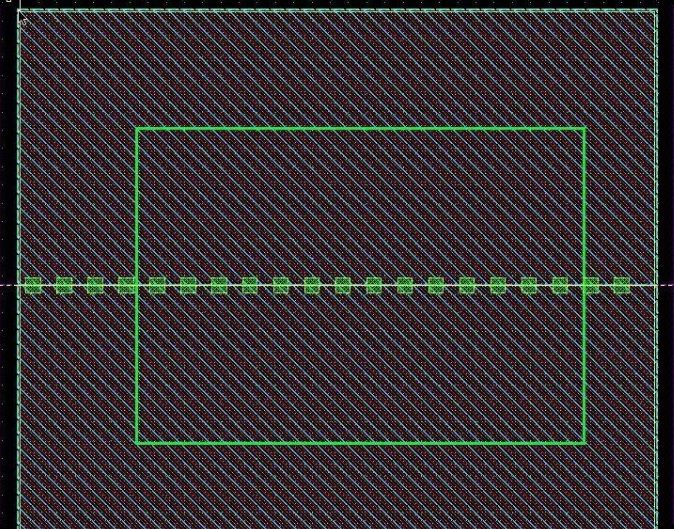

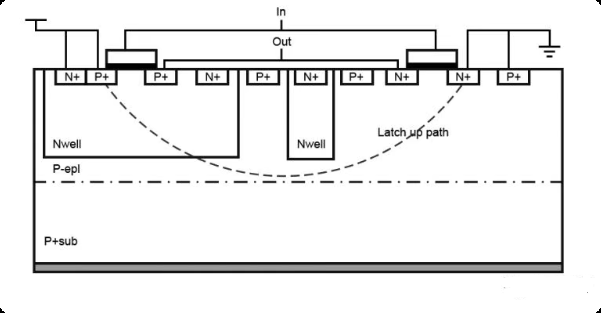

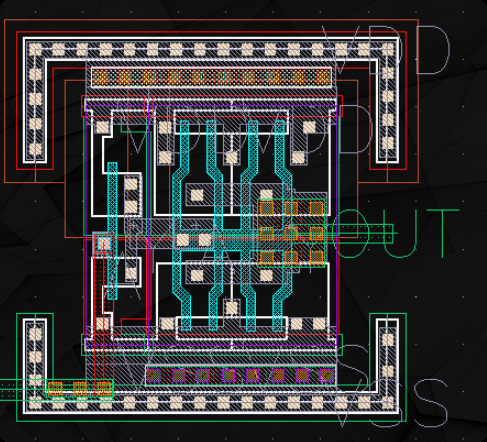

在芯片设计中,Guard Ring(保护环) 是一种环绕在敏感电路或器件(如模拟电路、高精度器件、存储器单元、I/O驱动器等)周围的版图结构,形成关键的“隔离带”。它的核心使命是提高电路的可靠性、性能和抗干扰能力,是复杂芯片(尤其是混合信号芯片、高可靠性芯片)成功量产的关键因素之一。 Guard Ring的物理构成 Guard Ring并非单一结构,而是由多个精心设计的物理组件协同构成: 1.衬底接触环 采用高掺杂的P+区域(P型衬底)或N+区域(N型衬底/深N阱)。其核心作用是提供到半导体衬底的低阻连接。它能有效收集衬底中不需要的少数载流子,防止其干扰被保护电路,稳定衬底电位,减少衬底噪声耦合,并为潜在寄生电流提供泄放路径。 2.阱接触环 采用高掺杂的N+区域(N阱)或P+区域(P阱)。它提供到阱的低阻连接点,稳定阱电位并收集阱中产生的少数载流子。在双阱工艺中,N阱接触环本身就能阻挡衬底中的少数载流子(空穴)进入N阱。  3.隔离结构 通常指浅沟槽隔离或深沟槽隔离。它在物理上分隔保护环内外的区域,阻止表面漏电流路径,增加载流子从外部扩散进入保护区域的难度,是防止闩锁效应的关键物理屏障。 4.连接线 通过通孔和金属层将衬底接触环和阱接触环连接到指定电位(VSS或VDD)。确保这些连接具有极低的电阻至关重要。 Guard Ring的核心作用 Guard Ring通过其物理结构实现多重关键保护功能: 1.防止闩锁效应 这是Guard Ring最核心的作用。闩锁效应由芯片内部寄生的PNPN结构意外触发引发,可导致大电流、功能失效甚至芯片烧毁。Guard Ring通过提供低阻的阱和衬底接触,有效收集触发闩锁的寄生载流子,在其达到触发浓度前将其泄放。同时,隔离结构增加了载流子横向流动的阻力。它对包含NMOS和PMOS相邻放置的电路(如CMOS反相器、I/O驱动器)的保护尤为关键。  2.抑制衬底噪声耦合 芯片上不同模块(尤其是数字模块与敏感的模拟/射频模块)工作时产生的噪声会通过公共硅衬底传播。连接到干净VSS的衬底接触环作为一个低阻抗的“汇”,能吸收和分流试图进入保护区域的衬底噪声电流,为被保护电路提供局部的“安静地”,显著降低噪声干扰。 3.阻挡少数载流子注入 芯片某些区域(如开关状态的NMOS源/漏、反向偏置的PN结)可能向衬底注入少数载流子(电子或空穴)。这些载流子扩散到敏感区域(高阻节点、存储节点、精密基准源)会引发漏电流、电压偏移或数据错误。Guard Ring(尤其是反向偏置的阱接触环,如N阱环接VDD阻挡空穴)能收集这些扩散载流子,阻止其到达敏感区域。 4.提高器件隔离度与可靠性 在需要高隔离度的应用(如RF电路、混合信号电路)中,Guard Ring有助于减少相邻器件间通过衬底的串扰。通过综合防止闩锁、减少噪声干扰和漏电流,Guard Ring显著提升了被保护电路的长期工作可靠性和稳定性。 设计与实现考量 Guard Ring的设计需结合具体工艺和电路需求: 必要性:为MOS器件提供衬底/阱电位(Bulk端)的Guard Ring是必不可少的。用于隔离噪声或防止Latch-up的Guard Ring则需评估实际需求(是否存在噪声源或对噪声敏感)。 结构选择:根据保护对象(PMOS/NMOS/DNW器件)选择对应的NWring、PSUBring或DNWring结构。其版图实现需严格遵循特定工艺的设计规则(Design Rule),例如有源区(AA/OD)与注入层(SP/PP/SN/NP)的包围关系、接触孔(CT/CONT)的尺寸和间距、金属层(M1)的连接等。  增强防护:有时会采用双层Guard Ring结构,以进一步降低阱/衬底的寄生电阻压降,增强隔离效果,更有效地降低Latch-up风险。 面积权衡:添加Guard Ring必然增加芯片面积。设计时必须在防护效果和成本(面积)之间进行仔细权衡。 Guard Ring是芯片版图设计中基础而关键的防护结构。其本质是通过在敏感电路周围精确构建阱接触环、衬底接触环和隔离结构,并将它们连接到合适的电源/地网络,共同形成一个高效的载流子收集阱和噪声隔离带。它从根本上防止了致命的闩锁效应,有效抑制了衬底噪声耦合,并阻挡了有害的少数载流子注入,从而极大提升了芯片的鲁棒性、性能和可靠性。 |