[可靠性测试] 半导体芯片老化与可靠性测试项目及方法 日期:2026-03-09 22:45:29 点击:188 好评:0

[可靠性测试] 半导体芯片老化与可靠性测试项目及方法 日期:2026-03-09 22:45:29 点击:188 好评:0

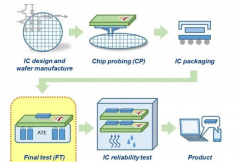

芯片可靠性测试主要分为环境试验和寿命试验两个大项,可靠性测试是确保芯片在实际应用中能够稳定运行和长期可靠的关键步骤。一般来说,可靠度是产品以标准技术条件下,在特定...

[可靠性测试] 芯片工作寿命老化测试 (HTOL):芯片可靠性的"高 日期:2026-03-09 20:34:00 点击:194 好评:0

[可靠性测试] 芯片工作寿命老化测试 (HTOL):芯片可靠性的"高 日期:2026-03-09 20:34:00 点击:194 好评:0

在指甲盖大小的芯片上,承载着数亿晶体管的精密城市这是半导体技术的奇迹,也是现代科技的核心命脉。从智能手机到自动驾驶,从人工智能到航空航天,芯片的可靠性直接决定了这...

[测试工程] 半导体制程测试分析利器:透射电子显微镜(T 日期:2026-03-04 22:57:00 点击:121 好评:0

[测试工程] 半导体制程测试分析利器:透射电子显微镜(T 日期:2026-03-04 22:57:00 点击:121 好评:0

一、TEM 简介 1.TEM 的加速电压远高于扫描电子显微镜(SEM); 2.中压电镜加速电压为 200-500 kV,相比低压电镜(80-120 kV)具备更优的透射效果和分辨率,超高压电镜加速电压可达 500 kV-...

[可靠性测试] 可靠性基础知识 日期:2026-03-04 20:37:00 点击:131 好评:0

[可靠性测试] 可靠性基础知识 日期:2026-03-04 20:37:00 点击:131 好评:0

...

[测试工程] 示波器如何接地?示波器接地步骤介绍 日期:2026-03-02 21:22:18 点击:227 好评:0

[测试工程] 示波器如何接地?示波器接地步骤介绍 日期:2026-03-02 21:22:18 点击:227 好评:0

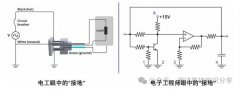

什么是接地? 接地是电路中电流的回流路径。该参考点充当基准线或零伏点,其他电压均以此为基准进行测量。接地确保电气系统的一致性和稳定性,有助于从数据解读到噪声抑制等各...

[测试工程] 什么是hast与uhast? 日期:2026-03-02 20:35:00 点击:193 好评:0

[测试工程] 什么是hast与uhast? 日期:2026-03-02 20:35:00 点击:193 好评:0

hast与uhast是半导体封装可靠性测试中两个非常容易混淆,但目的完全不同的测试。们都是抗湿气能力的加速测试,核心区别在于是否通电。 简单来说: HAST= 高温 + 高湿 +通电,测电路腐...

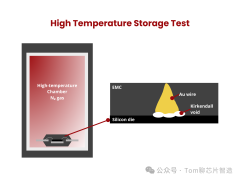

[测试工程] 什么是芯片高温储存可靠性测试? 日期:2026-03-02 19:27:00 点击:228 好评:0

[测试工程] 什么是芯片高温储存可靠性测试? 日期:2026-03-02 19:27:00 点击:228 好评:0

高温储存测试的核心逻辑非常简单:不通电,单纯用高温烤,看芯片能放多久不坏。 高温储存测试的核心目的与原理? 高温储存测试的物理基础是阿伦尼乌斯方程:温度每升高 10C,化...

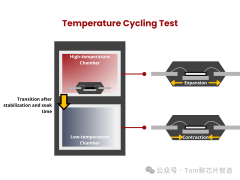

[测试工程] 什么是芯片温度循环可靠性测试? 日期:2026-03-02 18:48:00 点击:227 好评:0

[测试工程] 什么是芯片温度循环可靠性测试? 日期:2026-03-02 18:48:00 点击:227 好评:0

温度循环测试 (Temperature Cycling Test, TCT)是半导体封装可靠性测试(Reliability Test)中最核心、最严苛、也是最常见的一项测试。 它的目的只有一个:通过模拟极端的冷热交替环境,加速暴...

[测试工程] 电源测试之输出动态响应(Output Dynamic Response Tes 日期:2026-02-26 19:36:00 点击:141 好评:0

[测试工程] 电源测试之输出动态响应(Output Dynamic Response Tes 日期:2026-02-26 19:36:00 点击:141 好评:0

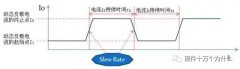

1、测试目的 动态响应一般是指控制系统在典型输入信号的作用下,其输出量从初始状态到最终状态的响应。对某一环节(系统)加入单位阶跃输入x(t)时,其响应y(t)开始逐渐上升,直到...

[测试工程] 硬件基本功——单元测试 日期:2026-02-26 18:02:00 点击:197 好评:2

[测试工程] 硬件基本功——单元测试 日期:2026-02-26 18:02:00 点击:197 好评:2

调试功能基本OK后,进入单元测试阶段。 单元测试,一般是指基于开发人员自行开展的功能测试及各个功能单元的单元测试,是硬件信号级的测试,分为基本测试和信号完整性测试。也...