|

大家都知道IC芯片的可靠性是芯片能不能正常量产的重要指标,那么IC的可靠性都包括哪些呢?ESD(HBM,CDM),HTOL(老化测试),HAST(封装可靠性测试),BHAST(偏压可靠性测试),当然还有芯片的LatchUp测试,本文中,我不会介绍为什么要进行LatchUp测试,只是要介绍一下LatchUp到底要测什么,测试条件是怎么样的? 首先,消费级IC芯片的LatchUp测试主要依据标准JESD78进行测试,当然,会有专门的仪器设备进行测试,通常IC芯片出来之后,会委托第三方实验室进行LatchUp测试,(第三方实验室可以出一个测试报告,这样客户的认可度会比较高,而且设备仪器不用购买以及维护)。那么详细的测试条件和测试步骤分别是什么呢? 首先,是环境温度,有两种,第一种就是在常温进行测试;另外一种就是规定温度下的测试,如最大运行温度,最大运行结温,或者是客户指明的温度等等。这一条件,只需要告诉第三方实验室即可设置。 然后呢就要进行Latchup的测试,主要分为3个部分,其实可以总结为两部分,一是电流测试,另一个是电压测试: 1.电流测试 电流测试分为两部分,正电流测试(灌入电流)和负电流测试(拉电流),主要是对普通IO进行电流测试。

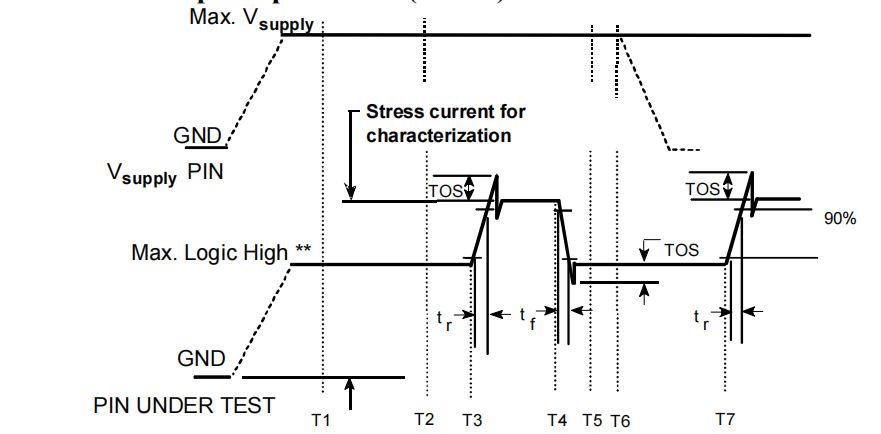

正电流测试

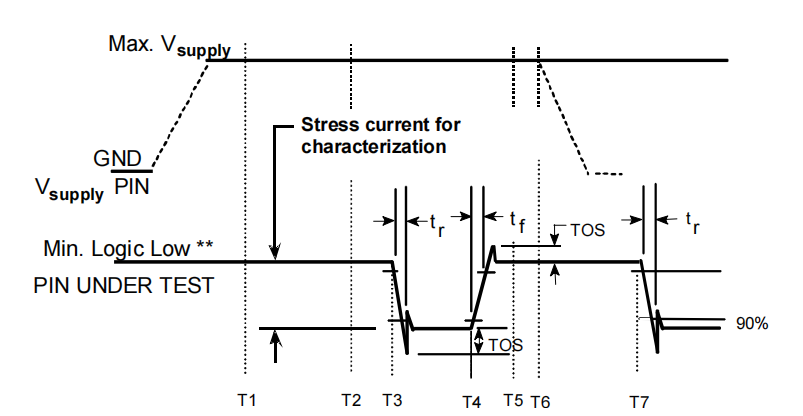

负电流测试 上面两张图描述了正负电流测试过程中芯片电源和测试IO的电压波形。大概如下:测试开始时,给芯片VDD上电,然后测量一个正常情况下的VDD的耗电值,Inormal,之后,给IO加电压(正电流测试时,加最大电压,负电流测试时,加最小电压),然后,对IO进行正负电流的测试,那么IO上的电压会升高或者降低(注意:IO引脚上的电压会限压,防止芯片是因为过压而损坏,具体计算公式在测试标准有),过一段时间之后(至少10us,最大1s), IO 上的正负电流去掉,稳定一段时间之后,再次测量VDD的耗电,Inormal2,比较前后两个电流值,进行判断,如果Inormal <=25mA,那么Inormal2必须小于Inormal+10mA,如果Inormal >25mA,那么Inormal2必须小于1.4*Inormal。这样IO的正负电流就测试完成了。 2.电压测试 电压测试主要是针对芯片的供电引脚,进行过压测试,如下所示:

过压测试 上面的图片描述了Latchup电压测试的流程。在测试过程中,首先给芯片供电引脚加上最大的运行的电压Vmax_operation(注意,Vmax_operation是芯片最大运行电压,不是最大绝对电压,经常有人会弄错),测量此时的耗电Inormal,然后,给芯片供电加1.5*Vmax_operation的电压,过一段时间(10us到1s),芯片供电恢复Vmax_operation,然后再次测量芯片耗电,Inormal2,然后比较Inormal和Inormal2.(比较标准和电流测试的标准一致)。 整个芯片的LatchUp测试流程大概就是这么多,当然,测试过程中,会对电压电流的上升下降和维持有严格的标准,我们这里不做过多叙述,这些需要用到的话直接到测试标准JESD78上面查看即可。 最后,我们再说一下,我们如果要委托第三方实验室做LatchUp实验的话,需要给他们提供什么测试条件:

上面我们提到芯片的LatchUp的测试条件以及测试步骤,如下我们介绍一下LatchUp是如何产生的,为什么在芯片测试中要加入LatchUp测试。

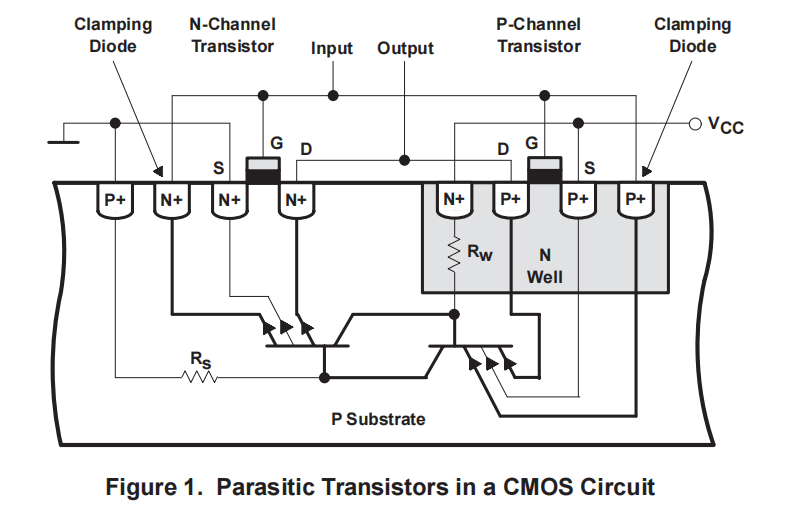

随着芯片的集成越来越高,芯片的体积越来越小,使得芯片的运行速度越来越快,功耗越来越低,但是,随着而来,也会带来一些负面影响,芯片内部的集成电路距离越来越近,相互之间的干扰越来越明显,芯片的LatchUp效应,就是由于电路之间相互影响造成的。 LatchUp效应是指cmos电路中, 在电源power VDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一种低阻抗通路, 它的存在会使VDD和GND之间产生大电流,并且形成正反馈,VDD和GND之间的大电流不会自动减除,只有芯片断电才会消除电流,这种现象重则烧毁芯片,因此我们要极力避免LatchUp效应。 下图是一张典型的IO设计电路图,包括NMOS和PMOS

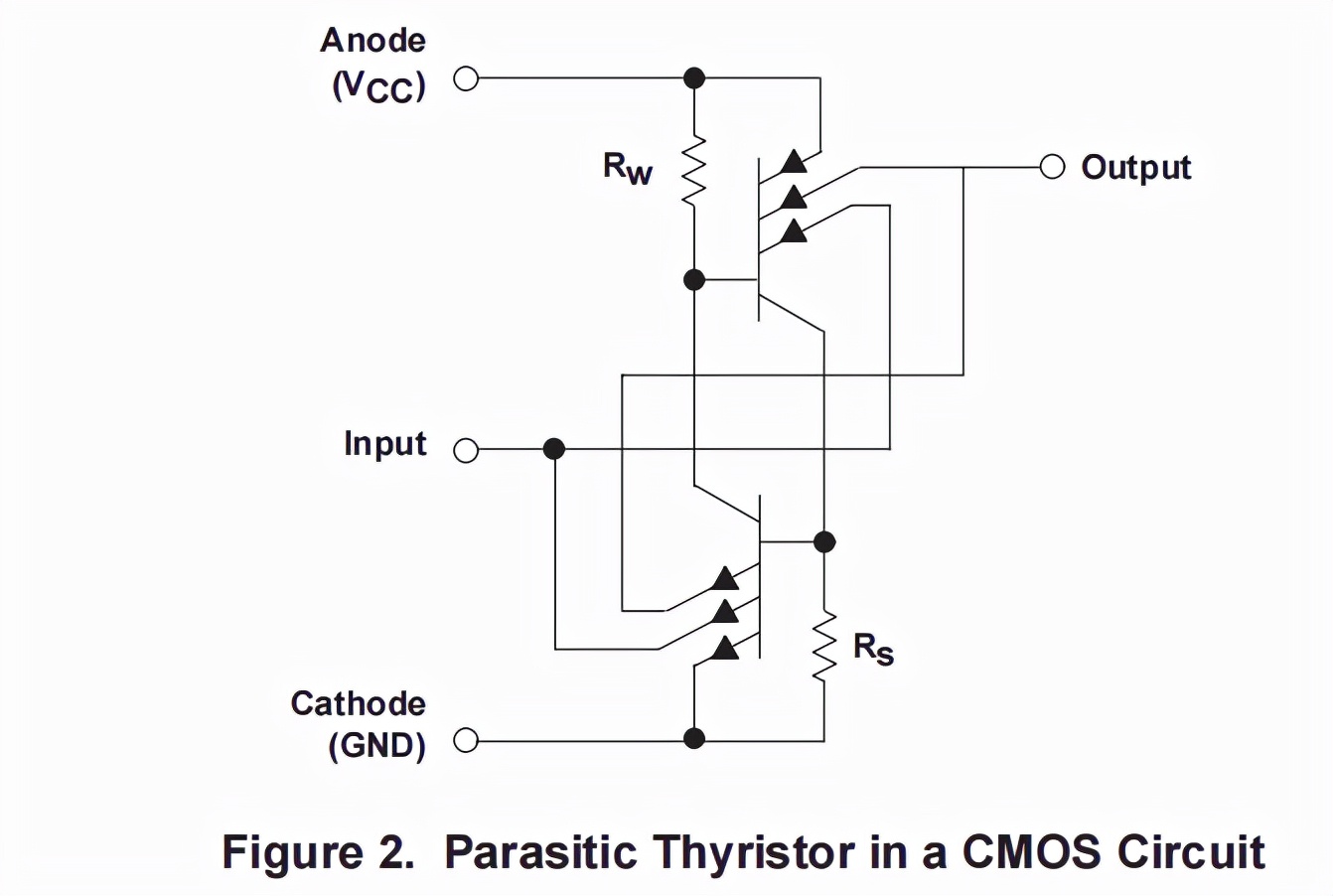

典型的IO CMOS IO设计电路寄生示意图 上图可以看出,NMOS的N+和P衬底加上PMOS的N+和N Well,形成一个寄生三极管;PMOS的P+,N Well加上P衬底会形成第二个寄生三极管,等效出来的电路图如下:

芯片IO CMOS电路寄生等效电路图 根据上图的等效图可以看出,外界信号要想影响该等效电路,有3个地方可以触发,一个是VCC,另外两个就是INPUT和OUTPUT。这时候,我们回过头来看LatchUp的测试,是否能触发该等效电路,这样就可以判断,LatchUp的测试是否有效。 1,电流的正负电流测试。当IO开始施加正负电流时,原则上就相当于在Input和Output上强行将对应的三极管打开,以Output为例,给其注入电流,当Output电压升高,就有几率打开OUTPUT对应的三极管,打开之后,RS两端将会产生压降,进而打开Input对应的三极管,Input对应的三极管打开,又进一步触发,Rw两端也有压降,output对应的三极管进一步导通,因此,当output不再注入电流,该等效电路也不会停止工作,会一直维持下去,现象就是VDD对GND存在一个不正常的电流。 2.电压的测试,即给VDD施加一个脉冲,OUTPUT对应的三极管的基极对GND是有寄生电容的,VDD的快速上升,有可能在Rw产生一个短暂的压降,如果该压降打开了OUTPUT对应的三极管,那么对导致RS产生压降,进而导通INPUT对应的等效三极管,这样,RW的压降将会维持,当VDD电压恢复正常,等效电路不会停止工作,VDD对GND存在电流回路。 上面分析可以发现,LatchUp的测试项确实可以触发Latch Up效应的产生,这样芯片测试就需要经过LatchUp测试,过了这个测试,表示LatchUp现象发生的可能性最低。 当然,还有其他的外部条件,也会触发LatchUp等效电路,如芯片ESD,这些都会有相应的测试作为保证,本文不多做介绍。 那么该如何防止芯片LatchUp呢? 首先,需要在芯片设计中考量,比如使用重掺杂衬底,降低RS,以及Rw,降低三极管的导通的可能性,NMOS和PMOS隔离等等,我这里不做多介绍,因为我也只是表面了解。 另外,应用电路中的考量,在VDD上串联电阻,磁珠,减少VDD的脉冲干扰。 说实话,主要是要在芯片设计的时候考量这些东西,芯片设计的时候就解决这些隐患,应用层面上的解决手段比较匮乏。 |