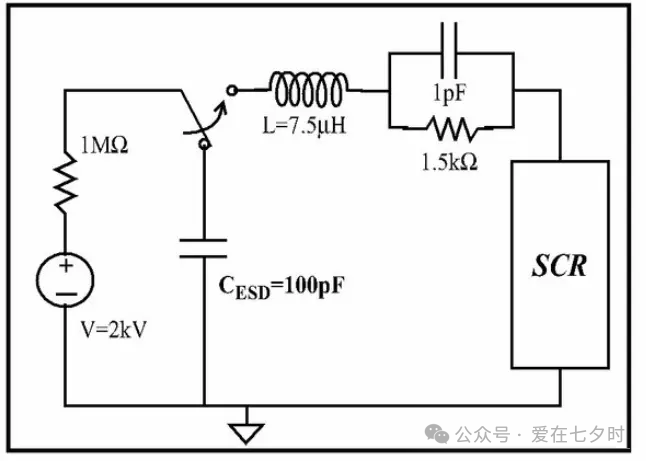

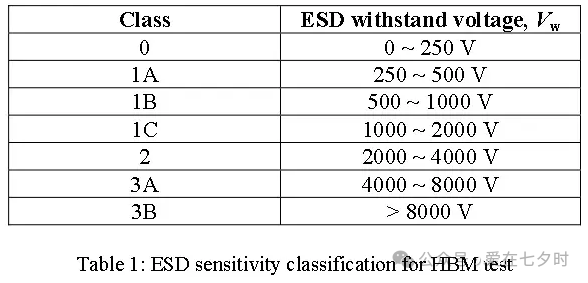

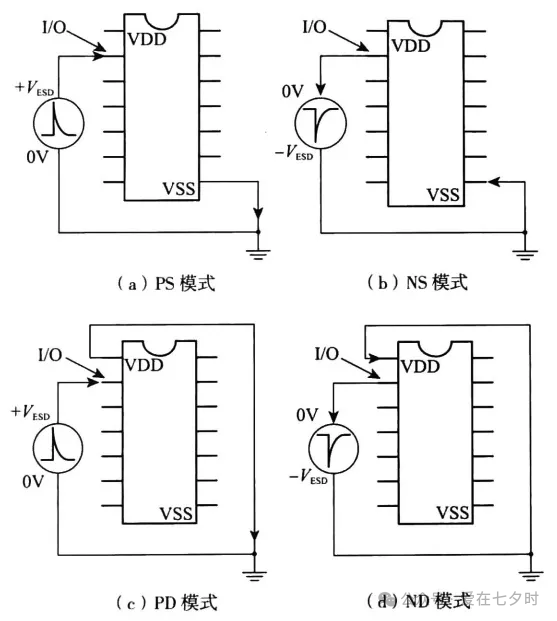

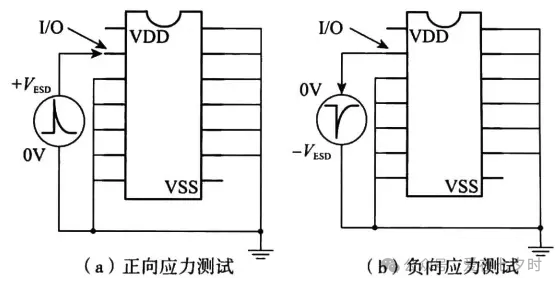

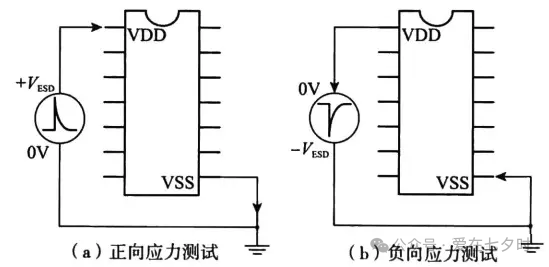

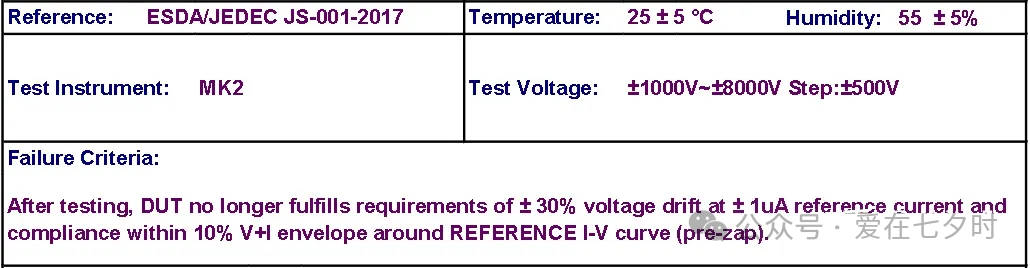

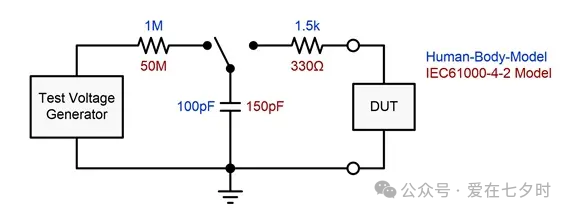

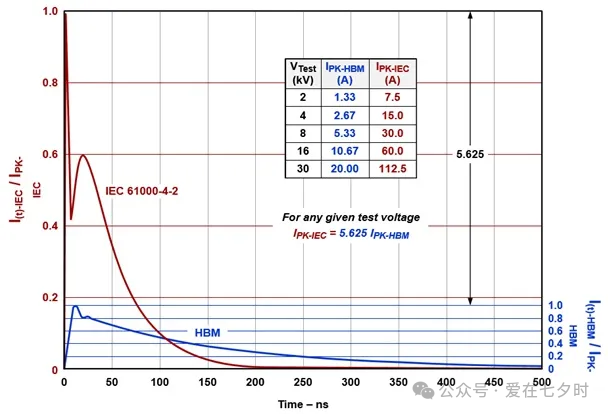

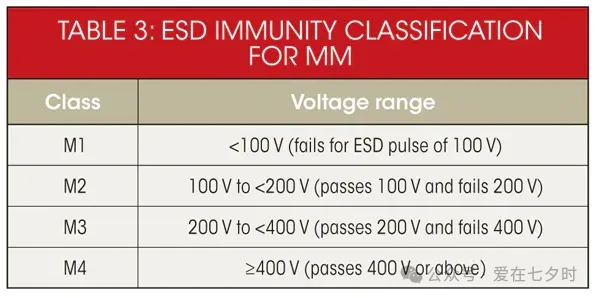

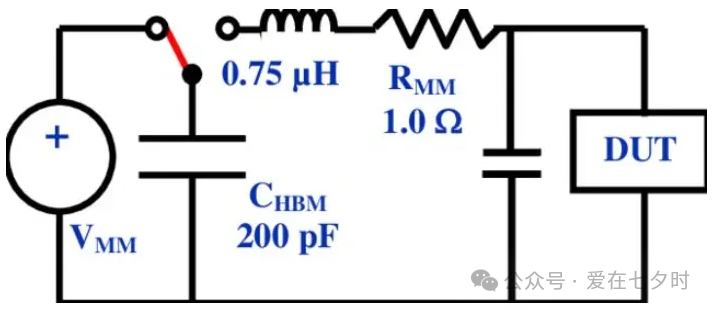

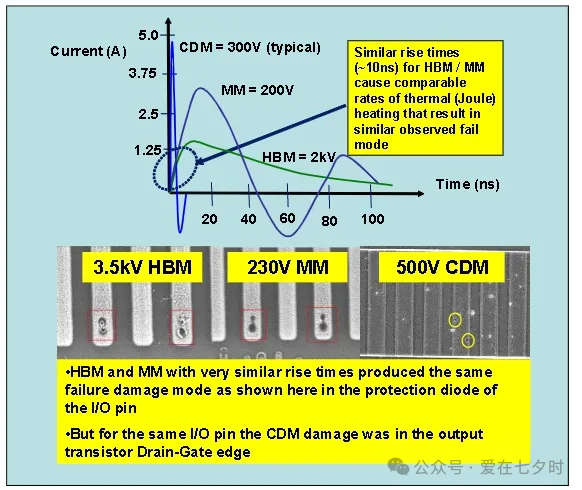

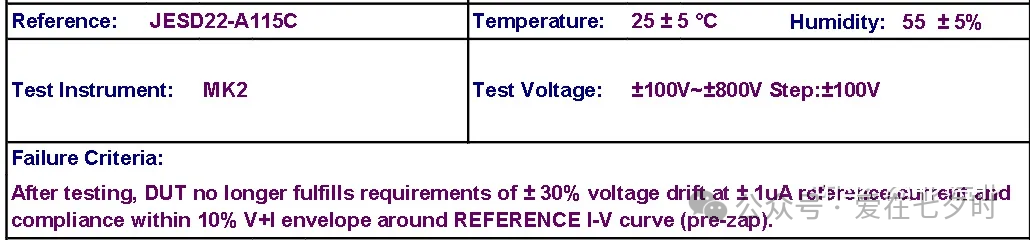

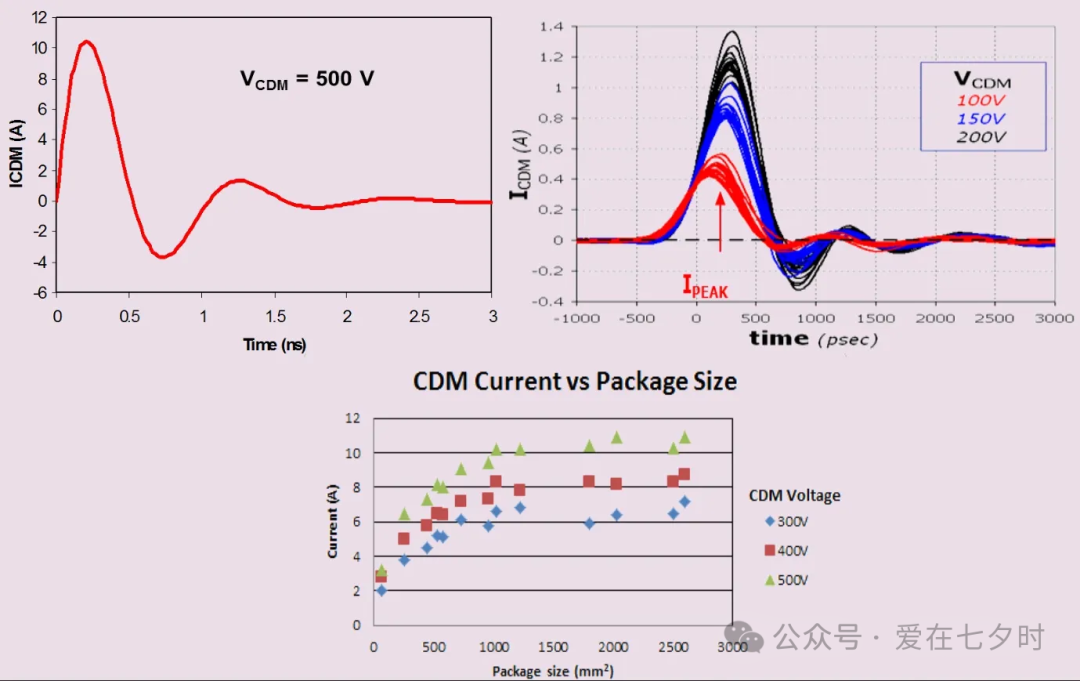

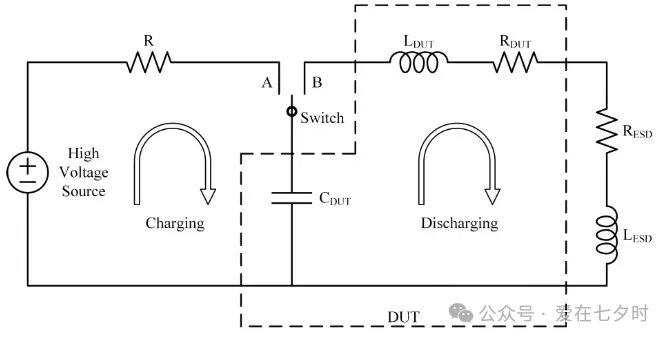

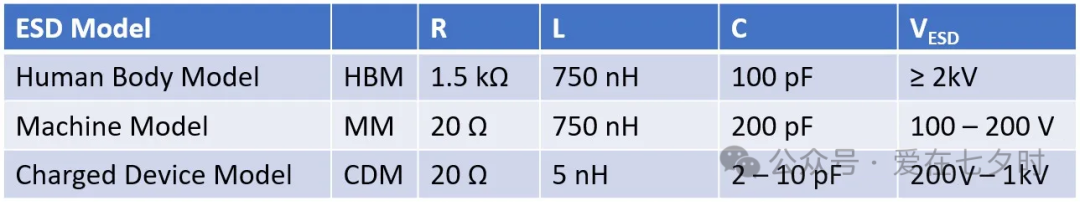

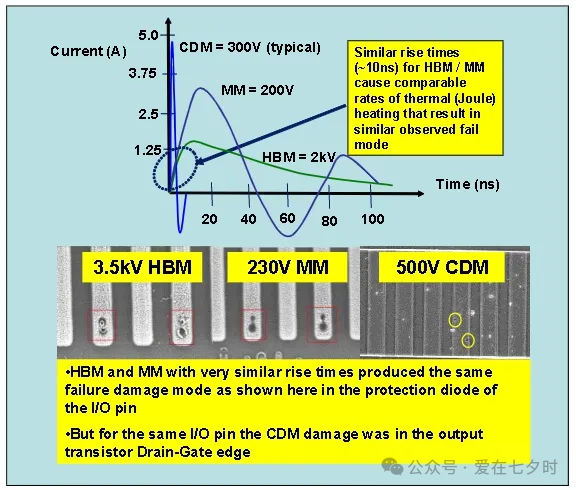

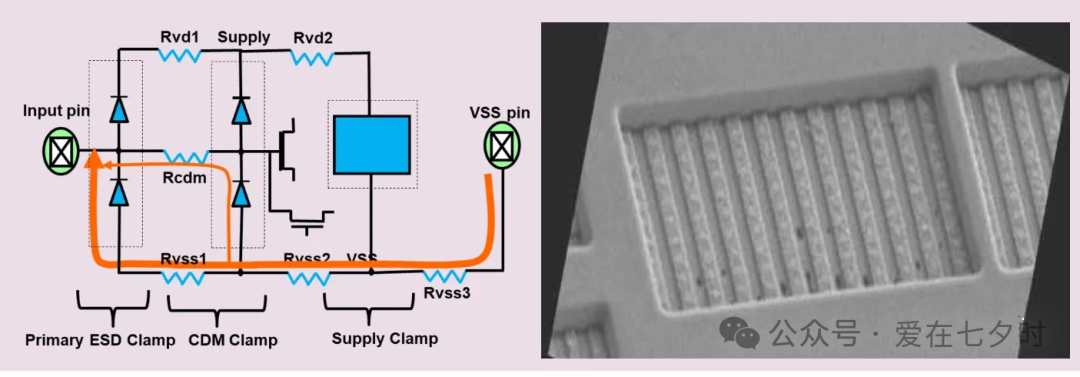

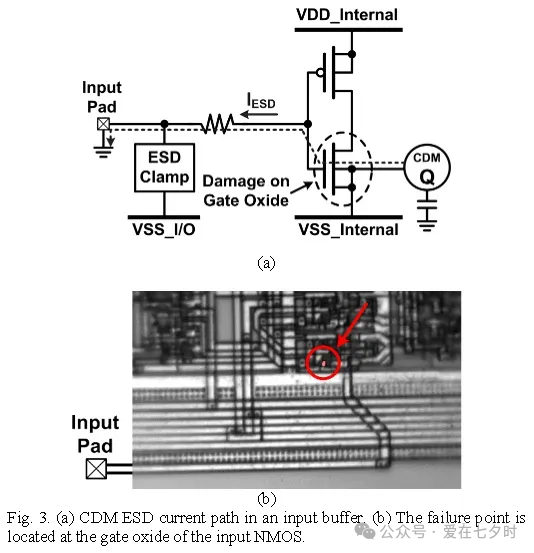

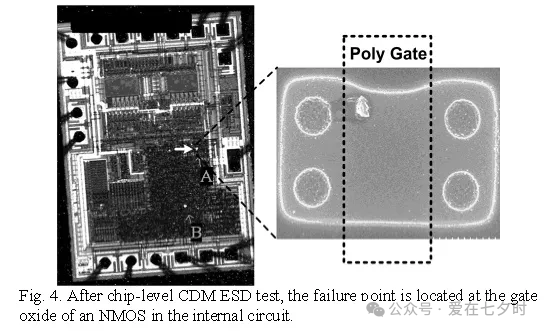

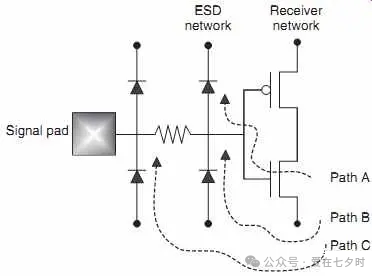

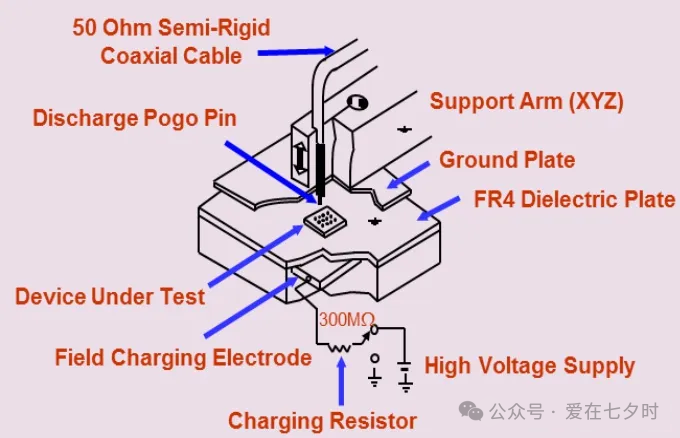

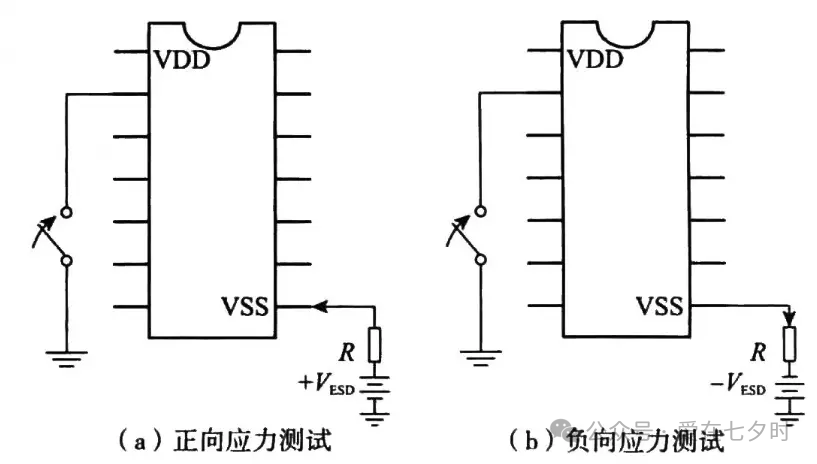

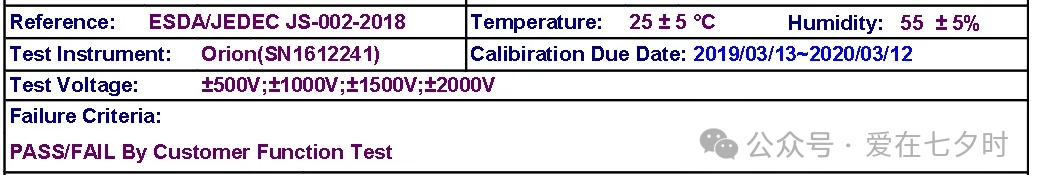

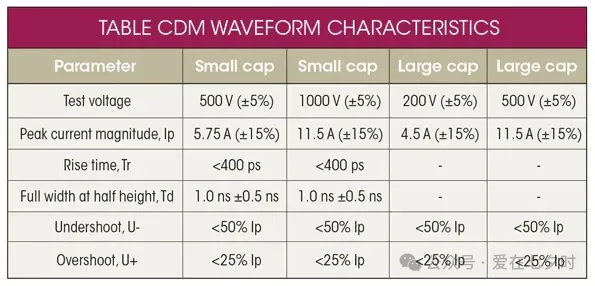

静电放电即ESD(Electro-Staticdischarge),是指具有不同静电电位的物体互相靠近或直接接触引起的电荷转移。ESD是20世纪中期以来形成的以研究静电的产生、危害及静电防护等的学科。因此,国际上习惯将用于静电防护的器材统称为ESD。ESD产生的原因多种多样,对集成电路放电的方式也有所不同。为了保证集成电路产品的良率,提高可靠性,需要对集成电路ESD防护能力进行测试。一般可分为两类:样品研究型测试和产品通过型测试。 (1)样品研究型测试:在芯片的研发阶段,与ESD防护研究最为相关的是防护器件的功能测试。此阶段的测试广泛采用传输线脉冲技术(TLP)。通过 TLP测试,可以获得防护器件的关键性能参数,便于在生产制造过程中调整相关的设计,从根本上提高产品的ESD防护能力,保证良率。 (2)在产品通过型测试中,为了更好地量化不同情形下的ESD冲击,一般分为五种不同的模型。包括工业界作为产品片上ESD等级衡量标准的:HBM、CDM、MM模型和针对板级和系统级ESD防护的IEC(International electrotechnical commission)模型和HMM人体金属模型(Human metal model)。一、 HBM模型:人体因摩擦等原因带上一定的静电荷之后,与集成电路的某些引脚接触且集成电路的另一部分引脚恰巧接触到地时,人体上的静电荷就会流经集成电路进入大地。人体能贮存一定的电荷,所以人体明显地存在电容。人体也有电阻,这电阻依赖于人体肌肉的弹性、水份、接触电阻等因素。大部分研究人员认为电容器串一电阻是较为合理的电气模型,。早在1962年,美国国家矿务局测得22人次人体电容范围为95~398PF,平均电容值为240,100次试验测得手与手之间的平均电阻为4000Ω。这些数据为建立了人体模型起了一个好的开端,做过一些修改之后,用在电子工业中建立早期的模拟电路。Kirk等人测得人体电容值的范围为132-190PF。人体电阻值为87-190Ω。为了求得一致,美国海军1980年提出了一个电容值为100PF,电阻为1.5kΩ的所谓“标准人体模型”。Human-Body Model and Electrostatic Discharge (ESD) Tests - In Compliance Magazine。这一标准得到广泛采用,但在后来也遇到一些问题。HBM模型放电时间长,峰值电流小,大约在几百纳秒的时间里产生数安培的瞬间放电电流。如果没有适当的防护措施,这个瞬间的大电流足以对集成电路芯片造成损坏。  添加图片注释,不超过 140 字(可选) 典型的HBM波形有2~10纳秒的上升时间、0.67安培/千伏特的电流,及200纳秒脉冲宽度的双重指数信号衰减波形。在ESD的仿真中,添加这样一个pulse电压。在HBM的情况下,这个pulse的peak电压取Vtrigger,上升沿和下降沿是1ns,持续时间400ns。而针对CDM,加入一个高达15V的pulse,上升沿和下降沿都是200ps,持续5ns。  添加图片注释,不超过 140 字(可选) 在实际使用过程中,芯片的每只引脚都有可能遭受ESD袭击,并且所带的静电电荷有可能是正电荷也有可能是负电荷,因此在芯片出厂之前需要对每只引脚进行相应的正向静电应力和负向静电应力测试。对于HBM,根据芯片引脚的分类,主要是: (1)I/O引脚对电源和地引脚的应力测试:对于每一个I/O引脚而言,其相对于正电源或者负电源都可能存在正向静电应力和负向静电应力,因此I/O引脚有四种测试模式,PS模式(positive to VSS),NS模式(negative to VSS),PD模式(Positive to VDD),ND模式(negative to VDD)。当某一引脚对电源进行应力测试时,其他引脚需处于悬浮状态。  添加图片注释,不超过 140 字(可选) (2)I/O引脚到I/O引脚应力测试:不同I/O引脚之间也存在正、负两种应力情况,在实际静电放电过程中,通常是其中某一个I/O引脚遭受ESD应力而另一个或多个I/O引脚接地形成ESD路径。为了节约时间并更全面地模拟现实情况,通常对某一I/O引脚进行I/0引脚到I/O引脚的应力测试时,要将其他所有I/O引脚全部接地。电源VDD引脚和VSS引脚处于悬空状态。  添加图片注释,不超过 140 字(可选) (3)VDD引脚到VSS引脚应力测试:电源引脚之间也存在正、负两种应力情况,在进行正电源VDD引脚到负电源VSS引脚的应力测试时,所有I/O引脚需处于悬浮状态。  添加图片注释,不超过 140 字(可选) HBM试验步骤:(1)准备好被测样品的规格书,内容要包括其PIN脚的定义图。一般分类有四种:电源,地,输入和输出四大类; (2)准备一个连接器,此连接器焊在PCB上,并从PCB上引出PIN用于插在测试仪器的PIN槽;(3)准备好需要的样品数;(4)准备好需要测试模块参数性能的仪器;  添加图片注释,不超过 140 字(可选) HBM静电放电故障判断:静电敏感器件(ESDS)经ESD测试后,要判断是否已被破坏,以便决定是否要再进一步测试下去,但是如何判定该静电器件已被ESD所损坏了呢?常见的有下述三种方法: (1)绝对漏电流:当器件被ESD测试后,其I/O脚的漏电电流超过1uA(或10uA)。漏电电流会随所加的偏压大小增加而增加,在测漏电电流时所加的偏压有人用5.5V(VDD×1.1),也有人用7V(VDD×1.4) (2)相对I-V漂移:当器件被ESD测试后,自I/O脚看进入器件内部的I-V特性曲线漂移量在30%(20%或40%) (3)功能观测法:先把正常且符合规格值器件的每一只脚依测试组合打上某一电压准位的ESD测试电压,再拿去ATE复测是否符合原来的规格。 知名的IEC61000-4-2有时也称为「人体放电模型」,但该模型是针对一个系统中不同操作条件下发生的各种ESD事件,故仅适用于该系统而已。IEC 61000-4-2和JS-001的波形和严谨度无法互比。在组件组装、包装和运输可能对单个组件造成 ESD 损坏的半导体制造环境中,组件级 ESD 额定值是必需的。在这里,测试脉冲发生器产生一个 ESD 脉冲,模拟带电人员通过被测设备 (DUT) 对地放电。因为通过应用 ESD 防护装备在受控的 ESD 环境中执行组件的处理,所以组件上的 ESD 应力大大降低。因此,HBM 测试是一种不太严格的 ESD 测试。对于受控环境来说已经足够了,但对于不受控 ESD 环境中的系统来说是不够的。在不受控制的现场环境中需要系统级 ESD 额定值,例如,带电的最终用户可以使包含半导体器件的手持式仪器在用户插入时触摸连接器引脚时承受超过 40 kV 的 ESD 水平或拔下电缆。为了更好地评估系统的 ESD 漏洞,开发了 IEC 61000-4-2 标准。该标准模拟了带电人员通过金属物体(例如螺丝刀)向接地电气系统放电。HBM 和 IEC 61000-4-2 标准之间的主要区别在于测试期间施加的雷击次数和发生器模型,这会在测试脉冲的上升时间和峰值电流方面产生差异。  添加图片注释,不超过 140 字(可选) 两种波形的电流脉冲上升时间明显不同。IEC 61000-4-2 雷击的电流上升时间小于1ns。当暴露于 IEC-ESD冲击时,设计用于处理HBM冲击的ESD结构可能无法足够快地运行。因此,保护电路不能充分发挥保护器件的作用,结果器件被损坏。峰值电流的大小对于组件能否经受 ESD冲击至关重要。 IC有可能在 8kVHBM冲击下幸存下来,但在低得多的 2kV IEC-ESD 冲击下失效。HBM规范中的ESD冲击次数仅限于单次正极冲击和单次负极冲击,而IEC61000-4-2要求至少10次正极冲击和10次负极冲击。因此,在HBM测试期间,组件可能会在第一次撞击中幸存下来,但由于第一次撞击中遭受的损坏而在随后的撞击(如果应用)中失败。  添加图片注释,不超过 140 字(可选) 最终用户应用在其生命周期内可能会受到多次ESD冲击。因此,系统设计人员应始终质疑组件数据表中通用的 ESD规范。根据 IEC 61000-4-2 标准测试的设备通常表明这一事实,而根据其他规范进行测试的设备通常不会说明正在使用的规范。这些设备通常根据不太严格的 HBM 标准进行测试。 二、 MM模型(此模型测试标准已取消):机器模型是指生产制造过程中,机器本身有可能积累电荷,若与集成电路产品的部分引脚接触并与地构成回路,静电荷就会流经集成电路到地。  添加图片注释,不超过 140 字(可选) 在测试设置中,与电阻器串联的高压 (HV) 电源为电容器充电,使用一个开关将其从 HV 电源中移除,并将其连接到电感器以进行放电,产生一个指数衰减的正负向振荡电流波形。商用 MM 测试仪在 MM 激励电路中内置了电感器。必须存在这些电感器才能产生 MM 测试方法所需的振荡波形。然而,电感器实际上减慢了 MM 波形,因此 MM 不能像 CDM 那样代表非常快的金属对金属接触放电。另一方面,CDM测试直接表现为提升封装电位,直接将管脚接地产生快速放电。不能依靠 MM 来准确模拟快速金属对金属接触放电。MM 模型的应力电流水平远高于 HBM 模型的应力电流水平。对于 200 V MM 应力水平,峰值电流为 3.5 安培或等效的 4kv HBM ESD 应力脉冲。  添加图片注释,不超过 140 字(可选) HBM 和 MM 具有相似的上升时间(2~10 ns)和总持续时间,导致相似的热 (焦耳) 加热率,导致两种模型的故障机制相似,即MM 测试的失效特征和放电过程与 HBM 测试基本相同。因此,在此时间段内发生的硅中的任何热加热都会导致两种模型的相同失效机制。这适用于所有技术,包括先进的技术节点。波形的这个早期部分决定了在设计中必须在何处以及如何部署保护电路。具有相似的上升时间特性,HBM 和 MM鼓励相同的保护设计。因此,HBM测试可以保证 MM ESD的稳健性。通常,MM ESD的应力水平比HBM ESD低约10倍。HBM 的保护电压电平通常为~2kV,而MM为~200V。  添加图片注释,不超过 140 字(可选) MM模型是在日本开发的,并在日本被广泛使用,该模型对寄生效应非常敏感,对测试人员的控制和遵守标准非常困难。 除非客户特别要求,MM压力仅供参考。 MM 模型已被更精确的 CDM 和 HBM 模型所取代。在 ESD 器件测试的早期,人们希望避免 HBM 测试的高预充电电压(2kV 或更高),并且“MM”的 200pF 和低阻抗被认为是等效但安全的较低电压测试以解决与 HBM 相同的故障机制。然而,很难实现从 MM 电压到 HBM 电压的单一转换。保护设计传统上专注于满足 HBM 要求,但MM 测试仪容易受到寄生电路元件的影响;仿真器中继电器开关网络的这些寄生效应导致 MM 波形比 HBM 测试仪的波形变化更大。尽管如此,在没有任何支持数据的情况下,200V MM 成为事实上的要求。它被认为是处理的安全水平,并且必须同时满足这个水平以及事实上的 2kV HBM 标准。 实际上,具有 2kV HBM 耐压的设备可能具有 100 到 300V 的 MM 耐压,具体取决于设备特性和 MM 测试仪寄生效应。这导致与指定 HBM 和 MM 规范级别相关的许多混淆。停止使用 MM 的下一个重要原因是 MM 不能正确表示金属表面的快速放电。 MM 上升脉冲的特性不是基于机器脉冲测量值的比较确定的,而是由已经开发的 HBM 模拟器的特性确定的。使用当前标准 CDM 测试方法实际上可以更有效地模拟金属对金属放电的快速上升前沿。由于高速示波器的发展,这一点如今已为人所知。然而,在 1980 年代,人们误解了MM是 CDM 的良好代表。这种误解实际上延迟了今天使用的 CDM 标准的最终开发和接受。在 1990年代后期,随着对 CDM的测试有了很大改进和准确,并且随着对快速放电仅由 CDM覆盖的更广泛的认识,MM测试更频繁地被 CDM 取代。對於不同的測試器,MM的耐受電壓可能會不同,測試結果不具重複性,而HBM的良好重複性則可針對相同的故障模式,故HBM是業界今天鮮少採用MM的主因。JEDEC和ESDA不推薦以機器模型來做產品的合格認證,而建議以HBM和CDM取代。然而,ANSI/ESDA MM 5.2文件的最後版本是2013年,基於前述「白皮書」中的爭議論點,測試流程因而重新分級,從「標準」到「標準測試方法」。積體電路(ICs)的機器模型測試應限制於不具耐受電壓和電場充電相關性的故障分析。 不同的客户部门可能会出于特定原因认为他们需要增强 ESD 要求。例如,一些汽车客户更一致地要求 MM 模型测试;给人的印象是独立和冗余的测试提供了增强的安全性、改进的质量和减少的缺陷。然而,行业经验表明,通过冗余(对 HBM)MM 资格测试并不能帮助汽车制造商实现这些目标。满足当前的行业标准 HBM / CDM 将确保产品可以安全处理并留有足够的余量,以防止 ESD 损坏并保持产品从组件制造商发货时的质量/可靠性。由于许多疑似 ESD 故障本质上是更高能量的 EOS,因此在制造过程中防止电气过应力的方法也将有助于保持产品的可靠性。Discontinuing Use of the Machine Model for Device ESD Qualification - In Compliance MagazineMM和HBM一样,都是外界带电体接触IC产品形成的放电现象,因此测试方法与HBM相同。  添加图片注释,不超过 140 字(可选) 三、CDM模型:充电器件模型CDM不同于HBM和MM两种放电模型,它是指集成电路产品本身在组装或者运输过程中被充电,接触到地或者其他导体时发生电荷转移,电荷从集成电路内部流出。 CDM 测试模拟充电集成电路与接地表面金属接触时所经历的快速放电。这正是现代印刷电路生产线中预期的那种 ESD 应力。印刷电路板自动快速地从一个位置移动到另一个位置,同时高速机械臂从托盘或卷轴上抓取组件并将它们放置在电路板上。速度至关重要,导致静电充电和放电的机会众多。工厂 ESD 专家努力最大限度地减少设备充电和控制放电,但所有组件都必须具有一定的能力来承受它们可能暴露的放电。 ESD控制工程师需要了解通过其生产线的所有组件的带电器件 ESD稳健性。CDM 测量提供了这种知识。 由于IC内部积累的静电会因集成电路组件本身对地的寄生电容而变化,集成电路摆放的角度与位置以及IC所用的封装形式都会造成不同的寄生电容。左下图显示了集成电路封装在 500v CDM 应力电压下充电后流经集成电路引脚的 CDM 放电电流。右下图说明,对于相同的封装尺寸,集成电路封装的预充电电压越高,流经封装引脚的放电电流就越大。下图中的图片说明了集成电路封装电容如何随着封装尺寸的增加而增加,这意味着集成电路 CDM 引脚放电电流会随着封装尺寸的增加而增加。芯片尺寸较大的 IC 可以在其体内存储更多的静电荷,这会导致 CDM ESD 事件期间的放电电流更大。  添加图片注释,不超过 140 字(可选) 此外,CDM ESD事件的峰值电流大且持续时间短,增加了有效保护内部电路免受CDM ESD事件影响的难度。为提供高效的 CDM ESD 保护,ESD 保护器件应快速开启并具有较高的 ESD 鲁棒性。此外,CDM ESD 电流从芯片基板流向外部接地,而 HBM 和 MM ESD 电流从外部 ESD 源注入到被击穿的引脚中。因此,CDM ESD 事件通常会对 CMOS IC 造成内部损坏。与 HBM 和 MM ESD 事件相比,CDM ESD 事件中的放电电流不仅巨大,而且速度更快。由于 CDM ESD 事件的持续时间远短于 HBM 和 MM ESD 事件的持续时间,因此在 ESD 保护电路开启之前,CDM ESD 事件可能会损坏 IC。当信号频率增加时,电容器将成为低阻抗器件。因此,CDM ESD 电流最有可能流经 IC 中器件的电容结构。在 CMOS IC 中,MOS 晶体管的栅极氧化层为电容性结构,因此栅极氧化层在 CDM ESD 事件下最容易损坏。在纳米级CMOS工艺中,栅氧化层变薄,使得单位面积的等效电容变大。因此,纳米级 CMOS 工艺中较薄的 MOS 晶体管栅极氧化物更容易受到 CDM ESD 应力的影响。此外,更多的功能被集成到单个芯片中,这使得裸片尺寸更大。在相同的充电电压下,较大的电容存储更多的静电荷,因此对于芯片尺寸较大的IC,CDM ESD电流较大。因此,具有较大裸片尺寸和较薄栅极氧化物的纳米级 CMOS IC 对 ESD 非常敏感,尤其是 CDM ESD 事件。上述特性使 CMOS IC 的 CDM ESD 保护更具挑战性。Evolution of Charged Device Model ESD Target Requirements - In Compliance Magazine 芯片内部的静电荷积累缓慢,不会对芯片造成任何损坏。但由于放电路径的寄生阻抗(包括电阻和电感)很小,上升时间和持续时间与HBM相比极短,可能会产生放电CDM 电流高达数十安培。等效电路如图 1-4 所示。当开关在A处闭合时,高压电源对DUT的等效电容CESD充电,表明芯片在生产或运输过程中携带静电荷;当开关在B处闭合时,放电电路导通,说明芯片管脚接触地或导体,内部电荷流出。 CDM 测试仪电气原理图如图 1-5 所示。DUT(RDUT、CDUT 和 LDUT)的参数与芯片的布局、裸片尺寸、工艺流程和封装有关。  添加图片注释,不超过 140 字(可选)  添加图片注释,不超过 140 字(可选) 对于 CDM,上升时间要快得多(0.1 – 0.5 ns),持续时间约为6~8纳秒,电流应力约为相同ESD应力下HBM模型的15~20倍,并且通常会导致独特的故障机制,如氧化物击穿。更重要的是,当 CDM 水平不足时,观察到的 ESD 场故障主要是氧化物击穿。因此,CDM 通常需要一套不同的保护策略。这使得关注 CDM 认证变得更加关键,而不是使用 MM 复制 HBM 测试信息。在使用 HBM、MM 和 CDM 进行应力处理后观察到的同一 I/O 引脚的故障模式。很明显,对于 HBM 和 MM,保护二极管中的损坏部位相同,但对于 CDM 应力,损坏部位对应于输出晶体管中的氧化物击穿。这也说明了这样一个事实,即在采用正确有效的设计技术之前,满足高水平的MM 并不能提高 CDM 性能。CDM事件的时间尺度明显低于热扩散时间;因此,CDM事件处于温施-贝尔功率到失效曲线的“绝热状态”。因此,CDM事件与长脉冲电过应力(EOS)事件的方向相反。  添加图片注释,不超过 140 字(可选) 左下图表示输入引脚的正 CDM 应力,橙色路径表示该引脚在应力期间的电流放电路径。右下图显示了在引脚上施加 500v (10A) CDM 应力后,输出晶体管漏极处的栅极氧化物区域的薄氧化物栅极损坏。  添加图片注释,不超过 140 字(可选) 在 0.8-μm CMOS 工艺中制造的输入缓冲器中的 CDM ESD 电流路径如图 3(a) 所示。该芯片通过了 2kV HBM 和 200V MM ESD 测试。虽然该芯片在其输入焊盘处配备了 ESD 保护电路,但经过 1000-V CDM ESD 测试后仍然损坏。如图 3(b) 所示,CDM ESD 测试后的失效点位于输入缓冲器中 NMOS 的栅极氧化层。由于考虑到 I/O 单元和内部电路之间的噪声隔离,I/O 单元的 VSS (VSS_I/O) 和内部电路的 VSS (VSS_Internal) 在芯片布局中往往是分开的。因此,位于输入焊盘的 ESD 钳位器件在 CDM ESD 应力期间无法有效保护输入缓冲器的栅极氧化层,因为 VSS_I/O 和 VSS_Internal 之间没有连接。损坏输入缓冲器中 NMOS 栅极氧化物的 CDM ESD 电流如图 3(a) 中的虚线所示。  添加图片注释,不超过 140 字(可选) 图 4 是另一个 IC 在 CDM ESD 测试后的故障图。该 IC 采用 0.5-μm CMOS 工艺制造。扫描电镜 (SEM) 图片证明 CDM ESD 事件引起的故障位于内部电路中的 MOS 晶体管的多晶硅栅极,该 MOS 晶体管通过金属连接连接到某个输入焊盘。从上述两种情况来看,即使在输入端施加了 ESD 保护电路,在 CDM ESD 应力下,存储在芯片主体中的电荷仍然会流过内部电路中输入 MOS 晶体管的栅极端子,从而损坏其栅极氧化物。根据以往的工作,IC产品的拐角处的引脚更容易遭受CDM ESD事件,因为拐角处的引脚通常首先接触到外部接地。  添加图片注释,不超过 140 字(可选)  添加图片注释,不超过 140 字(可选) 对于CDM故障,存在解决低级故障机制的电路解决方案。可以将额外的ESD电路元件添加到现有电路中,以求解CDM以获得可接受的结果。图13是常用的CDM ESD网络的示例。ESD网络工作包括放置在信号焊盘附近或附近的第一级双二极管网络。第二组二极管(例如,第二级网络)放置在接收器电路附近。在第一级和第二级之间放置一个电阻。图13示出了CDM事件在带电基板的情况下的可能路径。图中显示了从带电接地轨(例如p基板)到接地接收器引脚的CDM电流路径的三条路径。对于基板的正充电,电流从基板流向任何可能的路径,该路径将到达接地的信号焊盘节点。路径 A 通过 n 沟道 MOSFET 接收器电路并到达第二级 ESD 二极管。路径B通过基板到达第二级二极管网络。路径C通过基板到达第一级ESD网络。静电放电测试:带电设备型号 (CDM) (industrial-electronics.com)  添加图片注释,不超过 140 字(可选) 由于CDM的放电机制与HBM、MM不同,所以CDM的测试方法也有所区别。CDM测试分两步进行,首先静电电压需要被充入待测IC的衬底上,并储存在衬底之中,为避免充电过程对IC造成损坏,充电电压必须串联一个高阻值的限流电阻(10MΩ以上)。对P型衬底的IC而言,VSS引脚已与衬底相连,因此该充电电压是经由限流电阻对VSS充电。当IC充电以后,IC本身就带有正电压或者负电压,接下来再由该IC的其他引脚(I/O,VDD)等在连续的集成电路封装充电周期后一个接一个地放电。这意味着在 CDM 模拟期间,集成电路的每个引脚都会释放集成电路封装充电周期产生的电流,以完成CDM的静电放电测试。CDM测试分为插座放电(socketed)和非插座放电。插座放电是指该引脚是经由IC插座与继电器开关的。非插座方式放电是指带电的IC在浮空的状态下,经由放电探棒直接放电。  添加图片注释,不超过 140 字(可选)  添加图片注释,不超过 140 字(可选)  添加图片注释,不超过 140 字(可选) 在对所有引脚(正极和负极)进行应力处理后,器件仍需要满足所有数据表和功能规范。不幸的是,CDM 测试有时会给出令人困惑的结果。这些变异来源中的大多数都可以被表征或控制。尽管没有两个 JEDEC 测试头是相同的,但可以对测试头的差异进行电气建模。充电时间可由CDM系统软件控制。接地平面可以按照严格的公差制造。可以获得正确类型的 pogo pin,并且可以在每次试运行前清洁 pogo pin。电容器盘可以在每次使用前进行清洁。 1Ω径向电阻可以用四点探头精确测量,分析波形的软件在计算Ip时可以将测量考虑在内。 CDM 室中流动的干燥氮气可提供湿度控制和更可重复的结果。然而,即使这些问题得到解决,仍然存在由示波器分辨率差异引起的系统间差异的挑战。Charged Device Model (CDM) ESD Testing: Getting a Clearer Picture | Electronic Design  添加图片注释,不超过 140 字(可选)  添加图片注释,不超过 140 字(可选) 我们已经调查了 CDM 测试中一些更常见的可变性原因。已发现在放电事件期间发生的电流与时间波形的不正确测量是最重要的变化源。更好地测量 CDM 波形,使用更高带宽的示波器来消除系统间的差异,从而获得更可重复的测试结果。在不久的将来,当 ESDA 和 JEDEC 发布他们的联合 CDM 规范时,这将变得更加重要。为了符合规范,CDM放电波形必须具有满足 CDM 规范表中定义的要求的特性:  添加图片注释,不超过 140 字(可选)  添加图片注释,不超过 140 字(可选) 而至于针对板级和系统级ESD防护的IEC(International electrotechnical commission)模型和HMM人体金属模型(Human metal model)这两种在本文中就不过多赘述了,以后有需要了,再给大家讲讲了,希望有兴趣的朋友们多多支持和批评指正哦! |