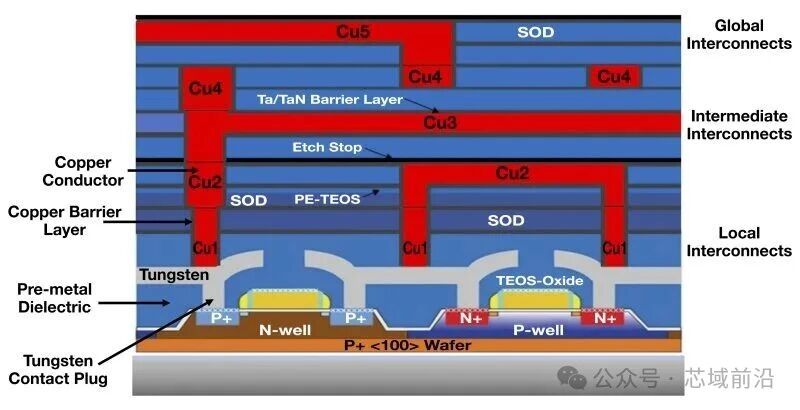

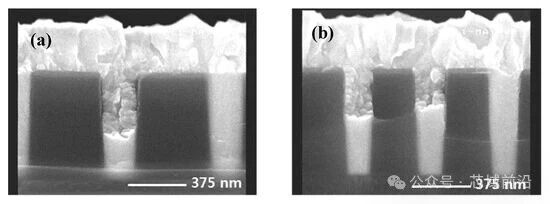

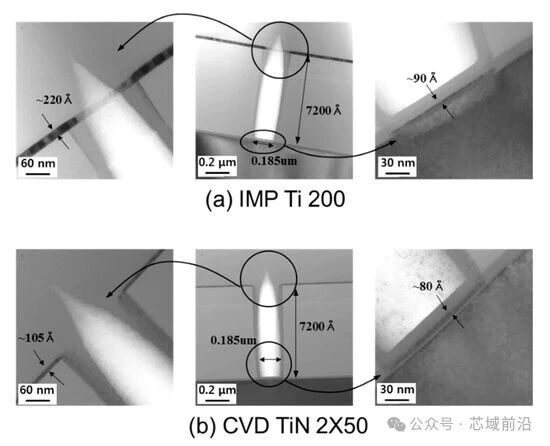

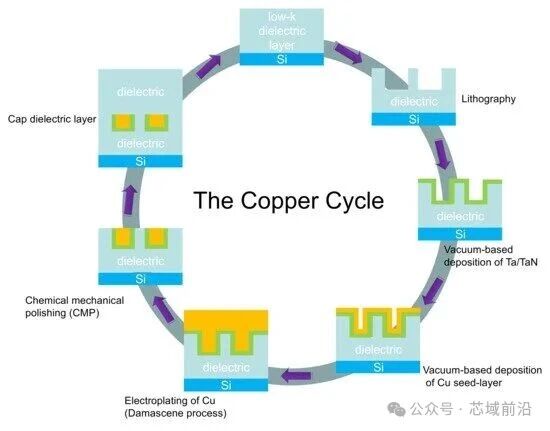

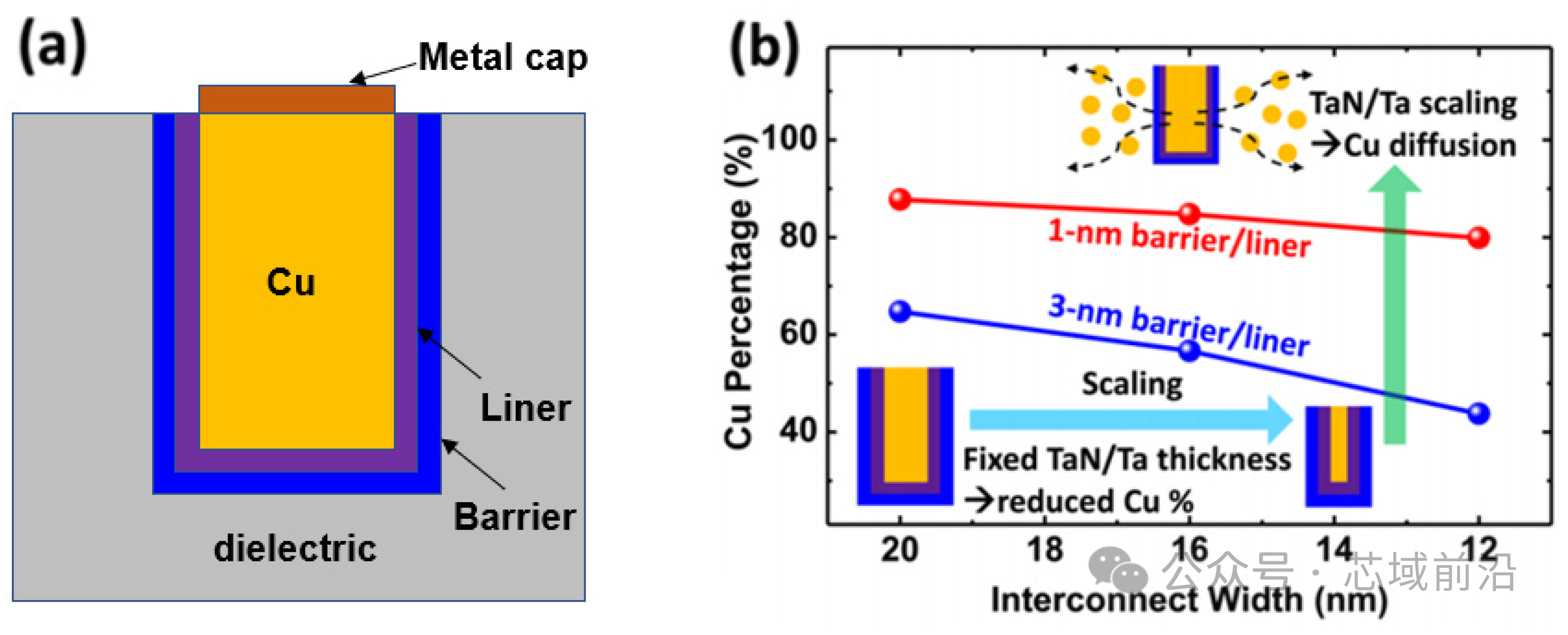

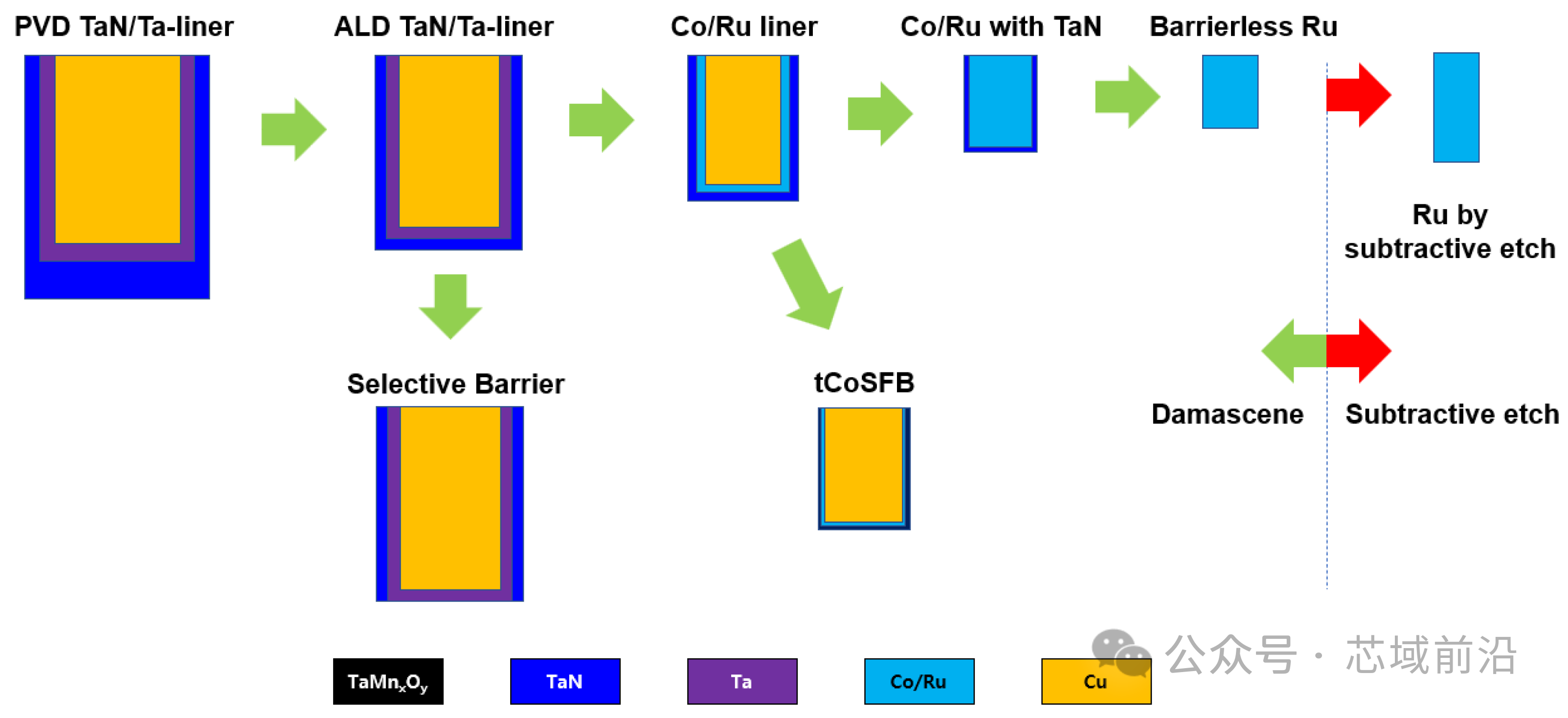

芯域前沿聚焦半导体行业最新动态、技术解析与深度科普,覆盖芯片设计、制造、封测全产业链。 无论您是工程师、投资者还是科技爱好者,在这里都能读懂“中国芯”的崛起逻辑与未来机遇。 硬核内容,深入浅出——与您共赴半导体黄金时代! 同样是“金属+氮化物”,为什么钨接触是Ti/TiN,而铜互连却是TaN/Ta? 01Contact W和Cu金属互联概览 Contact W(Tungsten,钨) 更多出现在 FEOL(Front End Of Line,前段工艺)/MEOL(Middle End Of Line,中段工艺)附近:它像“电梯井/立柱”,把晶体管源漏、栅等器件区引到上方金属层。Cu互连则主要在 BEOL(Back End Of Line,后段工艺) :它像“城市高速路网”,在多层金属中横向连接,典型用DD(Dual Damascene,双镶嵌)工艺成形。这就是为什么你会看到两套非常相似、却又“顺序讲究不一样”的夹层: · 钨接触常见 Ti(Titanium,钛)→TiN(Titanium Nitride,氮化钛)→W(Tungsten,钨) · 铜互连常见 介质→TaN(Tantalum Nitride,氮化钽)→Ta(Tantalum,钽)→Cu(Copper,铜) (很多工程口头会简称“Ta/TaN”,但 经典主流结构更常被文献写作TaN/Ta )  02Contact W的主线:为什么大多是Ti→TiN→W,而不是TiN→Ti? 先用一句话概括: Ti更像“底部修复+粘接+清洁”的活性层,TiN更像“防护服+扩散阻挡+成核底座”的惰性层 。把它们放反,就像“先穿雨衣再贴创可贴”,顺序不对劲。 2.1 Contact W常见工艺链条是怎样的?以典型接触孔为例(不同工艺平台会有差异,但核心模块相似): 1. 刻蚀形成接触孔(到Si或硅化物等) 2. 预清洗/去除残留与氧化(常见干法RF pre-clean等) 3. 沉积衬里/阻挡层:Ti + TiN(或TiN为主的变体) 4. CVD(Chemical Vapor Deposition,化学气相沉积)W填充 5. 刻回/或CMP(Chemical Mechanical Polishing,化学机械抛光)去除多余W 在CVD W阶段,业界常用WF6(Tungsten Hexafluoride,六氟化钨)配合H2或SiH4等还原体系形成钨膜;同时也必须避免WF6直接“咬”到硅界面引发风险。 2.2 Ti与TiN各自“负责什么”? · Ti(Titanium,钛) :更“活”,能作为粘附/反应层,帮助底部界面变干净、更好黏住;同时在狭窄孔底还能起到“吸附/捕获污染”的作用(常被称为getter行为)。 · TiN(Titanium Nitride,氮化钛) :更“稳”,典型用途是 扩散阻挡 与 保护下层免受WF6反应物攻击 ,并且还能作为W的粘附/成核表面、以及后续工艺的“停刻/停抛”辅助层。 所以从“功能贴合对象”来看: · Ti更适合贴着 底部硅/硅化物/底电极 去做界面管理 · TiN更适合在上方做“盾牌”,去面对后续CVD W的含氟化学环境  03Ti/TiN顺序背后真正的“化学战场”:WF6、氟渗透、漏电与“火山口” 如果只讲“Ti是粘、TiN是挡”,那还不够。因为决定顺序的,往往是 谁必须被保护 、以及谁最怕氟 。 3.1 为什么要防WF6“跑下去”?在W的CVD体系里,WF6参与反应并可能在某些条件下与下层发生副反应。行业经验非常明确: · 在W CVD过程中,TiN常被用作阻挡层,去阻止WF6向下扩散到Ti与Si等层 ; · 一旦氟穿透TiN,就可能带来有源区AA(Active Area,有源区)漏电与典型的W-volcano(钨火山口缺陷)等问题。 这也是为什么常见堆叠是 Ti在下、TiN在上 :Ti“干活”但怕被含氟气氛持续攻击;TiN在上面当“防护罩”,尽可能把含氟反应限制在它之上。 3.2 现实世界里,TiN不是“绝对密封”:所以顺序更要稳研究中也讨论过:当TiN层存在微观缺陷/孔道时,WF6可能沿这些通道向下迁移,把F注入到下层Ti附近,造成界面削弱甚至剥离风险(这是很多工艺优化的核心痛点之一)。换句话说:你越清楚“氟渗透的代价”,越能理解为什么要让 TiN尽量直接面对CVD W环境 。也越能理解很多工艺会在TiN沉积、致密化、厚度窗口、以及前清洗上做大量工程折中。  04Cu互连的主线:为什么要TaN/Ta,还要再配Cu种子层? 铜互连的关键词不是“氟”,而是两个更狠的对手: · 1) Cu扩散进介质 (导致可靠性与漏电风险) · 2) 电镀对底层“导电与润湿”的苛刻要求 4.1 Cu为什么离不开“阻挡层+衬里层”?在Cu技术里,阻挡层的核心任务是 防Cu在热预算下向周围介质扩散 ,同时还要对Cu与介质两边都有不错的粘附与稳定性;过去几十年里,Ta/TaN体系被广泛使用来隔离介质与Cu。但Ta/TaN(尤其是更偏阻挡属性的层)往往电阻更高、也不适合直接拿来电镀Cu ,所以工艺上通常还需要先沉积一层Cu seed(铜种子层),再进行ECP/ED(Electrochemical Plating/Deposition,电化学沉积/电镀)填充,最后用CMP把多余铜抛掉,进入下一层循环。 4.2 “Ta/TaN”口头简称背后的事实:很多主流文献写的是TaN/Ta你经常听到工程师说“Ta/TaN barrier”,这是因为现场沟通更关注“这是一套Ta系阻挡/衬里”。但在很多经典论述里, TaN/Ta 被直接点名为“当前主流的双层体系”,并强调 TaN在下更利于与介质黏附 ,而Ta在其上更容易形成低电阻相并服务于Cu界面。  05TaN/Ta顺序的“结构学逻辑”:为什么TaN更常在下面、Ta更常靠近Cu? 如果说Ti/TiN的顺序是“化学反应驱动”(防氟、保界面),那TaN/Ta的顺序更像“材料结构驱动”(相、晶界、电阻、黏附)。 5.1 关键点一:Ta的晶相会“看底层脸色”许多资料提到:Ta在不同条件下可能形成不同晶相,其中一种相电阻更低、另一种相电阻更高;而底层材料会影响Ta优先生长哪种相。经典论述中提到:在TaN下层之上,Ta更倾向生长为低电阻的bcc相;如果Ta直接长在介质上,可能更容易长成高电阻相。这句话翻译成工程语言就是:把TaN放在介质上 ,既能当阻挡,也能当“Ta的良好底座”;把Ta放在更靠近Cu的一侧 ,更利于降低界面电阻、提升Cu成核/润湿与后续电镀一致性。 5.2 关键点二:TaN“更像阻挡层”,Ta“更像衬里层”在大量对比研究中,TaN往往表现出更强的阻挡/热稳定优势,而Ta则更利于较低电阻但热稳定性可能更差;双层堆叠的价值就在于“取长补短”。 用一句好记的比喻: · TaN像“防盗门” :更在意“别让Cu跑出去” · Ta像“门内的地垫” :更在意“让Cu走得顺、接得牢、阻值小” 5.3 把两种顺序写成一张“从下到上”的对照表 · Contact W(Tungsten,钨)接触孔(典型): Si/硅化物 → Ti → TiN → W · Cu互连(典型DD结构): 介质 → TaN → Ta → Cu(再往上还有cap等)  06最后的对比结论:两条顺序“看起来相反”,其实遵循同一条底层原则 6.1 这两套顺序到底“差异在哪”?表面差异: · W接触: 先金属Ti,后氮化物TiN · Cu互连: 先氮化物TaN,后金属Ta (经典写法TaN/Ta) 本质原因: “谁更需要直接贴着底材”、以及“谁更需要面对后续环境”不同 · W接触底部是Si/硅化物,界面“脏/活/敏感”,需要Ti做“界面修复与粘接”;上方要面对含氟体系,TiN必须当盾牌。 · Cu互连底部是介质(尤其低k),首要任务是“阻Cu扩散+对介质黏附”,TaN更胜任;而靠近Cu的一侧需要更低电阻与更好Cu界面,Ta更胜任。 一句话总结:把“更像防护/阻挡的层”放在最该被保护的那一侧;把“更像界面工程/导电润湿的层”放在最需要导电与成核的那一侧。 6.2 下一站:为什么大家都在想“把这层做薄、甚至做没”?随着线宽/孔径继续缩小,阻挡/衬里层占的横截面积越来越“肉疼”,直接推高互连电阻;所以业界趋势之一,是用更高一致性的沉积方式(如ALD(Atomic Layer Deposition,原子层沉积))做更薄的TaN/Ta,或探索Co/Ru等新衬里、甚至“barrierless/自形成阻挡”等路线。 这也解释了一个常见现象:当你看到“TaN/Ta-liner在缩放下的挑战”,不是某个团队没做对,而是物理极限正在逼近;材料与工艺路线必然演化。  |