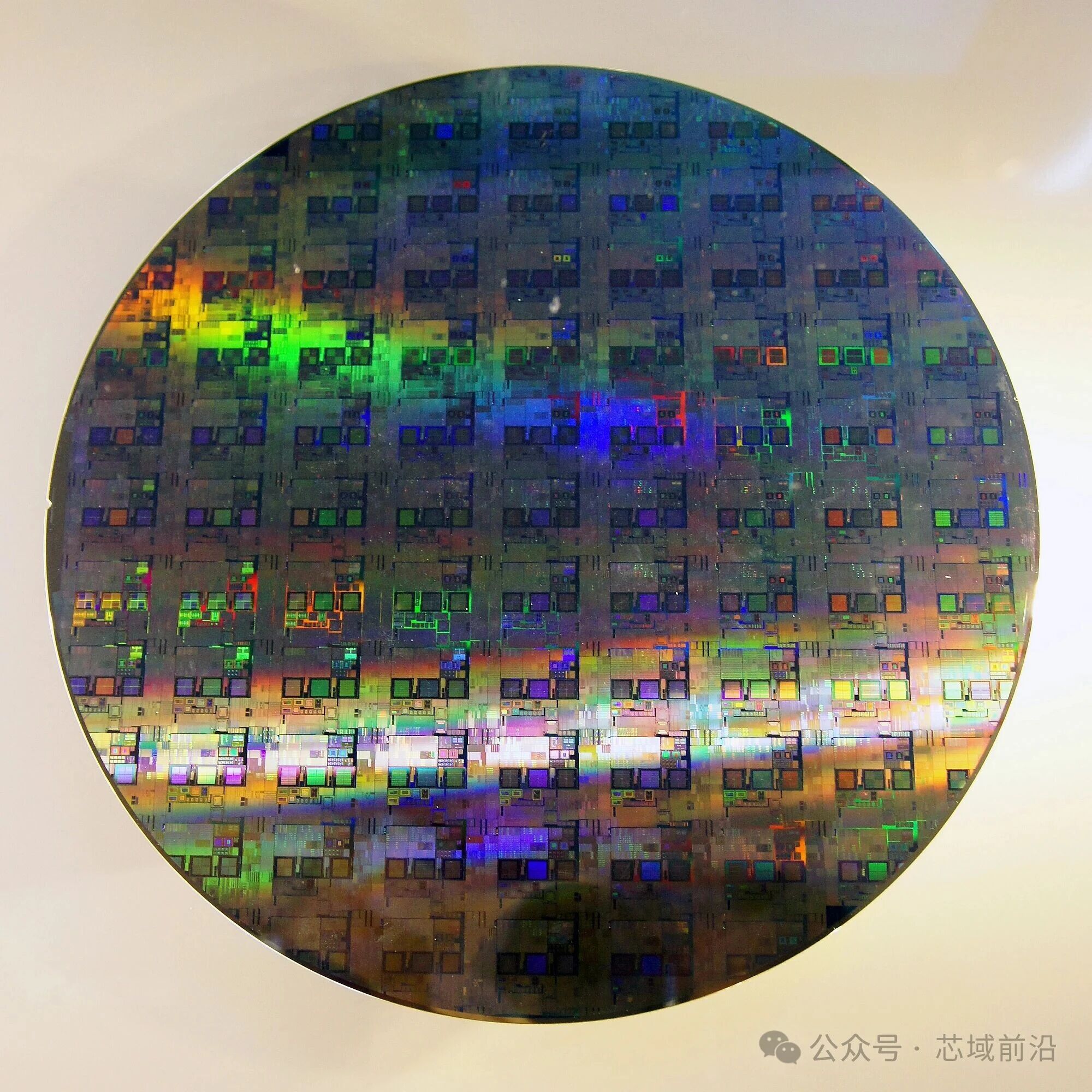

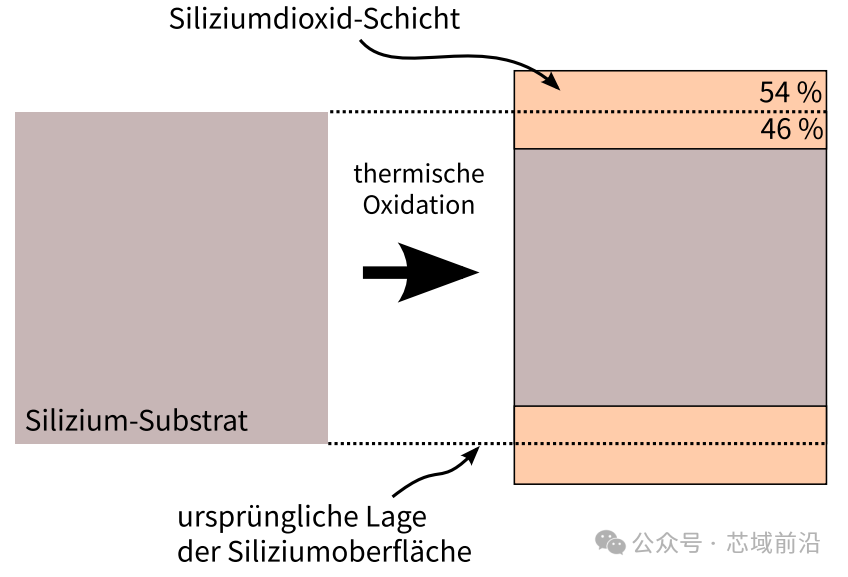

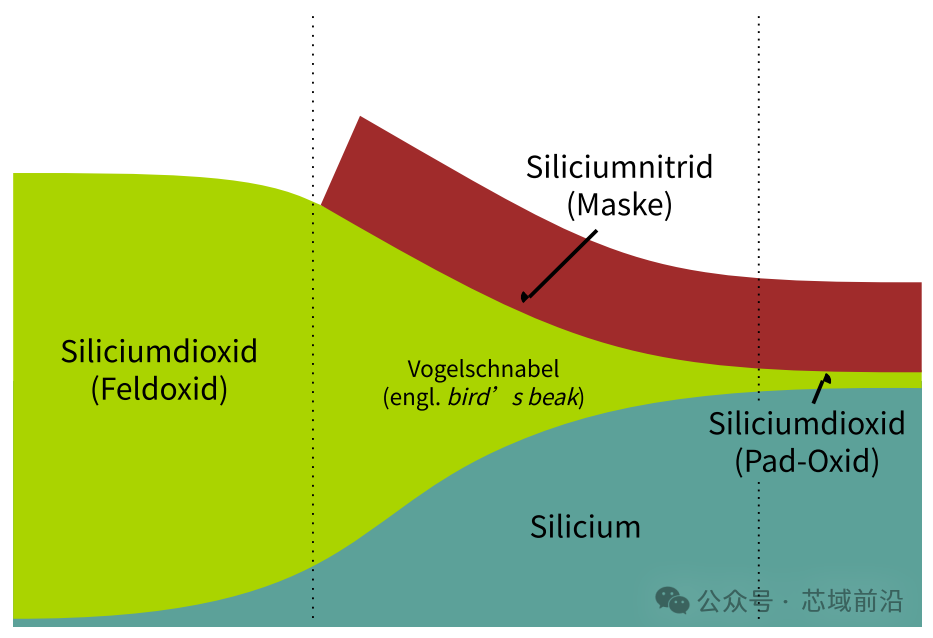

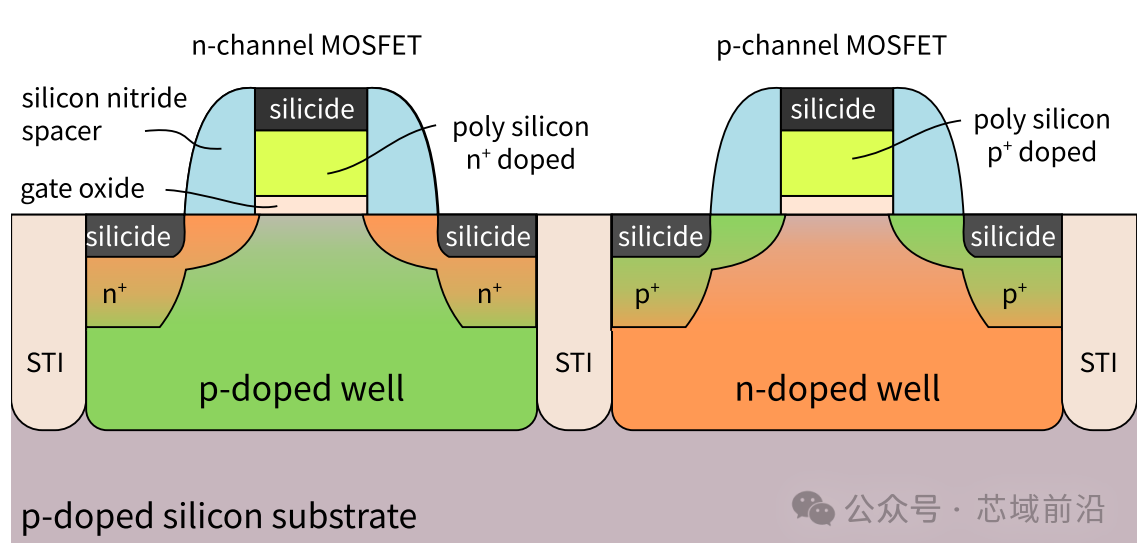

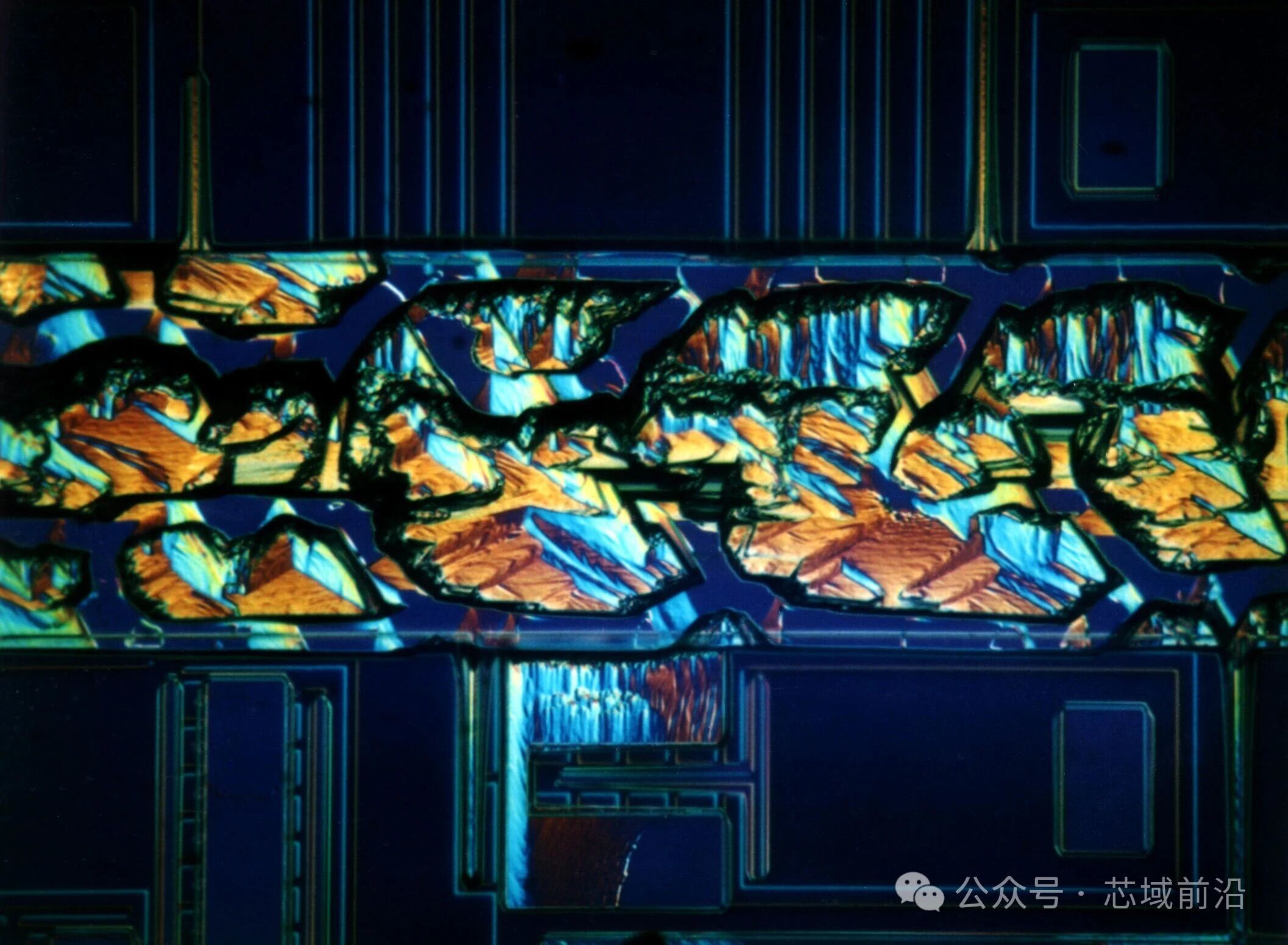

看懂芯片制造第一步:Pad Oxide Growth 为何薄到看不见,却关键到不能错在很多经典 CMOS(Complementary Metal-Oxide-Semiconductor,互补金属氧化物半导体)前道工艺里,AA(Active Area,有源区)模块一上来就要处理隔离问题:哪里将来要做晶体管,哪里必须永久“安静”。 而在这件事真正展开之前,晶圆表面往往先要长出一层很薄、很安静、却极有分量的氧化膜——Pad Oxide(缓冲氧化层)。 在教材化的 STI(Shallow Trench Isolation,浅沟槽隔离)流程中,这一步常被放在前道隔离模块的起点; 在经典 LOCOS(Local Oxidation of Silicon,局部硅氧化)里,它更是整个隔离逻辑的地基。 它不是最终的场氧化层,也不是后面直接决定栅控能力的栅氧,但它决定了后续氮化硅能否“压”得住、隔离结构会不会“长歪”、硅表面会不会提前埋下晶体缺陷。 Pad Oxide 的价值,就在于它把“裸硅表面”从一个容易受伤、容易污染、容易应力集中的对象,变成一个能接住后续复杂工艺冲击的、可控的工程界面。  01Pad Oxide :它不是主角,却是所有主角的垫脚石 Pad Oxide 本质上是一层在硅表面热生长出来的超薄二氧化硅,也就是 SiO2(Silicon Dioxide,二氧化硅)薄膜。 它之所以叫“Pad”,不是因为它厚,而是因为它像一个“缓冲垫”:夹在硅衬底和后续硅氮化物 Si3N4(Silicon Nitride,氮化硅)之间,缓冲机械应力、改善界面状态,并为后续隔离工艺提供更可控的起点。 教学型 STI 流程资料中,Pad Oxide 常见在 15–20 nm 量级;而在工业资料和专利语境里,它普遍被定义为“很薄的一层热氧化硅”,厚度窗口会随着器件结构、氮化硅厚度和隔离方案变化而变化。 Micron 的制造术语资料还特别指出,Pad Oxide 也承担保护硅表面、减少后续注入表面损伤、保持表面清洁并降低缺陷的作用。 理解 Pad Oxide,最重要的一点是把它和“别的薄氧化层”区分开。 它不是 FOX(Field Oxide,场氧化层),因为场氧化层是用来真正完成器件横向隔离的厚氧化层; 它也不是 GOX(Gate Oxide,栅氧化层),因为栅氧直接进入器件电学核心,对界面态、漏电、等效氧化层厚度都有更苛刻的要求。 Pad Oxide 更像一个“工程型界面层”:它的使命是让后面的工艺更稳,而不是单独承担最终器件性能。  02 Pad Oxide 是怎么“长”出来的:不是涂上去,而是从硅里“长”出来 Pad Oxide 的关键词不是“沉积”,而是“热氧化”。 热氧化的本质,是把硅晶圆放到高温氧化环境里,让氧化剂穿过已经形成的氧化层,在 Si/SiO2 界面继续与硅反应,生成新的二氧化硅。 TU Wien 的工艺资料指出,室温下硅表面也会形成大约 1 nm 左右的天然氧化层,但由于氧分子难以在室温继续穿透这层薄氧,氧化会迅速停下来;真正可工程化、可控的氧化,需要高温条件。 热氧化不是单一动作,而是“氧化剂到达表面—穿过氧化层扩散—在界面反应—伴随体积膨胀”这一整套耦合过程。 Deal-Grove(迪尔—格罗夫)模型之所以经典,正因为它把这套扩散与界面反应的基本逻辑讲清楚了。 热氧化又分成 Dry Oxidation(干法氧化)和 Wet Oxidation(湿法氧化)。 干法氧化对应反应 Si + O2 → SiO2,湿法氧化对应反应 Si + 2H2O → SiO2 + 2H2。 MKS 的工艺资料给出的典型条件是:干法氧化常在 900–1200°C 进行,生长速度较慢,大约 14–25 nm/h,通常用于 100 nm 以下、强调致密性和界面质量的薄氧化层;湿法氧化则更快,适合长厚氧。 UTEP 也明确指出,干法氧化虽然慢,但氧化层更高质量、更致密。 对 Pad Oxide 这种“薄而要稳”的工艺对象来说,工艺工程师更关心的是界面质量、厚度精度、应力状态和后续匹配,因此它通常更接近“精细热氧化”,而不是单纯追求速度。 还有一个很容易被忽视的物理事实:热氧化会“吃掉”一部分硅。 生成 SiO2 的过程中,界面位置会移动,氧化层增长伴随着硅被消耗和体积膨胀。 正因为有这一步,后面我们才会看到 LOCOS 里的鸟嘴效应、应力弯曲和边缘形貌变化。 也就是说,Pad Oxide Growth(Pad Oxide Growth,缓冲氧化层生长)并不是“在表面盖一层膜”这么简单,而是从材料、界面、应力到几何形貌都会一起变化的起跑动作。  03 为什么第一步不是先上氮化硅,而是先长 Pad Oxide 真正让 Pad Oxide 成为“第一步关键层”的,不是它会不会绝缘,而是它能不能“接住应力”。 在经典隔离流程中,后面往往要沉积一层较硬的氮化硅作为氧化阻挡层或 CMP(Chemical Mechanical Planarization,化学机械平坦化)停层。 问题在于,氮化硅本身机械应力强,如果直接压在硅上,高温过程中很容易诱发位错、堆垛层错等晶体损伤。 MKS、Micron 和多份大学工艺讲义都强调,Pad Oxide 的核心任务之一,就是在硅和氮化硅之间提供一个应力缓冲界面,减少应力诱发的缺陷与失配。 换句话说,Pad Oxide 的第一价值不是“挡”,而是“缓”。 但工程上真正难的地方,是它不能无限厚。 因为 Stanford 关于 LOCOS 的课程资料明确指出,Pad Oxide 变厚,会给氧化剂提供更宽的横向扩散通道,从而更容易在氮化硅掩膜下侧向生长,导致更严重的 bird’s beak(Bird’s Beak,鸟嘴效应)。 也就是说,这一层氧化膜越厚,缓冲应力越有利;可它越厚,隔离边界越容易被“吃”进去。 有经验的工艺工程师做 Pad Oxide,从来不是在追求“越稳越厚”,而是在做一个三方平衡:既不能薄到失去缓冲能力,也不能厚到把后面几何尺寸拖垮。 这也是 Pad Oxide 最像半导体制造本质的地方:它看似只是一层膜,实际上是一场多目标优化。 你要的是界面质量、应力释放、尺寸控制、后续可刻蚀性、与氮化硅及清洗流程的兼容性,而不是单点最优。 真正成熟的产线,最强的不是能把膜长出来,而是能把这层膜稳定地长在“刚刚好”的位置上。  04Pad Oxide 在 LOCOS 里扮演什么角色:一边缓冲,一边埋下“鸟嘴”的代价 说 Pad Oxide,绕不开 LOCOS。 TU Wien 的隔离工艺资料把经典流程讲得很直接:先在晶圆上长一层很薄的 Pad Oxide,再沉积氮化硅,完成光刻和开窗后,在暴露的硅区热生长厚场氧化层,最后去掉氮化硅。 LOCOS 的优点很明显:隔离氧化层本身就是热生长出来的,质量高、界面好、流程逻辑也相对直观。 它的问题也同样典型:氧化在开口区向下长,也会在掩膜边缘向侧面钻,最后形成“鸟嘴”,侵占原本属于有源区的尺寸预算。 而 Pad Oxide 恰恰处在这个矛盾中心。 没有它,氮化硅应力太狠,晶圆表面容易伤;有了它,侧向扩散路径又会更“顺”。 Stanford 的资料给出了一个非常有启发性的工程结论:Pad Oxide 厚度减小,鸟嘴通常会缩短,但应力问题会加剧;Pad Oxide 厚度增大,鸟嘴则更容易变长。 于是,Pad Oxide 在 LOCOS 里从来不是“加不加”的问题,而是“加多少、配多厚的氮化硅、配什么氧化温度与时间”的组合问题。 LOCOS 还有一个经典缺陷叫 Kooi effect(白带效应/白丝带效应)。 Stanford 课程资料指出,它来自氮化硅掩膜边缘下方硅表面的局部氮化,后果是后续局部栅氧可能变薄,最终影响器件可靠性。 工艺上常通过额外氧化和刻蚀,把这层局部形成的不利氮化层处理掉。 注意,这里再一次说明了 Pad Oxide 的本质:它不是一次性完成某个“终局电学功能”,而是为了让整个隔离模块在高温、应力、边缘效应与后续制程中不出大问题。  05 到了 STI 时代,Pad Oxide 为什么还没退场 进入深亚微米以后,LOCOS 最大的问题越来越难接受:鸟嘴会吃掉横向尺寸,表面形貌也不够理想。 TU Wien 明确指出,STI 因为几乎没有传统 LOCOS 那种侧向场氧侵占,更适合亚 0.5 μm 技术节点的高密度隔离。 可这并不意味着 Pad Oxide 从历史舞台消失了。 恰恰相反,很多 STI 流程一开始仍然是“Pad Oxide Growth + Nitride Deposition(氮化硅沉积)”,只是它的角色从“配合 LOCOS 生长场氧”转向了“给沟槽隔离流程打底”。 在典型 STI 流程里,Pad Oxide 先作为缓冲层垫在硅和氮化硅之间,随后进行有源区光刻、沟槽刻蚀、去胶、再氧化、角部圆化、沟槽填充、CMP 停在氮化硅上、最后去掉氮化硅与 Pad Oxide。 MKS 的 CMOS 工艺页面和教学讲义都提到,沟槽刻蚀会伤害暴露的硅表面,因此还会再长一层 liner oxide(衬里氧化层/侧壁氧化层),用来修复刻蚀损伤、圆化沟槽拐角。 这里一定要分清:Pad Oxide 是沟槽刻蚀前的“底层缓冲氧化”,liner oxide 是沟槽刻蚀后的“修复型再氧化层”,两者都薄,但使命不同。 也正因为如此,Pad Oxide 并不是“老工艺遗产”。 它代表的是一种直到今天仍然成立的工程逻辑:在强应力膜层、剧烈刻蚀、后续高温步骤真正开始前,先用一层受控的热氧化界面把表面状态、应力传递和后续可制造性稳住。 节点在变、隔离形式在变,但“先把界面做好”这条原则,一直没变。  06只有十几纳米,为什么 Pad Oxide 这么难做稳 Pad Oxide 最难的地方,恰恰在于它太薄。 薄到什么程度? 薄到晶圆前处理有没有把天然氧化层清干净、表面是不是处于 H-passivated surface(氢钝化表面)状态、炉管里氧化气氛和升降温节奏是不是稳定,都会直接体现在厚度均匀性、界面态、固定电荷甚至后续应力上。 MKS 指出,优质热氧化层之所以被工业长期偏爱,原因之一就是它在氢钝化硅表面上能形成非常规则、稳定、可重复的 Si/SiO2 界面; 而 Chris Mack 的氧化流程讲义则强调,一个完整热氧化周期通常包含低应力推片/升温、干法或湿法氧化、N2(Nitrogen,氮气)退火以及低应力降温,其中氮气退火有助于降低表面态。 再往深一点看,Pad Oxide 的控制不是只看“厚度有没有到”。 Micron 的资料提到,Fab(Fabrication Facility,晶圆制造厂)的 Metrology(量测)环节不仅要测膜厚,也会关注应力等指标。 因为对 Pad Oxide 来说,真正的良率语言从来不是单一纳米数值,而是“厚度均匀不均匀、界面干净不干净、应力有没有压到后续窗口里”。 同样是薄氧化层,Pad Oxide、Screen Oxide(屏蔽氧化层)和 Sacrificial Oxide(牺牲氧化层)也不能混为一谈: 后两者更常用于减轻注入损伤、降低沟道效应或消耗表面受损层,而 Pad Oxide 更强调隔离模块中硅/氮化硅之间的缓冲与保护。 所以,Pad Oxide 的难,不在于“能不能长出 SiO2”,而在于“能不能把一层极薄的 SiO2 长成后面几十道工艺都愿意接受的样子”。 它要够薄,才能不吃掉版图;它要够稳,才能接住氮化硅;它要够干净,才能不给后面的栅氧、隔离和注入埋雷。 这就是为什么在真正的制造线上,越是看起来不起眼的前几步,越容易成为整条制程稳定性的风向标。  07结语 Pad Oxide 这一步,最能体现半导体制造的真实气质:真正决定成败的,往往不是最“炫”的技术名词,而是最早、最薄、最基础的那层界面。 它一头连着硅表面的材料学,一头连着氮化硅、LOCOS、STI、刻蚀、退火和良率;它看起来像配角,实际上却在第一分钟就把整场工艺的脾气定下来了。 理解 Pad Oxide,你就真正开始理解半导体制造不是“把图形印上去”,而是在一层一层、一步一步地管理材料、应力、界面与缺陷。 |