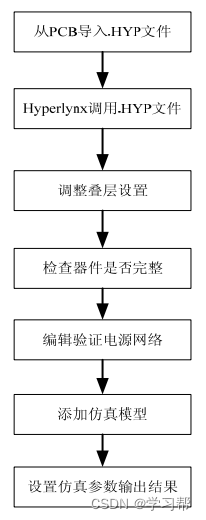

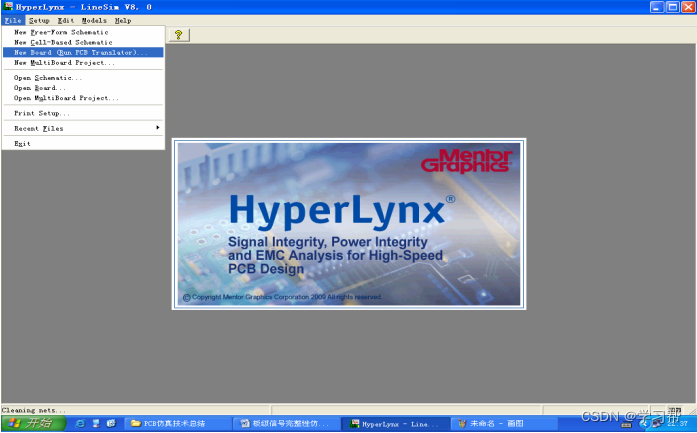

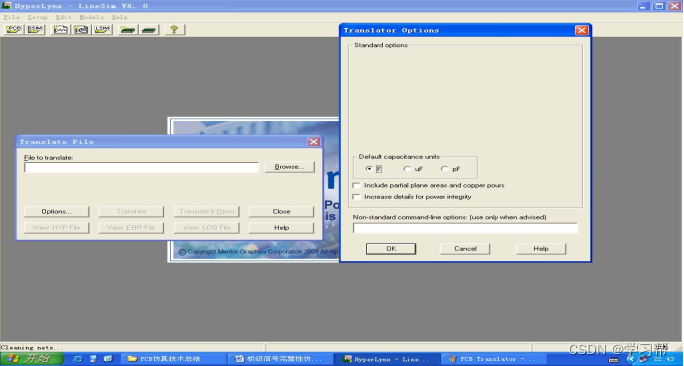

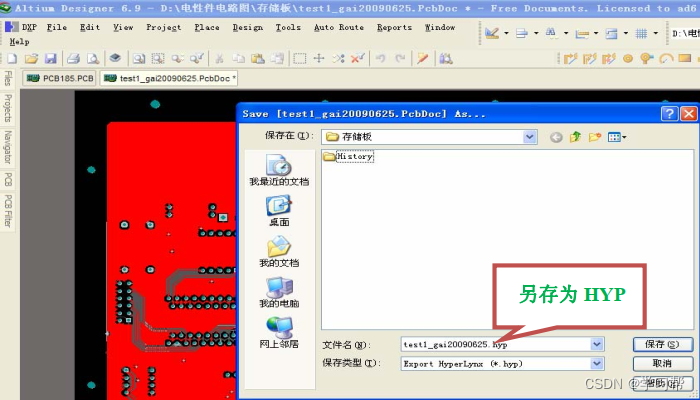

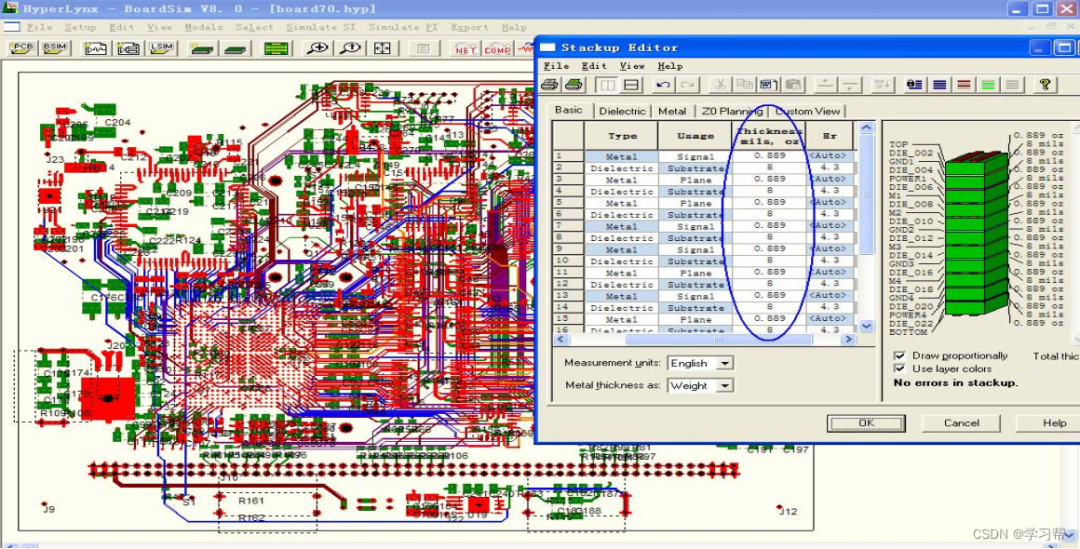

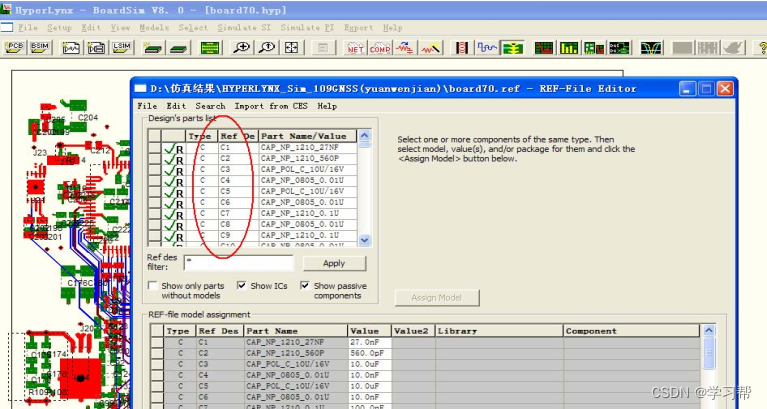

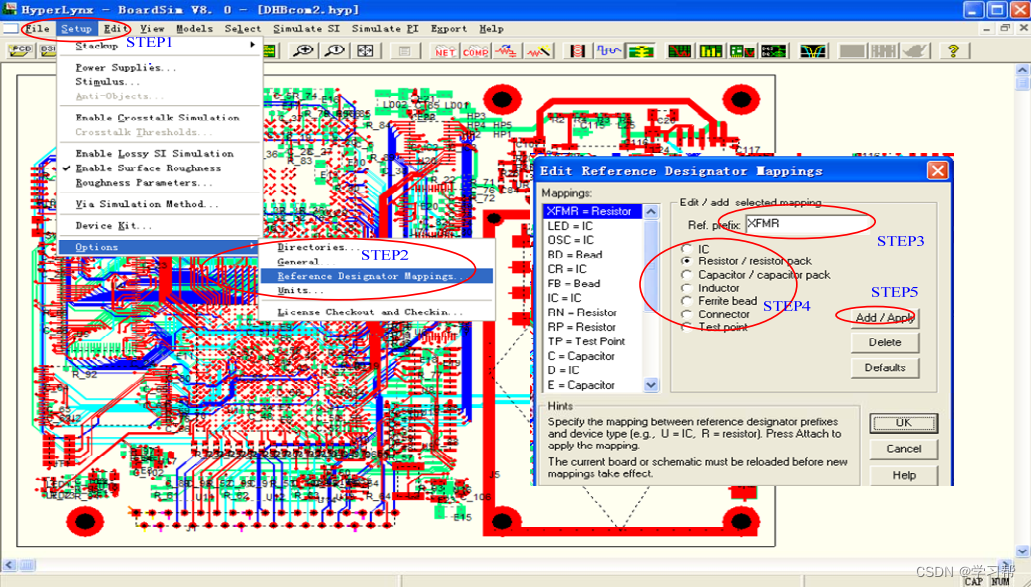

1 概述随着 IC 芯片时钟信号频率的增加、信号边沿的减小,由此带来的信号完整性问题已经越来越凸显。PCB 信号完整性问题主要包括由阻抗不匹配引起的信号过冲、相邻不同网络之间由于各种耦合产生的信号串扰、有损传输线造成的信号边沿退化等问题。信号完整性问题不仅会造成电路功能错误,也会造成各种电磁兼容问题。 在高速 PCB 设计过程中,为了能够使 PCB 一次设计成功的同时又能确保板级辐射发射不超标,板级信号完整性仿真分析已经成为一种重要不可缺少的手段。信号完整性仿真的模型主要有 IBIS 模型、 SPICE 模型、 VHDL_AMS 模型、Verilog_AMS 等等。其中 IBIS 模型是 PCB 设计业界中最常用的、最流行的信号完整性仿真模型。板级信号完整性仿真工具有 Mentor Graphics 的 Hyperlynx、Cadence 公司的 SPECCTRAQuest 等等。下面以 Hyperlynx 为例说明板级信号完整性仿真的方法及具体过程。  图 1 基于 Hyperlynx 的板级 SI 仿真流程图 2 生成*.HYP 格式文件 Mentor Graphics 的 Hyperlynx 软件可以支持当前较流性的 PCB 设计软件生成的 PCB 文件格式,不仅能和 Mentor 公司自己的 Expedition、 PADS、 BoardStation 等 PCB 设计软件进行无缝链接,还可以和其他 PCB 设计软件,比如Altium 公司的 Protel(高版本为 designer)、 Cadence 公司的 Allegro 软件及株式会社公司的 Zuken 软件通过接口进行链接。一般得到*.HYP 格式文件有两种方法:第一种是利用 PCB 设计软件本身自带的和第三方 EDA 软件的接口(这里是指 PCB 设计软件和 Mentor 公司的 Hyperlynx 软件之间的借口),比如在 Protel软件中,其 PCB 文件本身就可以导出 Hyperlynx 可以读取的.HYP 格式的文件;第二种是利用 Hyperlynx 软件自带的 PCB 转换工具,将目标 PCB 文件直接转换成仿真所需的.HYP 文件, Hyperlynx8.0 支持转换的 PCB 格式有以下几种:Cadence 公司的*.DSN、 *.brd 文件、 Accel 公司的*.PCB 文件、以及株式会社的*.PCF 文件等。图 2、图 3 是使用 Hyperlynx 自带的 PCB 转换工具来生成.HYP 文件;图 4则是在第三方 EDA 软件 Protel 中生成.HYP 文件。  图 2 Hyperlynx 的 PCB translator 菜单  图 3 PCB translator 选项设置  图 4 Protel 导出 HYP 格式文件 注意事项:在对 PCB 文件进行 HYP 格式转换前要指定 PCB 文件中的各平面层(如果不指定 Plane 面则转换时会报错),且 Plane 层的命名要符合一般通用规则(比如电源层名字使用关键字 VCC 开头,地层名字使用 GND 关键字开头等);无源器件如电阻、电容、电感器以及磁珠等的取值信息尽量详细。 3 导入*.HYP 格式文件 设置叠层 当导入一个 HYP 文件后首先要做的就是要对 PCB 的叠层作修改, 如介质厚度、平面层厚度、介质的介电常数及特征阻抗等等,使其符合实际的 PCB 加工情况。HyperLynx 对由 PCB 文件转换导入的 HYP 文件有一个默认的叠层设置,这个默认值一般不能直接使用,需作修改。  图 5 调整叠层设置 4 检查元器件的命名 打开 HYP 文件后要先检查 PCB 中的元器件是否都已完全无误的导入到 HYP文件中了,检查元器件的标号是否缺失、完整,如图 6 所示。  图 6 检查元器件编号 如果有部分元器件因为标号命名方式不符合一般命名规则而未被软件所识别,则可修改软件中的器件命名规则方式,从而使得器件能够被软件所识别。 点击SETUPÆOPTIONÆREFERENCE DESIGNATOR MAPPING 选项,即弹出器件标号映射修改对话框,如图 7。在对话框中选择所要映射器件标号的首字母以及将该器件所要映射的类别后,点击 Add 按钮即可新建一标号映射规则。  图 7 修改元器件标号映射规则 |