|

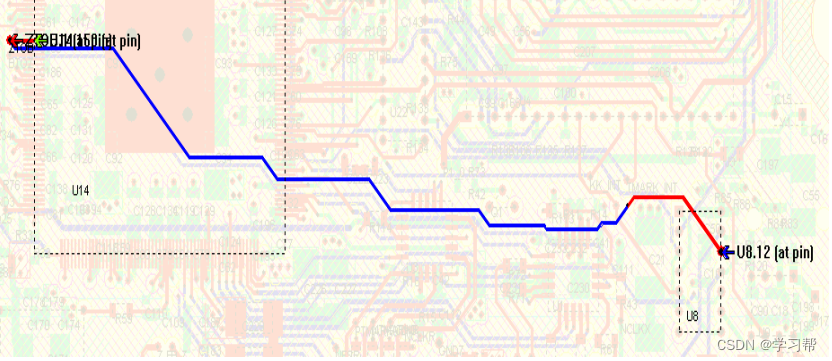

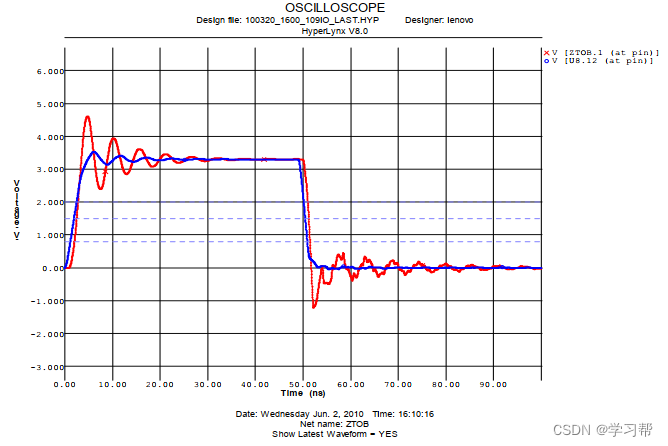

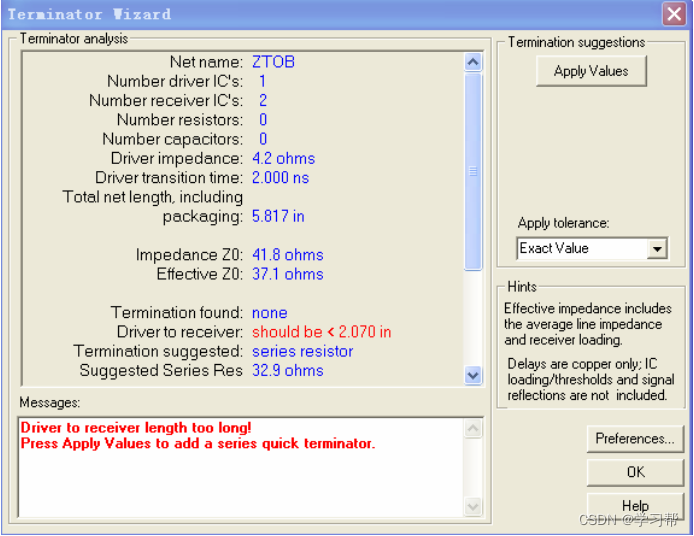

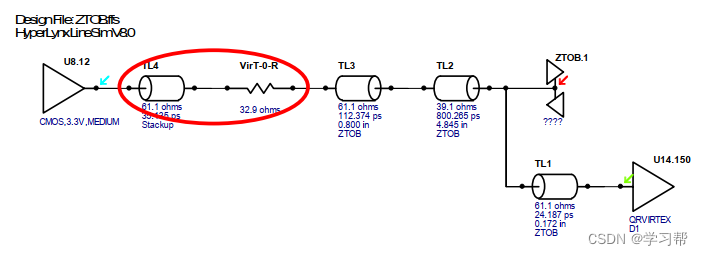

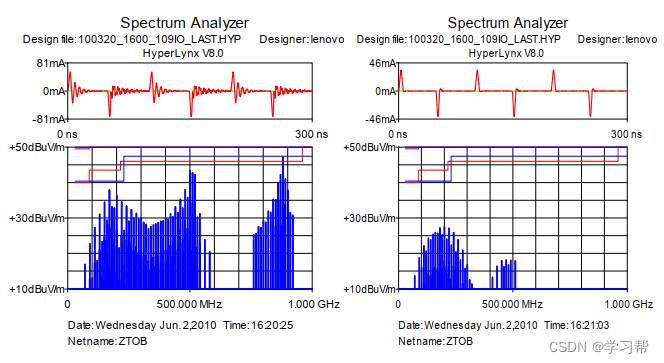

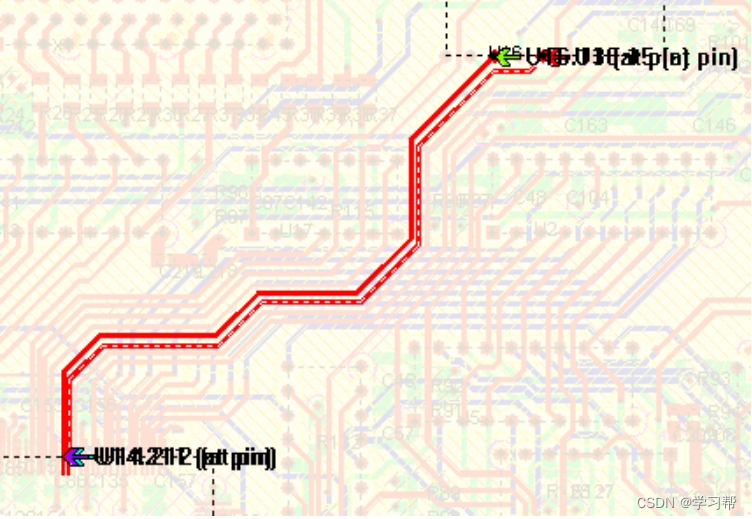

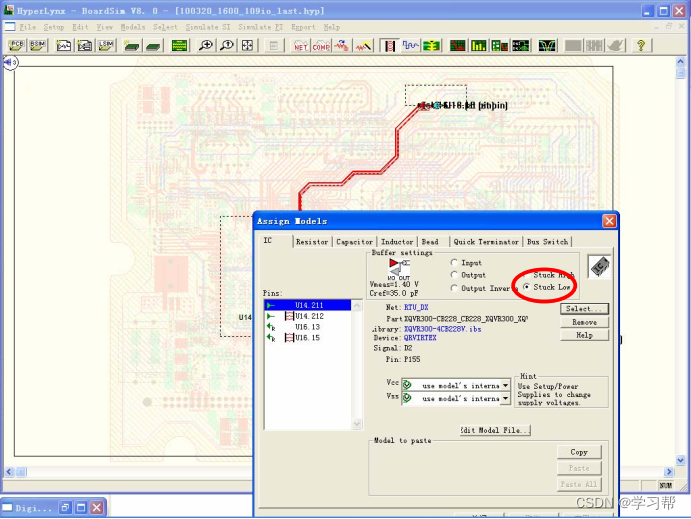

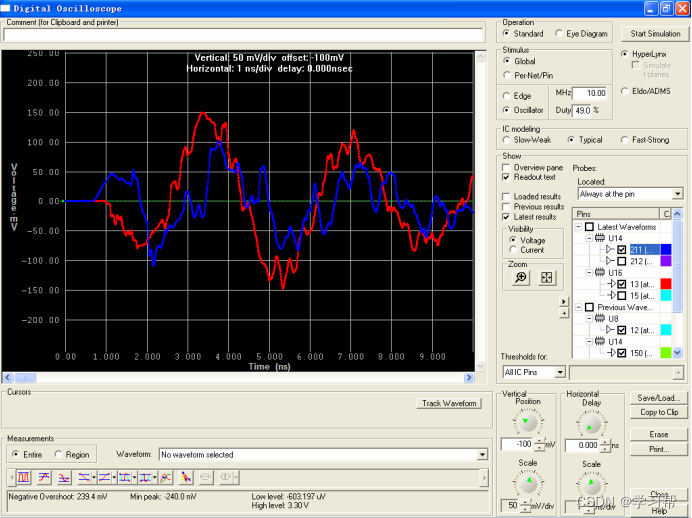

12 仿真分析结果 ZTOB 逻辑信号过冲分析 图 52 所示是 FPGA( U14)和逻辑芯片( U8)之间的互联网络( ZTOB),信号由逻辑器件输出至 FPGA。将 U8.12 设置为驱动输出, U14.150 设置为接收器输入端。  图 52 ZTOB 信号网络 点击菜单 EXPORTÆNET TOÆFREE FORM SCHEMATIC, 得到如图 53 所示的模型。  图 53 ZTOB 信号网络导出模型 点击 SI 交互式仿真快捷按钮 ,仿真类型设置振荡模式,频率为 10MHz。图 54 是 ZTOB 信号仿真结果,其中红色的是驱动输出端信号,蓝色是 FPGA 接收端信号。由图可以明显看出上升沿过冲为 1.3V,下降沿过冲为 1.19V,信号质量很差,过冲很严重。  图 54 ZTOB 信号过冲 针对信号过冲较为严重情况,采取端接措施进行改进。利用终端向导,可以发现,驱动端到接收端建议的走线长度应该小于 2in,或者串入 32 欧姆左右的电阻,如图 55 所示。  图 55 端接向导 改进后的 PCB 布线网络导出模型如图 56 所示。  图 56 端接改进示意图 改进后的上升沿过冲为76.83mV,下降沿过冲为 239.4mV;但时钟信号的边沿变缓了。  图 57 采取端接措施后 下图为采取端接措施前、后辐射频谱对比情况,由图可以明显看到端接后的辐射大大减小了。  图 58 端接为前的辐射频谱 图 59 端接后的辐射频谱 RTU_DX 与 SELF_CLKX 网络间串扰分析 下图是相邻较近的两个信号网络。将 RTU_DX 信号网络设置为受害网络并选中,然后点击按钮,将在 RTU_DX 信号网络周围出现攻击线(虚线显示,即 SELF_CLKX 网络)。  图60 相互干扰的两个网络 点击 COMP 按钮 ,将受害线上的驱动输出端管脚设置为 Stuck Low 状态,接收端管脚设置为输入状态;将攻击线上的器件管脚设置为正常工作状态,具体设置如图 61 所示。 图 62 是受害线上的串扰电压值,由图观察可知最大串扰噪声达到 150mV左右。  图 61 串扰仿真设置  图 62 串扰仿真结果 |