|

3.3基于非扫描设计的低功耗DFT方法

DFT的实现方法可以分为两类,一种是基于扫描的设计,另一种是基于非扫描的设计。

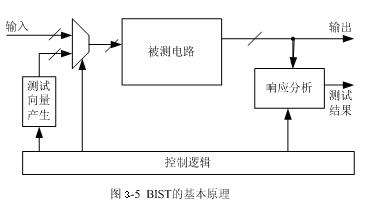

基于扫描的设计是将ATPG首先加载到扫描链上,然后捕获测试响应进行分析诊断,非扫描设计则是将测试向量直接施加在被测试电路的输入端,然后分析响应。这里,我们选择非扫描BIST为例来说明非扫描设计低功耗的基本方法。对于基于扫描设计的低功耗问题,可参考上一节。

非扫描设计的DFT低功耗方法主要包括:抑制翻转和禁止无用的测试矢量加到CUT(Circuit Under Test,被测电路)的输入端[24];采用双速反馈移位寄存器产生低功耗的ATPG(Automatic Test Pattern Generation)[25],采用分布式BIST[26],对并行BIST进行调度[27],设计新的扫描路径结构[28]和改进扫描单元[24],修改时钟树[29],使用格雷(Golomb)码压缩测试向量[30],等等。

低功耗的关键问题是在保证较高的故障覆盖率的前提下,减少电路中各处节点的翻转次数。减少总的翻转测试,既可以减少测试带来的总功耗,又可以缩短测试时间;减少多个节点同时翻转的次数,则可以有效地降低峰值功耗;另外,还要尽量减少测试向量产生电路本身的功耗。

3.3.1 对测试向量处理得到低功耗ATPG

处理测试向量,既可以在测试向量产生过程之中进行,也可以在测试向量产生之后进行优化。不管采用什么方法,基本目的都是使得相邻向量之间的相关性尽可能大,最好是单跳变的。

3.3.1.1优化种子

用LFSR产生测试向量时,WSA(Weighted Switching Activity)与种子的选取有很强的相关性,而对于本原多项式的敏感度则相对较低[24],因此选取合适的种子是减小WSA的关键所在。由于有效测试矢量分布不均匀,使得不同的种子产生的测试矢量具有不同的故障覆盖率,也具有不同的功耗。文献[31]提出了一种基于模拟退火算法的选取种子近似最优解的方法。

3.3.1.2屏蔽无用的测试向量

由于LFSR(Linear Feedback Shift Register)产生的测试向量序列中,并不是所有的测试矢量都对故障覆盖率起作用,那些对测试覆盖率没有“贡献”的测试矢量施加到CUT的输入端,造成了不必要的功耗。因此可以对测试矢量进行分组,避免那些无用的测试矢量进入CUT。文献[32]中采用了解码电路和D触发器来控制测试矢量进入CUT,从而大大减少了WSA,同时其面积开销也可以忽略。

3.3.1.3准单跳变测试向量生成

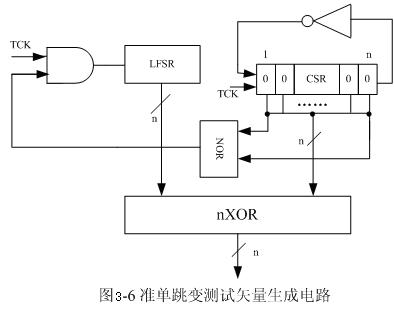

这种方法目的在于将测试向量有序化,当这些向量按照一定的顺序施加到被测电路上时,可以有效的减少CUT内部节点的翻转概率。图3-6给出了这种方法的一个示例。只有当移位寄存器CSR的所有位都是“0”的时候,LFSR的时钟才有效,此时产生一个伪随机测试向量,也就是说,LFSR的工作频率实质上是1/n。n位移位寄存器加上一个非门,产生单跳变序列,该单跳变序列与任意一个由LFSR生成的测试序列进行异或,均可以得到一个单跳变序列,将该单跳变序列施加到CUT输入端,可以有效地降低CUT的翻转次数。

该方法可以有效地降低平均测试功耗和总测试功耗,不足之处是由此带来较大的面积开销问题[33]。

3.3.2降低CUT输入端的活动性

CUT上的测试功耗主要来自动态测试功耗。因此,降低CUT输入端子上的测试激励的变化率,可以有效地降低测试功耗。

3.3.2.1对CUT输入端子进行分组

当测试向量施加到CUT的输入端子上时,不同的输入端子引起CUT内部节点翻转的次数是不同的。有的输入端子引起的翻转次数较多,而另一些则引起的翻转次数较少。称前者为“重翻输入端”(有较高的活动性),后者为“轻翻输入端”(有较低的活动性)。若使得施加到重翻输入端上的测试向量部分保持较低的翻转速率,则可以有效地降低CUT内总的翻转次数。

在文献[29]中提出的DS-LFSR(Dual_Speed Linear Feedback Shift Register)使用两个LFSR,一个低速的LFSR和一个常速的LFSR,它们一起构成TPG(Test Pattern Generator),对于那些重翻输入端由慢速LFSR驱动,轻翻输入端则采用常速LFSR驱动。总的看来,CUT输入端子上的测试信号的活动性就被大大降低了,从而就有效的降低了总测试功耗和平均测试功耗。

在另外的文献[34]中,则是采用与门阵列实现该方法。采用位数较少的LFSR直接驱动活动性较低的CUT输入端子;LFSR产生的测试向量经过与门阵列施加到活动性较高的输入端子上。由于与门具有低电平封门特性,总的来看,CUT的输入端子可以获得活动性较低的测试向量。

该方法在大大降低总测试功耗和平均测试功耗的同时,和标准的LFSR测试电路的故障覆盖率相差无几,不足之处是峰值功耗没有得到降低,面积代价稍大。

3.3.2.2采用门控时钟

基本做法是:将系统时钟树一分为二,每个时钟都是系统时钟的一半,它们有固定的相位关系。TPG中的D触发器被分为两组,分别被两个“半速时钟”驱动,从而有效地降低了CUT输入端测试信号的活动性,达到了降低功耗的目的[29]。

这种方法不仅可以降低测试平均功耗、峰值功耗和总测试功耗,而且有效的降低了TPG本身的功耗,由于改进电路而带来的面积增加几乎可以忽略。

3.3.3采用混合模式测试向量

以上所谈到的方法主要基于伪随机测试向量的产生办法。在采用那些方案时,虽然不需要存储空间来存储测试向量,但因为测试时间较长,也会带来较大的总测试功耗。另外,往往不能达到100%的故障覆盖率。

采用确定性矢量的测量方法虽然可以有较低的功耗,但是由于需要很多的存储空间来存储测试向量,所以需要大量增加芯片的面积。在芯片中增加如此巨大的面积是不现实的,所以此种方法主要适用于基于扫描的测试,将大量的测试矢量存储在ATE的存储器中。

将确定性测试矢量法和伪随机性测试矢量法相结合,产生了混合式测试向量法。在这种方法中,用一组有限个数的伪随机测试矢量来覆盖容易检测到的故障,而另外一些不容易被覆盖到的故障则用一组确定性向量来覆盖。该种测试方法可以达到100%的故障覆盖率。可以通过折中确定性测试矢量和伪随机测试矢量的个数来达到最大限度的降低总测试功耗的目的[35-38]。上面所谈到的多种测试方法,也适用于本方法中的伪随机测试法。

3.4本章小结

本章首先简单的分析了测试模式下功耗过高的主要原因,然后针对两种主流DFT实现手段(基于扫描的设计和基于非扫描的设计)的低功耗DFT问题进行了讨论。它们共同的目的就是减少电路节点的翻转次数,降低峰值功耗、平均功耗和总测试功耗,从而增强产品的低功耗DFT特性和市场竞争力。

|