2.3.4.1如何处理不可测试的故障

解决上述不可测试故障的方法有多种,针对图4-13,此处给出常用的两种。

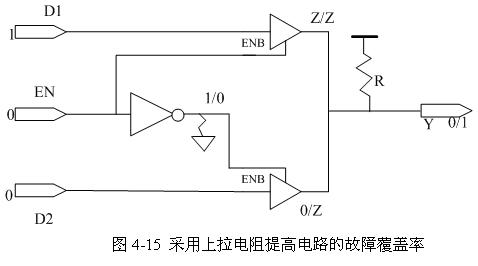

方法1:增加一个上拉电阻(如图4-15)。通过上拉电阻,一个悬空的总线可以被上拉到一个弱1。这样图4-13中所示的SA0故障就可以用通常的方法进行测试了。采用这种方法的缺陷是引入了静态功耗。与方法2相比,优点在于采用的测试向量个数较少。

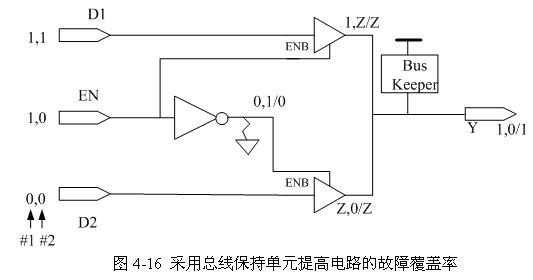

方法二:增加一个总线保持单元(Bus Keeper)

采用这种方法,需要两个连续的测试向量实现图4-13中所示的SA0故障诊断。第一个测试向量将一个初始数据打入总线数据保持单元(Bus Keeper),用来覆盖第二个测试向量在输出端产生的高阻值Z。在图4-16中,用第一个测试向量110将Bus

Keeper置为弱1,当第二个测试向量施加到输入端时,如果上述SA0故障存在,则由Bus Keeper提供的1作为输出,如果电路不存在此故障,则输出0电平。采用这种方法的缺陷是,增加了ATPG的数量,好处是故障覆盖率较高。

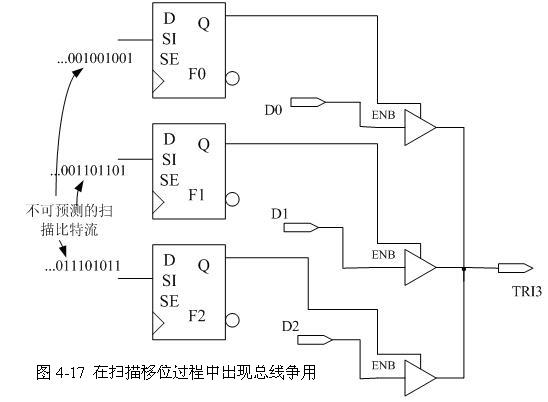

2.3.4.2在扫描移位过程中出现的总线争用(Contention)

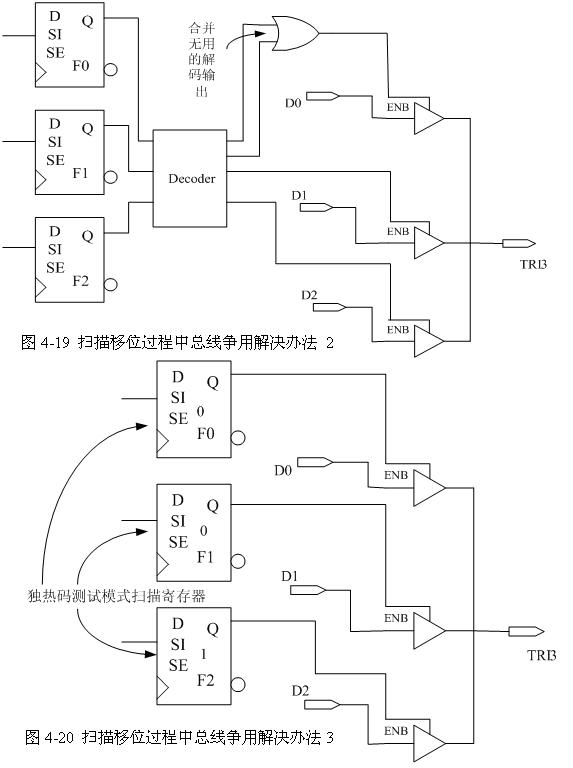

由于一些扫描移位寄存器Q端与三态输出的使能端相连,造成三态输出总线上的输出信号会不断发生变化,如图4-17所示。在通常情况下,这些扫描移位寄存器中的数据往往是不可预测的。因此,三态输出端的输出电流会对与之相连的电路产生影响。虽然这种现象不会影响故障覆盖率,但是潜在着损坏器件的危险。解决这种问题的办法有三种,分别如图4-18、4-19、4-20所示。

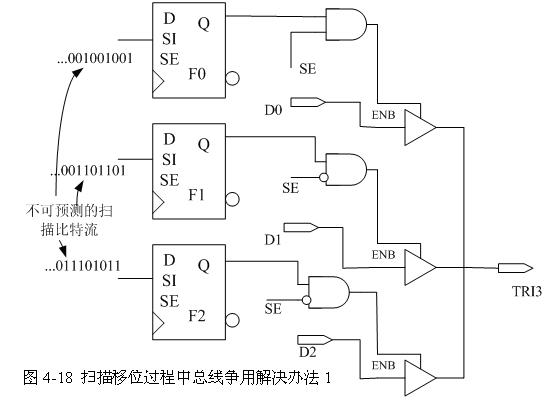

方法1(图4-18):增加一些控制逻辑。在图中使用的是一些与门。通过使用扫描使能信号SE,使得与输出三态引脚相连的三态缓冲器中只有一个可以将数据送出,其它三态缓冲器全部为高阻状态。因此,可以有效的避免测试过程中损坏器件。

方法2(图4-19):引入一个解码器。该解码器可以解码三态使能端,使得在任一时刻,只有一个三态缓冲器是导通状态,其它缓冲器均为高阻状态。另外,也可以采用类似于方法1的办法,让所有的三态缓冲器在扫描移位过程中都处于高阻状态。

方法3(图4-20):该种方法是采用独热码。在任一时刻,只有一个三态缓冲器是导通状态,其它缓冲器均为高阻状态。显然,采用这种测试向量,不一定适用于被测试电路。

2.3.4.3在捕获响应的时候出现的总线争用(Contention)

如何避免在捕获响应的时候出现总线争用?可以采取以下四种方法:

(1) 使ATPG工具丢弃所有导致总线争用的所有测试向量;

(2) 在图4-18所示的方法中,使用ASIC_TEST引脚取代SE引脚来控制三态使能。虽然这样可以避免总线争用,但是会降低故障覆盖率(因为ASIC_TEST在测试响应捕获期间为高电平,在它封锁的与门输入端的固定型故障将无法传送到输出端);

(3) 通过一个独热码测试模式寄存器来控制三态使能;

(4) 全解码三态使能(不需要检查总线争用)。

|