|

工程会接触DFT。需要了解DFT知识,但不需要深入。

三种基本的测试(概念来自参考文档):

1. 边界扫描测试;boundary scan test。测试目标是IO-PAD,利用jtag接口互连以方便测试。(jtag接口,实现不同芯片之间的互连。这样可以形成整个系统的可测试性设计。)

2. 内建自测试BIST;(个人理解:模拟IP的关键功能,可以开发BIST设计。一般情况,BIST造成系统复杂度大大增加。memory IP一般自带BIST,简称MBIST)

3. 扫描测试(又叫ATPG)。scan path。与边界扫描测试的区别,是内部移位寄存器实现的测试数据输入输出。测试目标是std-logic,即标准单元库。(个人理解:扫描测试和边界扫描,不是一个概念。需要区别对待。内部的触发器,全部要使用带SCAN功能的触发器类型。)

补充:

还有一种测试:

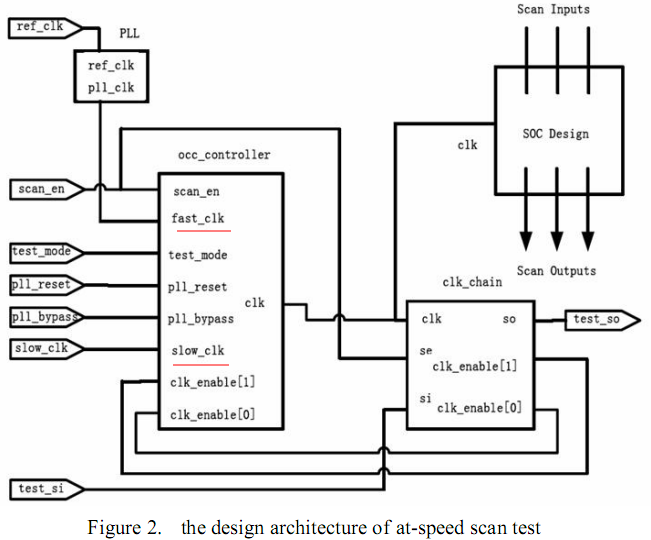

4. 全速测试at-speed-test(其实是属于扫描测试的一种。只不过测试时钟来源频率更快。)

at-speed 就是实速测试, 主要用于scan测试-即AC测试,和mbist测试。这种测试手段的目的是-测试芯片在其工作频率下是否能正常工作,实速即实际速度。测试时钟往往是由芯片 内部的PLL产生很快的测试时钟,用于实速测试。

相对而言 ,一般的测试是20~40兆的测试时钟,频率低,测不到transition fault,即使测试通过,实际使用中还会由于使用高频时钟发生芯片电路故障。

常见的DFT/OCC结构如下:

特点:

1. Clock MUX必须放在OCC模块/DFT MUX之前。

2. 时钟大于50MHz时,使用OCC模块,否则使用DFT MUX。

3. Clock Gate放在OCC模块/DFT MUX之后。

4. 对于手动添加的Clock Gate,DFT_SE端口接到 dft_glb_gt_se。

5. 对于综合工具添加的Clock Gate,DFT_SE端口接到dft_syn_gt_se

注意:

1. DFT_MODE有效时,clock mux的sel信号要保证dft_clk来源于最高频率的时钟源。

2. DFT_MUX或者OCC,不能串联。

OCC(On Chip Clock)结构如下:

注意:

1. slow_clk是类似dft_clk;这个时钟源由后端提供。个人认为所有dft_clk的来源,频率不一样,来源由后端决定,应该是测试引脚输入的吧?!

2. fast_clk是正常工作时钟源。

DFT工程师手里有三大法宝:

法宝一:BSCAN技术– 测试IO pad,主要实现工具是Mentor-BSDArchit,sysnopsy-BSD Compiler;

法宝二:MBIST技术– 测试mem,主要实现工具是Mentor的MBISTArchitect 和 Tessent mbist;

法宝三:ATPG 技术– 测试std-logic,主要实现工具是:产生ATPG使用Mentor的 TestKompress 和synopsys TetraMAX,插入scan chain主要使用synopsys 的DFT compiler。

以下对工具的使用原则做一些介绍:

ATPG工具

Insert scan:

1、虽然教科书会介绍很多种DFT DRC但是在实际设计中95%的工作在修复scan_clk和scan_reset的DRC violation;

2、修复clk/reset violation 的方法主要是用DC插入mux ,目的是使在scan_mode下clk和reset被芯片scan_clk和scan_reset pad控制。 同时,scan_clk和scan_reset pad会用于ATE给芯片施加激励;

3、插入scan时,DFT Compiler必须修复的DRC violations 类别为D1/D2/D3/D9;

4、做全片级的DFT设计时,需要在scan_in,scan_out,scan_reset,scan_clk的IO pad 的OEN/IE/REN端插入mux,控制pad的输入和输出方向。

Atpg patterns产生和仿真:

1、所有的模拟模块,例如PLL、POR等,一般设置为black-box,无法用ATPG测试其内部;

2、芯片clk、power、reset的控制寄存器,一般不会放到scan_chain上,以免在测试时由于寄存器的动作,改变芯片工作状态;

3、考虑power domain的开关,一般必须保证在scan测试时,所有power domain都打开,每个数字标准单元都能测试到;

4、如果有模拟的IO pad,一般必须在产生pattern时mask掉,因为他们不是数字的,ATPG工具无法控制它们;

5、业界一般使用DC插入OCC (on chip clocking)模块,实现at-speed scan测试电路。

MBIST工具

目前使用较多的是MBISTArchi,但是Tessent MBIST以后会成为主流。原因是Mentor公司2013年已经宣布MBISTArchi将不再提供技术支持,而且Tessent MBIST技术更为先进。

1、所有的MBIST设计应该考虑diagnose。加入diagnose电路,方便诊断mem故障,这会在芯片量产时大大提高成品率;

2、由于ARM与Mentor有合作,Coretex-A9以上的ARM核具有share-bus接口,可以很好支持Tessent Mbist,就能够实现ARM内核的mem的高速测试和访问,也提高了ARM CPU的性能;

3、Tessent MBIST会使用JTAP,只占用TCK/TMS/TDO/TDI/TRST五个pad,比MBISTArich使用更少的pad资源。

BSCAN 工具

1、所有的模拟IO,一般无法用bscan来测试,不要加上bscan_cells;

2、所有需要测试的数字pad的OEN/IE/REN 在bscan_mode下,需要插mux来控制;

3、所有需要测试的数字pad的PU/PD 在bscan_mode下,一般需要插mux来控制,保证在bscan_mode下,PU和PD=0,才能使bscan HIGHZ测试仿真通过;

4、所有JTAG的强制要求指令如IDCODE,EXIST必须在bscan电路中实现,特别是BYPASS。

|