|

2.4 一个实现实例

对于上面介绍的技术,我们用Synopsys公司的软件进行了实验验证。

DFT Compiler是功能强大的可测试性设计工具,我们用它对一个多级滤波芯片进行了DFT设计。该图像处理芯片规模较小,内部只有2554个触发器,另外还包含有4个IP核,它们是4个“位数为16、深度为128”的RAM。该芯片初始的设计没有考虑DFT问题,对于综合后的网表,我们施加了DFT功能,故障覆盖率达98.78%。故障覆盖率没有达到100%的原因在于:该芯片采用的硬核内部有64个三态门,没有办法有效的控制它们。另外,我们还用TetraMax对该芯片生成了ATPG,其中有4个时序向量和231个组合向量。

以下是DFT Compiler给出报告的一部分:

0 out of 2554 sequential cells have violations.

*2554 cells are valid scan cells

test coverage is now 98.78%.

Pattern Summary Report

-----------------------------------------------

#internal patterns 0

Uncollapsed Stuck Fault Summary Report

fault class code #faults

------------------------------ ---- ---------

Detected DT 104796

Possibly detected PT 32

Undetectable UD 1069

ATPG untestable AU 1149

Not detected ND 134 -----------------------------------------------

total faults 107180

test coverage 98.78%

以下是TetraMax给出的报告的一部分:

Chain c0 successfully traced with 510 scan_cells.

Chain c1 successfully traced with 510 scan_cells.

Chain c2 successfully traced with 510 scan_cells.

Chain c3 successfully traced with 510 scan_cells.

Chain c4 successfully traced with 510 scan_cells.

107238 faults were added to fault list

Pattern Summary Report

-----------------------------------------------

#internal patterns 235

#basic_scan patterns 231

#fast_sequential patterns 4

2.5本章小结

本章首先介绍了可扫描单元的类型和基本特征,分析了采用各种扫描方式对设计造成的影响和适用范围,然后比较详细的分析了构造扫描链问题上的一些细节问题,给实际设计作好了理论准备。上面的设计方法已经成功应用在一个图像处理芯片上。

3 集成电路的低功耗DFT方法

集成电路测试模式下的功耗会远远高于正常工作模式下的功耗,分析它的功耗来源并设法降低测试功耗,可以节约测试能源(对于移动设备尤其重要),也可以降低因为测试而烧坏芯片的可能性,还可以增加并行测试的模块个数。

本章首先简单的分析了集成电路的测试功耗比较高的原因,将低功耗DFT方法分为两个方面进行阐述:基于扫描设计的低功耗问题和基于非扫描设计的低功耗问题,并给出一些行之有效的方法。

3.1测试模式下功耗比较高的原因

随着便携式设备和无线通讯系统在现实生活中越来越广泛的使用,测试低功耗问题引起了工业界和学术界更多的关注。研究表明:大规模集成电路在测试期间的功耗可能高达该芯片在正常工作模式下功耗的两倍[21]。测试期间功耗更高的原因在于:

(1)电路在正常工作模式下,往往只有一部分电路在工作。而且嵌入的可测试性电路是“闲置”的,它们没有为功率消耗做出“贡献”,然而在测试模式下,所有的电路(包括功能电路和测试电路)都要参与进来;

(2)功率消耗与电路状态的翻转有关,也就是说,功率损耗以动态损耗为主,在正常工作模式下前后激励(被处理数据)之间有较大的相关性,因而在测试模式下,各个电路节点的翻转次数远远高于正常工作模式;

(3)测试码生成器经常采用伪随机测试向量产生技术,它产生的众多测试向量中,有许多对测试覆盖率没有贡献,但是却加载在被测电路的输入端,造成了更多的功率损耗。

(4)为了缩短测试时间,经常采用并行测试,造成整个芯片或者系统的功耗增大。如果没有良好的测试调度方案,则会造成测试功耗(或者测试峰值功耗)大幅度上升,热击穿其中的一些器件,甚者烧毁芯片(或者晶片)。

一般来说,应该将降低测试功耗的方法分两种情况来讨论,就是基于扫描设计的低功耗DFT方法和基于非扫描设计的低功耗DFT方法。下面就以这样两种情况进行分析。

3.2基于扫描设计的低功耗DFT方法

扫描的方法就是将测试向量施加到扫描链中,然后让电路切换到测试工作模式,之后将测试响应移出扫描链。在测试向量和测试响应在扫描链上移动的时候,和它相连的组合逻辑电路会有大量的翻转,这是功耗的重要来源之一。我们可以对测试矢量进行编码,得到低功耗的测试向量,也可以合理利用芯片本身的测试资源来降低测试功耗。

3.2.1测试矢量的处理

对于组合逻辑,将测试矢量进行排序,可以降低测试功耗。但那只是一种最粗浅的方法。一般来说,测试矢量的处理包括四个过程,分别是:排序、差分、编码、解码。对于已经生成的测试矢量进行排序,目的在于建立测试集中测试矢量的相关性,做差分运算以后的向量就可以具有较多的“0”(最好的情况下只有1位非“0”),这样可以保证电路中节点的翻转尽可能的减少。将差分向量进行级联,可以得到一个测试代码链,然后按照某种编码方案进行编码。编码的目的主要有两种:一种是为了减少测试数据的传输时间(带有压缩性质);另外一种是为了减少电路节点上的翻转[22]。

3.2.2合理划分片上的测试资源

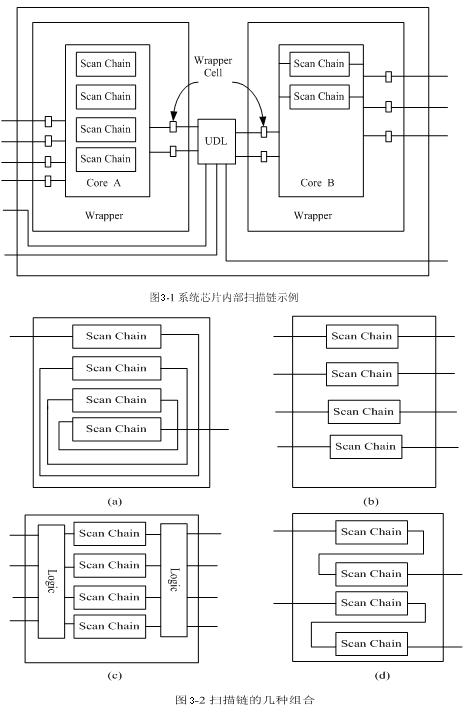

基于IP设计的SoC,各个芯核中一般都有开发商提供的测试电路,而可测试电路的设计一般是基于扫描结构的设计。在每个IP核中,往往会有若干个扫描链,这种结构如图3-1所示。为了简便起见,图中只画出了两个内核,其中核A中有4条扫描链,核B中有两条扫描链,UDL是用户自定义逻辑(User Defined Logic);对UDL进行测试的时候,可以利用两个内核的包(Wrapper,有的文献称为“测试环”)单元进行,这时A和B则必须工作在外测试(Extest)模式下。对于内核A而言,它有四个扫描链,如果对它们进行串行测试,如图3-2(a)所示,则产生最大的功耗,同时也需要最长的测试时间。如果采用图3-2(b)所示的做法进行并行测试,则可以有效的减

少测试时间,但是对于测试期间的最大功耗问题,则没有改善。采用图5-2(c)所示的电路结构,虽然测试时间没有改善,但功耗却最低,大约为图(a)的1/4。采用图5-2(d)所示的电路结构,则可以降低一半的测试功耗,值得注意的是,在减少测试时间的同时,也增加了集成电路的测试引脚数目,使得电路的布局布线更加复杂。

3.2.3 减少测试电路节点的翻转次数

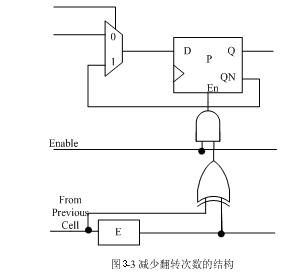

可以采取各种各样的方法来减少电路在被测试过程中的翻转次数,从而达到降低功耗的目的。如图3-3所示的电路结构可以有效的减少电路的翻转次数。在这种结构中,P触发器是主存储单元,它包含施加到CUT(被测试电路,Circuit Under Test)的测试向量。E链中的触发器用于提供选择触发的数据,这种机制有两种方法来减少不必要的翻转。首先,测试数据(经过编码的激励信号,编码的基本原则是将需要翻转的P触发器相应的E链中的两个触发器设置为不同的值)直接通过扫描方式加

载在E链上(此时Enable信号为低电平),只有需要将激励加载到测试电路的时候,才将需要翻转的P链中的触发器翻转。在触发模式,使能信号被激活,多路选择器将QN反馈到触发器的输入端。但是如果异或门的输出为“0”,P触发器的值将保持不变,但是如果异或门的输出为1,P触发器将翻转。在进入工作模式之前,E链首先被送入“10101010……”这样的数据,激活所有异或门的输入端,并将Enable设置为“1”,这样P链就可以工作在任务模式下了。另外还有一种方法,是采用前面介绍的类似于测试数据的处理办法,也可以使尽可能少的P触发器翻转[23]。

3.2.4软硬件协同测试

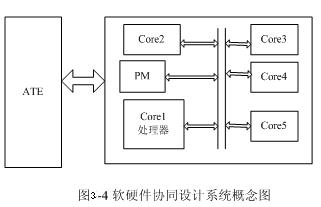

图3-4示出了软硬件协同测试集成电路的一般概念[18,23]。该结构由以下几个部分构成:若干个core和一个处理器(在实际应用中,可能会有多个处理器),它们通过总线形式相连;一个测试数据存储器PM(Pattern Memory),它用来存放测试指令和测试数据。当运行在测试模式时,ATE将测试指令和测试数据传输到PM,使用处理器自身的指令系统,对各个内核进行测试。这里,处理器不仅可以对测试数据进行有效的格式转换,而且可以对捕获的测试响应进行分析和比较,得出故障的类型和位置,并将测试结果返回给ATE。由于此类测试方式可以对测试向量进行编码和压缩,测试功耗可以压得较低。而且,由于这种测试模式下的频率可以和正常工作时的频率相同,因而能够有效避免因为测试频率和工作频率的差异而带来的不良影响。

|