|

这篇文章主要讲一下芯片设计中测试环节以及相关的概念。芯片设计中的测试分为以下几类:

1)验证:在芯片量产之前,验证设计是否正确和符合规范。在验证时,主要进行功能测试和电气特性测试。功能测试是测试输入激励与响应的一致性,电气测试分为直流和交流特性测试两种。而直流测试主要是对短路、开路、最大电流、漏电流、输出驱动电流和开启电平的测试。交流特性主要是对传输延时、建立和保持时间、速度、访问时间等特性的测试。

2)量产测试:在量产之前,每个芯片均要经过此测试,要求测试的时间段,因此只能做go/no go测试,不做错误诊断。

3)老化测试:测试芯片的可靠性,采用各种加速因子来模拟器件长期的失效模型,常用的有加高温加高压等。

下面对测试仪、故障模型进行介绍,然后对常见的可测性设计方法进行概述。

测试仪:测试集成电路的仪器,它负责按照测试向量给集成电路加激励,同时观测响应。目前,测试仪一般都是同步的,按照时钟节拍从存储器中调入测试向量。测试仪的参数包括:测试仪通道数目、测试仪最小周期、测试仪最小脉冲宽度、测试仪支持的激励波形。常见的测试仪有如下的特点:

1)采用同步时序

2)激励的波形有限

3)响应的测试时刻有限

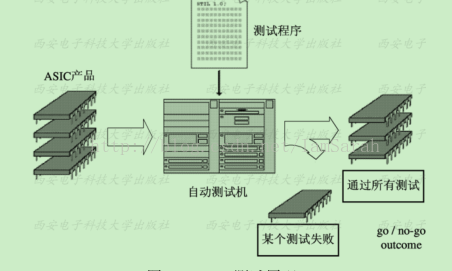

下图给出了自动测试仪ATE工作原理。ATE通常由工作站或者PC机控制,有一个或者多个CPU。测试系统有一个或者多个测试头。测试向量存放在存储器中,当测试时,将测试头与芯片的引脚接触,然后调用测试程序,施加激励,并将芯片的输出相应于预期的激励进行比较,如果一致则芯片正常,否则芯片有误。

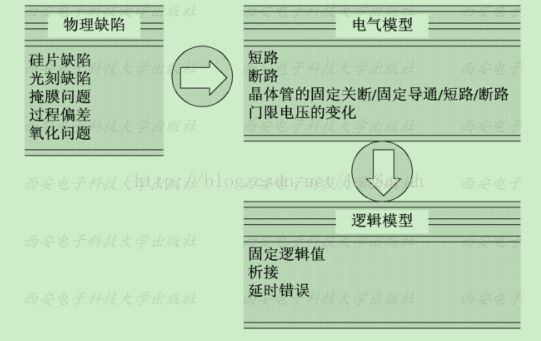

故障模型:制造缺陷会导致芯片无法正常工作。制造缺陷通常包括硅片缺陷、光刻缺陷、掩膜缺陷、工艺偏差等,这些会导致芯片出现如下的问题:

1)连线与电源或者地短路

2)连线开路

3)晶体管的源或者漏极短路

出现故障的机理是各种各样,为了能够高效地检查电路中哪一部分除了问题,需要构造故障模型,并根据故障模型产生测试向量集合。物理缺陷对应的电气模型和逻辑模型如下图所示:

故障模型是对物理缺陷的逻辑等效。常用的故障模型分为下面几种:

1)固定值故障模型

2)延时故障模型

3)基于电流的故障模型

下面是对可测试设计方法概述:

为了检查电路中故障,需要将激励施加到有故障的逻辑,并且将它们的错误激励传递出来,这就是可测性设计中可控制性与可观测性的概念。对一些简单的电路可以通过输入端口实现电路的可控制性,通过输出端口实现可观测性。但是实际电路中输入输出端口非常有限,为了实现可控制性和可观测性,需要增加相应的测试电路。在不同的测试技术中,采用的测试电路是不同的。

IC系统的测试通常可以分为下面几种:

1)静态电源电流测试IDDQ:检查电路是否有异常的、较大的漏电流。

2)路径扫描:规则的可测试性设计方法,适用于时序电路。

3)内建自测性:将激励电路和响应电路加在被测电路中。

4)边界扫描:即JTAG测试,主要用于板级测试,用于检查芯片引脚的连接情况。在该方法中,利用四线接口扫描所有的管脚。利用JTAG还可以观察修改电路的逻辑状态。

在测试中,加载到集成电路中的输入信号称为测试向量;测试向量以及集成电路对这些输入的信号的响应合在一起称为集成电路的测试图形。而测试向量的生成方法如下:

1)人工法:设计者生成

2)程序自动生成:由工具根据所用的测试技术、测试协议和故障模型,自动生成测试向量。

3)自测试

|