2.2.4辅助时钟LSSD的扫描方式

此类可扫描单元要采用三个测试时钟,因而带来较大的面积开销,并且不能测试系统时钟的故障,因而实际应用中较少采用,所以此处不再给出具体的分析。

2.3如何提高故障覆盖率

提高故障覆盖率的关键就是要提高电路的可控制性和可观察性。

由于种种原因,某些电路的可控制性和可观察性往往不高,不可控制或者不可观察,也就造成某些故障的不可测试。鉴于这样的原因,就需要对电路进行修改,修改电路的同时,要保证逻辑和时序的正确。这里给出一些常见问题的解决办法。

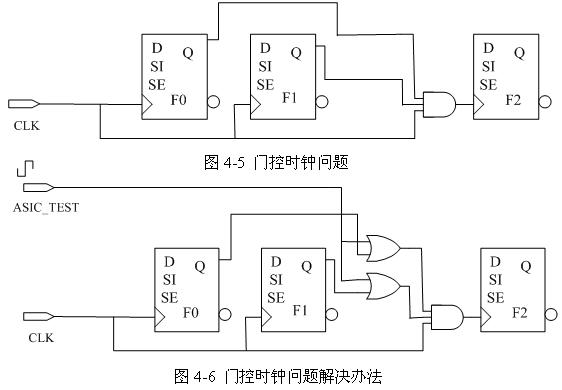

2.3.1门控时钟问题

如下图4-5所示,当F0、F1中的任何一个为0时,时钟脉冲将被阻止传到F2,因此F2将不能和F0、F1放在同一个扫描链中。解决这个问题的办法如图4-6所示。在正常工作时,ASIC_TEST为低电平,插入的两个或门均打开,和图4-5功能相同。

在测试期间,测试信号ASIC_TEST为高电平,扫描和捕获时钟总能到达F2,因此F2可以和F0、F1放在同一个扫描链中。

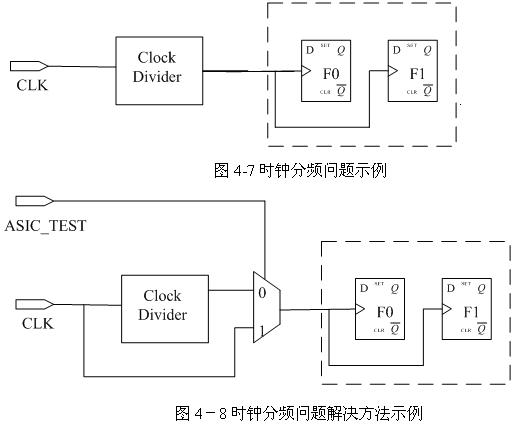

2.3.2时钟分频问题

ATE只能控制输入端口的波形,对于如图4-7所示的情况, ATE只能控制CLK,在扫描过程中,对于虚线框中的F0和F1,并不是每一个测试时钟都能够到达F0和F1,因此,在测试过程中,很难预测它们的状态变化。这样就需要改造该电路来实现可测试性。改造后的电路如图4-8所示。图中增加了一个二选一选择器。在正常工作状态,ASIC_TEST为低电平,分频后的时钟信号可以驱动F0和F1,与图4-7的逻辑功能相同。在测试方式下,CLK可以直接作用到F0和F1,因此F0和F1可以被包括到扫描链中。值得指出,选择器的引入可能造成时钟歪斜(clock skew),但是,在频率不高的情况下,可以忽略这个影响。

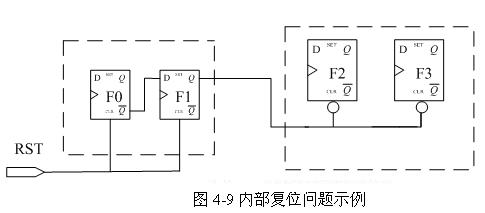

2.3.3内部复位问题

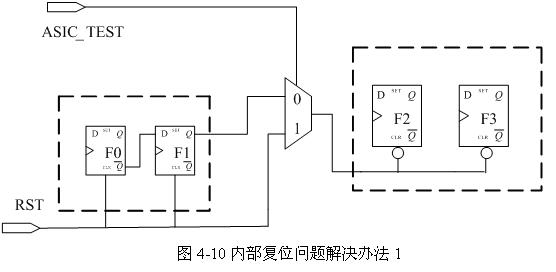

该问题是指在电路内部有不可控制的异步复位端,如图4-9所示。从图中可以看出,F2和F3的复位端和F1的Q端相连,因此,在测试向量施加的过程中,F1的状态将影响F2和F3的值,造成扫描链测试数据加载混乱。为了解决这个问题,采用图4-10所示的方法:增加一个多路选择器。在正常工作模式下,该选择器是透明的,

电路的工作逻辑和图4-9完全相同,也就是说,不会出现功能上的错误。在测试模式下,ASIC_TEST为高电平,复位时钟可以有效的施加在所有的触发器上,使得扫描链可以正常的加载测试向量,进行扫描测试。

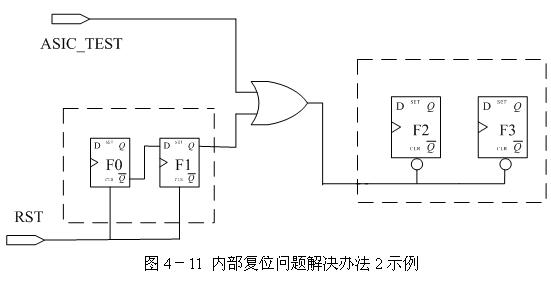

另外还有一种解决该问题的办法,如图4-11所示。在正常工作模式下,ASIC_TEST为低电平,或门对于Q1而言是直通的,不影响电路的正常功能。在测试模式下,ASIC_TEST为高电平,从而阻碍了Q1对F2和F3的影响,因而它们都可以放在扫描链中。至于是否放在同一个扫描链中,就看设计的需要了。

两种方法的比较:在办法1中,内部复位线上的SA1故障是可以测试的,而办法2则不然,因此,办法1比办法2有更高的故障覆盖率。另一方面,由于选择器比或门有更复杂的电路结构,所以采用方法1将会有更大的面积开销。

2.3.4 三态网络的DFT

三态网络需要考虑的可测试性问题有:

1.不可检测的故障

这时需要增加DFT逻辑(或者增强ATE的功能),来获得100%的故障覆盖率;

2.在扫描移位过程中出现的总线争用(Contention)

扫描比特流可能导致三态驱动器处于一个未知的状态;

3. 在捕获响应的时候出现的总线争用(Contention)

捕获时钟边缘的状态变化可能使得三态驱动器处于一个不确定的状态;

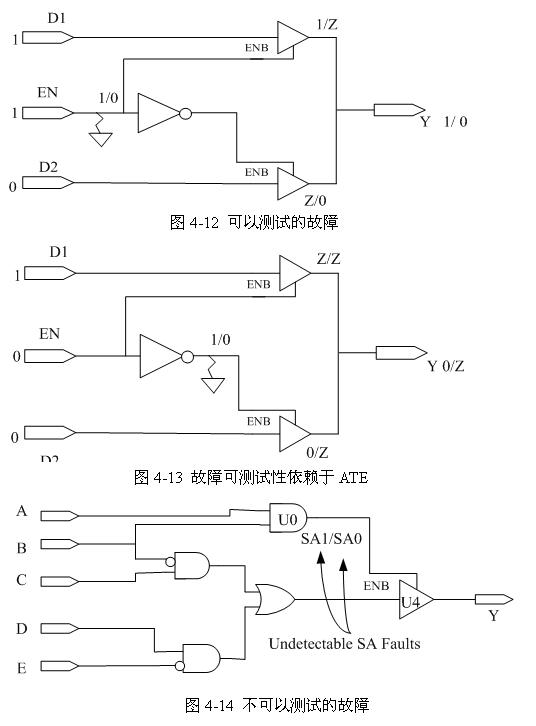

三态门的某些故障是可测的(如图4-12中,EN引脚上的SA0故障);某些故障能否测试则与ATE的性能有关(主要看ATE是否具有测试Z状态和X状态的能力)(如图4-13);还有一些故障是不可以测试的(如图4-14)。为了确保电路能够在更多的测试仪上有较高的故障覆盖率,为保险起见,我们将后两种情况视为不可测试。

|