|

1.6边界扫描测试的发展前景

IEEE Std 1149.1-1990是边界扫描的第一个协议,它拉开了边界扫描技术推广与使用的序幕。IEEE Std 1149.4是对1149.1的一个补充,使得模拟耦合方式的测试成为可能。1149.6则在以上两个协议的基础上,扩充了指令集,增加了交流耦合通路和差分通路的测试能力。边界扫描协议IEEE Std 1149.5中定义的MTM总线结构,为扫描测试向网络化方面的发展奠定了基础。主模块和从模块之间的默契,为远程测试做下了铺垫。1149.6的提出,完善了混合系统测试的方法,使得电路中几乎所有的模块可以相互连接,统一在主测试模块的管辖之下。Agilent公司的芯片已经可以实现1149.6所要求的功能,完全支持1149.6的交流测试模式。

主模块和从模块的这种网状结构,进一步可以扩展为多级星型结构。借助于现代的互连网技术和全球定位系统,加上已经比较成熟的无线通信协议,我们相信,在不远的将来,每个服务商和各个运营商将会拥有自己的“Intranet”,随时对自己的设备进行故障检测和故障定位。

1.7 本章小结

本章简要的回顾了边界扫描的主要功能和主要实现思想,对边界扫描的系列协议进行了简单的总结,并展望了边界扫描技术在未来测试领域的应用。

今天的系统芯片有望成为明天的IP核,边界扫描结构在以后更大规模的集成电路设计中将成为诸多嵌入式内核之间互连测试的有效方法。另外,由于边界扫描单元位于芯片的引脚端口,它也是一条直接控制内建自测试的有效通道。

2 全扫描可测试性实现方法

为了便于实现ATPG的产生和加载,经常要使用扫描电路。由于在集成电路中,被集成的IP核要保持原有的特性,对于IP核使用者来说,只在用户自定义逻辑中采用全扫描与部分扫描技术。对于IP核设计者来说,一般而言,大多都要用到全扫描或部分扫描技术(一部分BIST电路除外)。

本章首先简要介绍扫描测试的必要性,然后详细探讨可扫描单元的基本类型和扫描链处理上的一些问题。值得指出:虽然本章介绍了多种可扫描单元类型,例如多路选择器型的触发器型、专用时钟型、电平敏感型等,但是在后面关于扫描链问题的处理上,通常用多路选择器类型中的二选一选择器D型触发器为例来进行探讨,对于其它类型的可扫描单元也可以使用类似的方法。

2.1为什么需要扫描测试

集成电路器件的制造面临着许多测试问题。现实情况表明,集成电路器件的发展趋势是更高的密度、更多的引脚、更大的晶圆尺寸、更小的特征尺寸、更细的导线、更高的频率,这就使得集成电路对污染、工艺更加敏感,与此同时,也包含了出现物理故障的更高概率(由于更多的门与门之间的互连)。“更高的频率”、“更多的管脚数”和“更高的复杂性”使得测试平台的价格不断提升,出现了“测试代价危机(crisis in test cost)”。在某些市场,由于测试而带来的消费是硅片和封装价格总和的2~4倍[20]。面对这样的问题,最好的解决方案就是提供某种测试访问机制,该机制能够提高电路内部节点的可控性和可观察性,从而缩短测试时间、减小测试数据量、降低测试平台复杂性。扫描测试可以有效的解决这个问题。

扫描测试是在设计的时候用可扫描寄存器替换原来的标准寄存器,从而增加电路中的可控制点和可观察点,相当于增加了许多虚拟探头。它的不足之处在于它会对原来电路的性能发生一定程度的影响,也会增加布局布线的复杂性和芯片的面积。

2.2可扫描单元类型

可测试性设计的一般思想是构造扫描链,构造扫描链的关键是用可扫描寄存器替换原来的标准寄存器。一般情况下,可以使用的具有扫描功能的寄存器有四种类型,分别是:多路选择器型、专用时钟型、电平敏感型、辅助时钟型。下面逐一加以介绍。

2.2.1多路选择器型的触发器

这是一种主流类型。用带有选择器的触发器(或锁存器)单元替代标准的触发器(锁存器)单元,并将它们串在一起,形成扫描链,然后将ATPG施加到其上,就可以控制和观察电路内部节点处的信号。图4-1给出了采用多路选择器构成的可扫描触发器。图a为常规的D触发器示意图,图b为可扫描D触发器符号,图c为图b相对应的内部电路结构。

由图中可以看出,具有扫描功能的触发器增加了两个输入端口:Scan_in和Scan_En。Scan_in引脚用于接受扫描数据的输入,Scan_En用于扫描使能。在测试模式下,将测试向量打入寄存器的时候,将Scan_En置为“1”;在正常工作模式下和测试模式下的非扫描状态,将其置为“0”。

采用多路选择器而增加的延迟表现在功能路径中,有较少的面积增加。一个带多路选择器的D触发器通常将一个标准D触发器的面积增加15%到30%;增加的I/O端口最少的可以只有一个Scan_En。在实际设计中,可能并不需要增加一个另外的I/O端口用于Scan_in或者Scan_out,因为可以在设计中将这些引脚和功能引脚复用。

2.2.2 专用时钟扫描单元

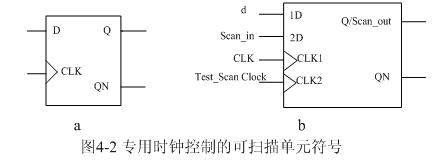

专用时钟控制的扫描方法是使用一个专用的、边沿触发的测试时钟来提供串行移位驱动。在功能模式下,系统时钟是活动的,系统数据被时钟打入单元电路。在测试移位过程中,测试时钟是活动的,扫描数据被打入该电路单元。电路符号如图4-2所示。图a为标准的D触发器,图b为专用时钟控制的可扫描单元。在这种结构中,相当于有两个D输入端,两个时钟输入端。在这种方式下,需要增加的测试引脚有:扫描输入、测试时钟、扫描输出(可以和输出功能引脚共用)。

专用时钟控制扫描方式的特征是:

对电路性能影响可以忽略;面积的增加可以接受:一个专用时钟控制的扫描单元一般比普通的D触发器的面积增加15%--30%;支持这种扫描方式的工艺库具有触发器和锁存器两种等效单元;很适用于部分扫描设计:专用的测试时钟提供了一种机制,在扫描移位的过程中,可以很容易地保持非扫描单元的状态;支持带有异步置位和复位端的锁存器;典型的应用是具有边沿触发的设计风格。

2.2.3 电平敏感扫描设计

常见的电平敏感扫描(LSSD扫描设计,Level Sensitive Scan design)单元有3种方式:单锁存器、双锁存器、专用时钟控制锁存器。

2.2.3.1单锁存LSSD

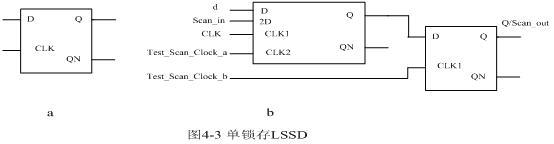

单锁存电平敏感扫描单元的逻辑结构如图4-3所示。图a为通常意义下的D触发器,图b为它相应的可扫描单元。图b增加了一个数据输入端、两个时钟输入端:Test_Scan_Clock_a和Test_Scan_Clock_b。增加的两个时钟是电平触发的。在测试模式下,Test_Scan_Clock_a和Test_Scan_Clock_b连接到所有的同类扫描单元,分别在不同的时刻将扫描数据逐位移动。Scan_in引脚的数据来自上一个扫描单元。

单锁存器LSSD的特征是:

a) 对电路性能的影响可以忽略;

b) 较高的面积代价。用一个LSSD单元替换一个简单的锁存器将会增加100%或者更多时序逻辑的面积。增加的主测试时钟和从测试时钟也增加了布线的面积(与多路选择器型的触发器扫描类型相比);

c) 支持带有异步复位和清零端的锁存器;

d) 因为增加了专用的测试时钟,所以适合用于部分扫描设计。

2.2.3.2双锁存器LSSD

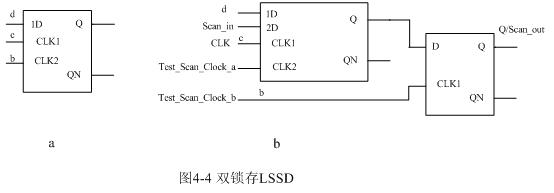

双锁存器LSSD的基本结构如图4-4所示。图a为常规的主从式D触发器,图b为它的可扫描单元。相对于图a而言,图b增加了两个引脚:Scan_in和Test_Scan_Clock_a。

在工作模式下,LSSD单元中的主从锁存器实现原来的主从锁存器的功能,系统数据被主从时钟c和b打入锁存器对,数据在从锁存器输出端输出。

在串行移位模式下,两相非交叠主从测试时钟施加到时钟输入端实现数据移位。注意在双锁存LSSD中,从时钟(b)既用于工作模式又用于测试模式,而在单锁存LSSD中,它只用于扫描模式下的串行移位。

双锁存器LSSD特征是:

a) 对电路性能的影响可以忽略;

b) 较低的面积增加量(15%--30%);

c) 支持具有异步复位和清零端的锁存器;

d) 因为有专用的测试时钟的加入,所以适用于部分扫描设计。

2.2.3.3专用时钟控制的LSSD

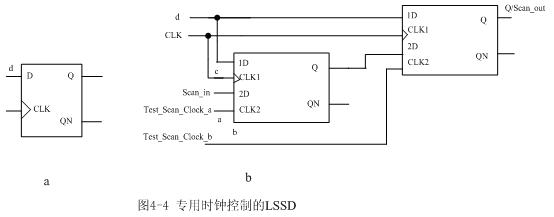

专用时钟控制的LSSD使用与LSSD兼容的触发器单元替换边沿触发器。在正常工作模式下,系统时钟有效,一个专用时钟控制的LSSD单元像一个边沿触发器一样完成系统数据的存储。在扫描模式下,两相非交叠时钟驱动主从测试时钟完成扫描数据的移入和移出。

专用时钟控制的LSSD的特征:

a) 对电路性能的影响可以忽略

b) 中等的面积开销。一个扫描单元的面积比基本的触发器增加40%---80%。布线面积也会因为两个测试时钟的加入而有所增加。

c) 适合于部分扫描设计,因为有专用的测试时钟。

|