[测试设备原理] 一款PVM板的设计1 日期:2015-04-19 22:18:22 点击:904 好评:290

[测试设备原理] 一款PVM板的设计1 日期:2015-04-19 22:18:22 点击:904 好评:290

现在测试的产品,对ATE的要求越来越高,譬如某款很常见的AC-DC driver,limit也就+-4个mV。ATE内部的VI源由于设计复杂,本身产生的噪声很难控制下来,所以对1mV以下的信号测量的绝对精度...

[测试基础理论] 开短路测试基本原理 日期:2015-04-15 22:34:10 点击:10859 好评:451

[测试基础理论] 开短路测试基本原理 日期:2015-04-15 22:34:10 点击:10859 好评:451

开短路测试,是测试工程师需要掌握的最基本的技能,通常被称为continuitytest 或者open/short test。开短路测试的原理,其实是基于产品本身管脚的ESD防静电保护二极管的正向导通压降的原...

[测试基础理论] 开尔文测试基本原理 日期:2015-04-15 22:28:05 点击:7602 好评:395

[测试基础理论] 开尔文测试基本原理 日期:2015-04-15 22:28:05 点击:7602 好评:395

开尔文测试方法,是模拟电路测试常用的测试方法之一,又叫开尔文四线检测(Kelvin Four-terminal sensing),也被称之为四端子检测(4T检测, 4T sensing)。四线检测也被称为开尔文(Kelvi...

[芯片相关原理] 详解IGBT的工作原理和作用 日期:2015-02-07 12:17:12 点击:1103 好评:250

[芯片相关原理] 详解IGBT的工作原理和作用 日期:2015-02-07 12:17:12 点击:1103 好评:250

本文通过等效电路分析,通俗易懂的讲解IGBT的工作原理和作用,并精简的指出了IGBT的特点。可以说,IGBT是一个非通即断的开关,兼有MOSFET的高输入阻抗和GTR的低导通压降两方面的优点...

[测试机台/ATE] ATE加流测压及加压测流的设计 日期:2015-02-07 11:40:27 点击:5337 好评:375

[测试机台/ATE] ATE加流测压及加压测流的设计 日期:2015-02-07 11:40:27 点击:5337 好评:375

自动测试设备 是用于测试分立器件、集成电路、混合信号电路直流参数、交流参数和功能的测试设备。主要通过测试系统软件控制测试设备各单元对被测器件进行测试,以判定被测器件...

[测试设备原理] 高阻抗微弱信号测量的保护电路设计 日期:2014-10-22 09:08:10 点击:1257 好评:280

[测试设备原理] 高阻抗微弱信号测量的保护电路设计 日期:2014-10-22 09:08:10 点击:1257 好评:280

空气质量检测、光电信号探测、加速度计、压电传感器以及生物体信号等 高阻抗 信号测量,易受到来自测量系统输入电阻、输入偏置电流的影响,实际测量系统中主要有与信号路径相并...

[测试设备原理] 负载电流的测量方法分析 日期:2014-10-22 08:51:34 点击:1699 好评:256

[测试设备原理] 负载电流的测量方法分析 日期:2014-10-22 08:51:34 点击:1699 好评:256

引言 电流 测量 可用于监测许多不同的参数,输入功率就是其中之一。有许多采样元件都可用来测量 负载电流 ,但没有一种元件能够覆盖所有应用。每种采样元件都有其优点和缺点。...

[测试元器件] 元器件基础知识:电容器是如何工作的? 日期:2014-10-17 10:47:13 点击:1630 好评:303

[测试元器件] 元器件基础知识:电容器是如何工作的? 日期:2014-10-17 10:47:13 点击:1630 好评:303

一篇不错的电容知识,原理介绍 电路是道路,电荷是车 如果将一个电路比作马路的话,电荷的移动就好像车流一样。 阻抗是崎岖的道路 道路凹凸不平的情况下,车的行驶速度虽然会减...

[测试基础理论] 关于Cpk的一些知识 日期:2014-05-30 09:22:02 点击:13846 好评:319

[测试基础理论] 关于Cpk的一些知识 日期:2014-05-30 09:22:02 点击:13846 好评:319

关于 Cpk 的一些常识 现在很多的客户要求了解你生产设备的能力,都要求看你的Cpk值。什么是Cpk值?我这里传载一些介绍给大家,要详细的了解,还是要看SPC。 SPC相关术语解释 您知道...

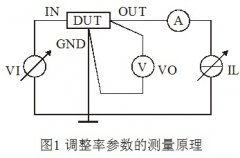

[测试基础理论] 集成稳压器调整率参数的测试 日期:2014-05-24 21:23:29 点击:2195 好评:344

[测试基础理论] 集成稳压器调整率参数的测试 日期:2014-05-24 21:23:29 点击:2195 好评:344

集成稳压器调整率参数的测试 北京华峰测控技术公司 孙 铣 赵建平 摘要 本文介绍了集成稳压器调整率参数的测量原理和方法,分析了影响调整率参数测量精度的各种原因以及为此而采...