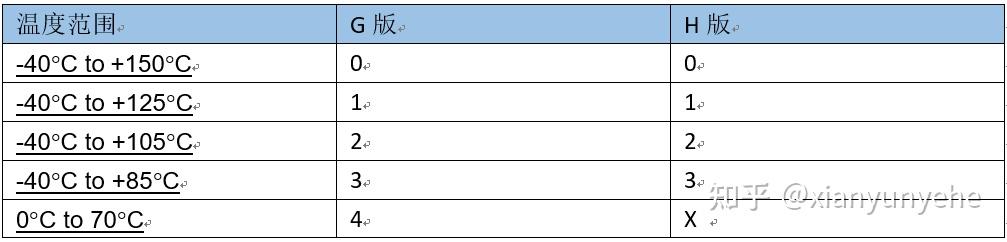

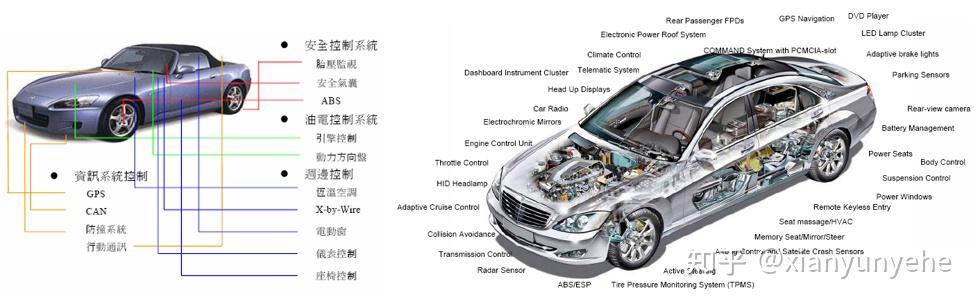

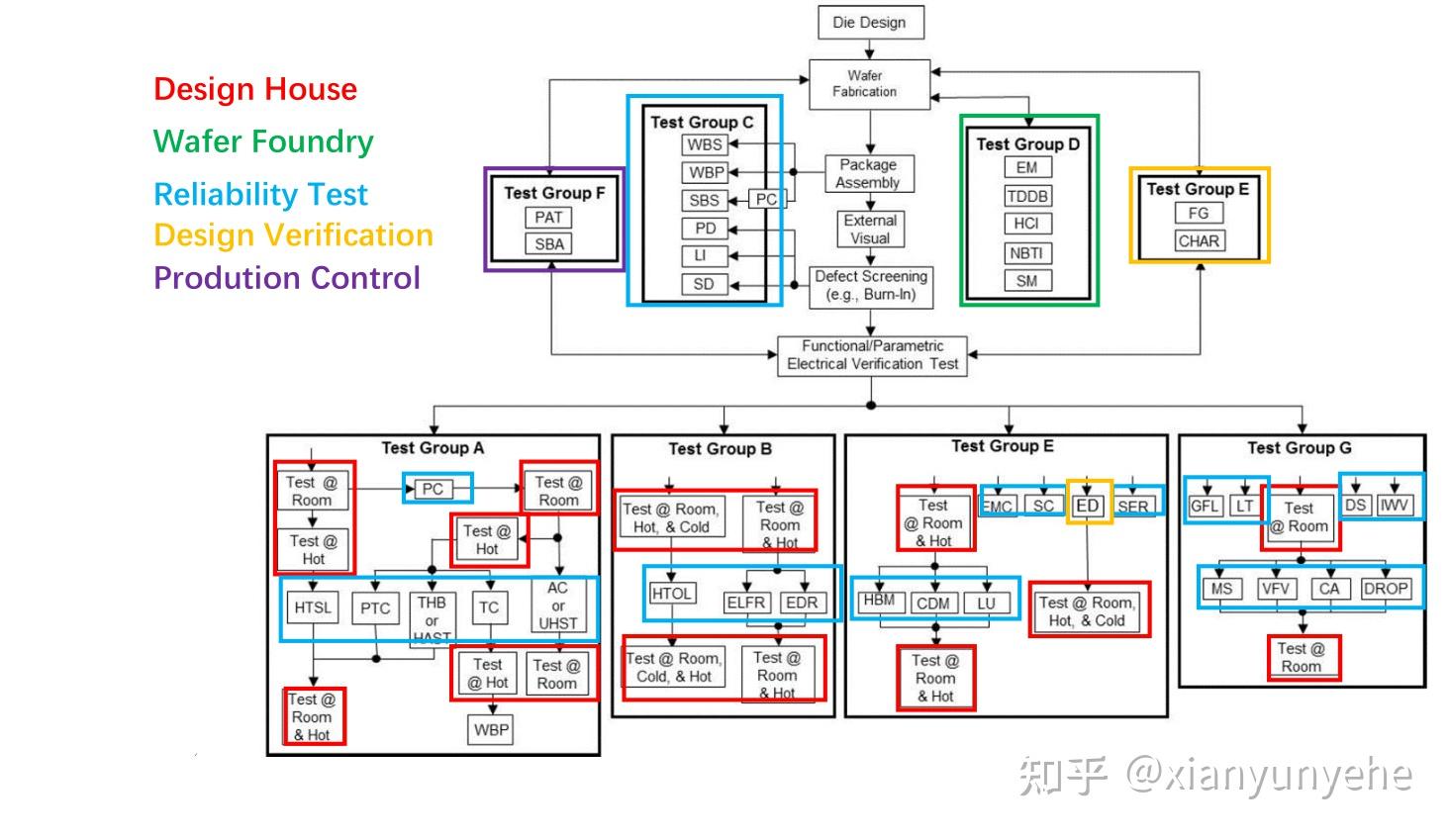

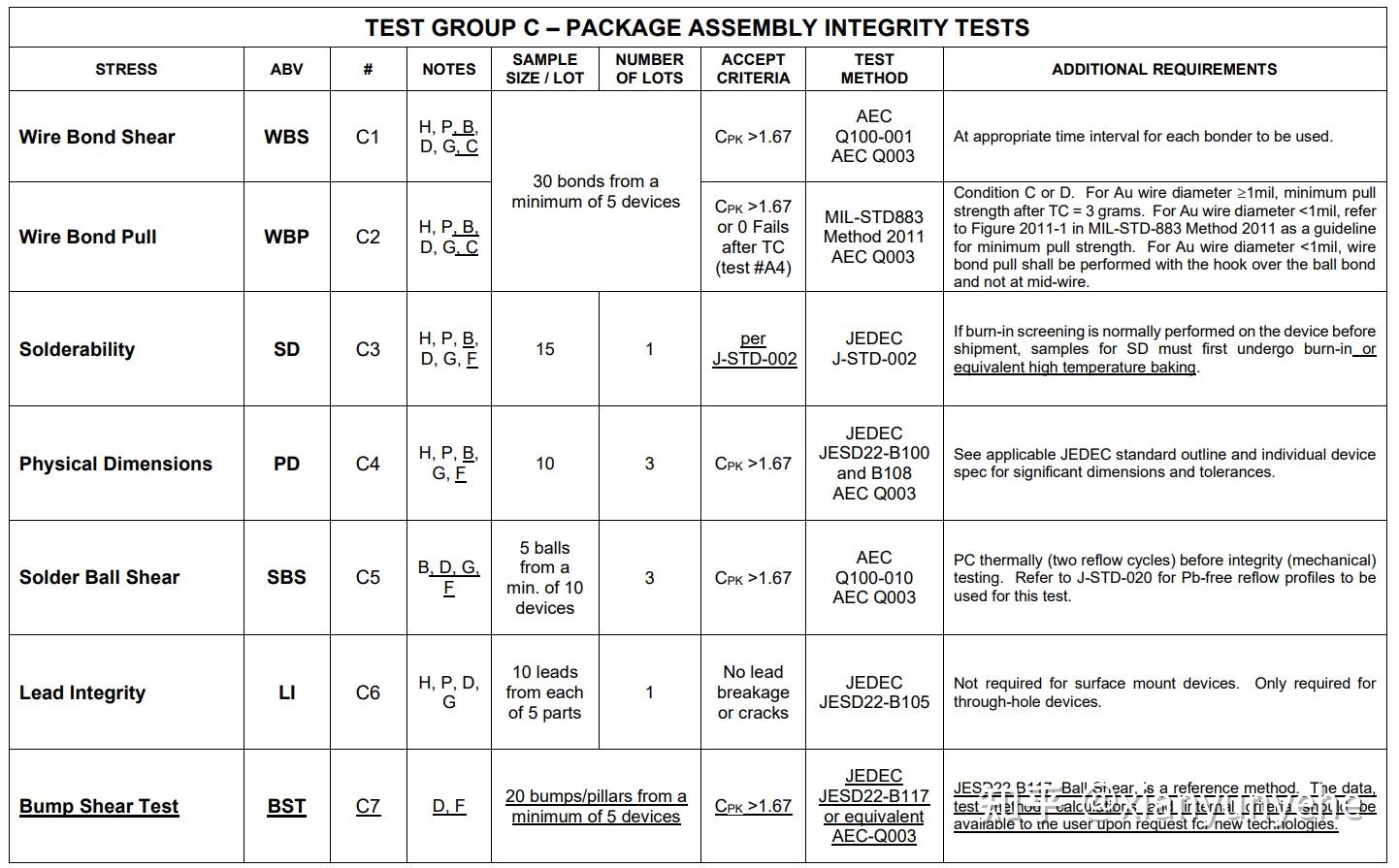

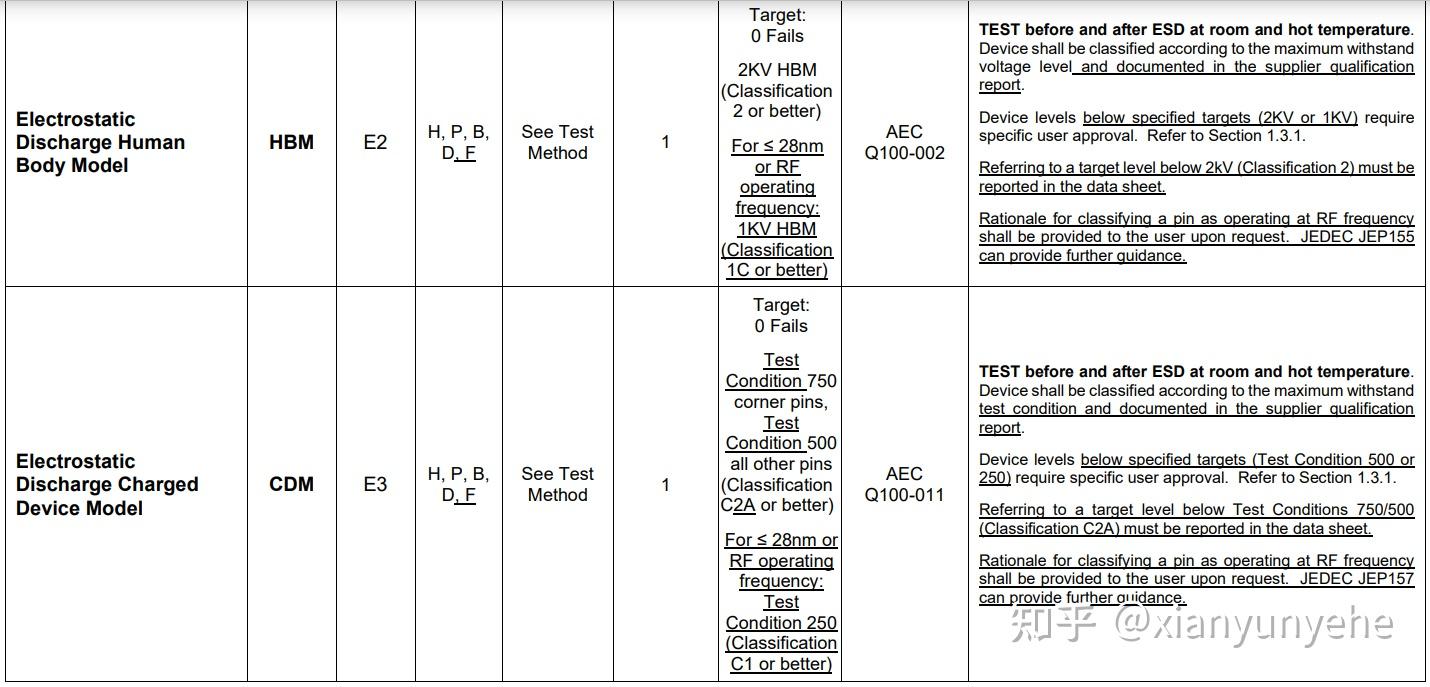

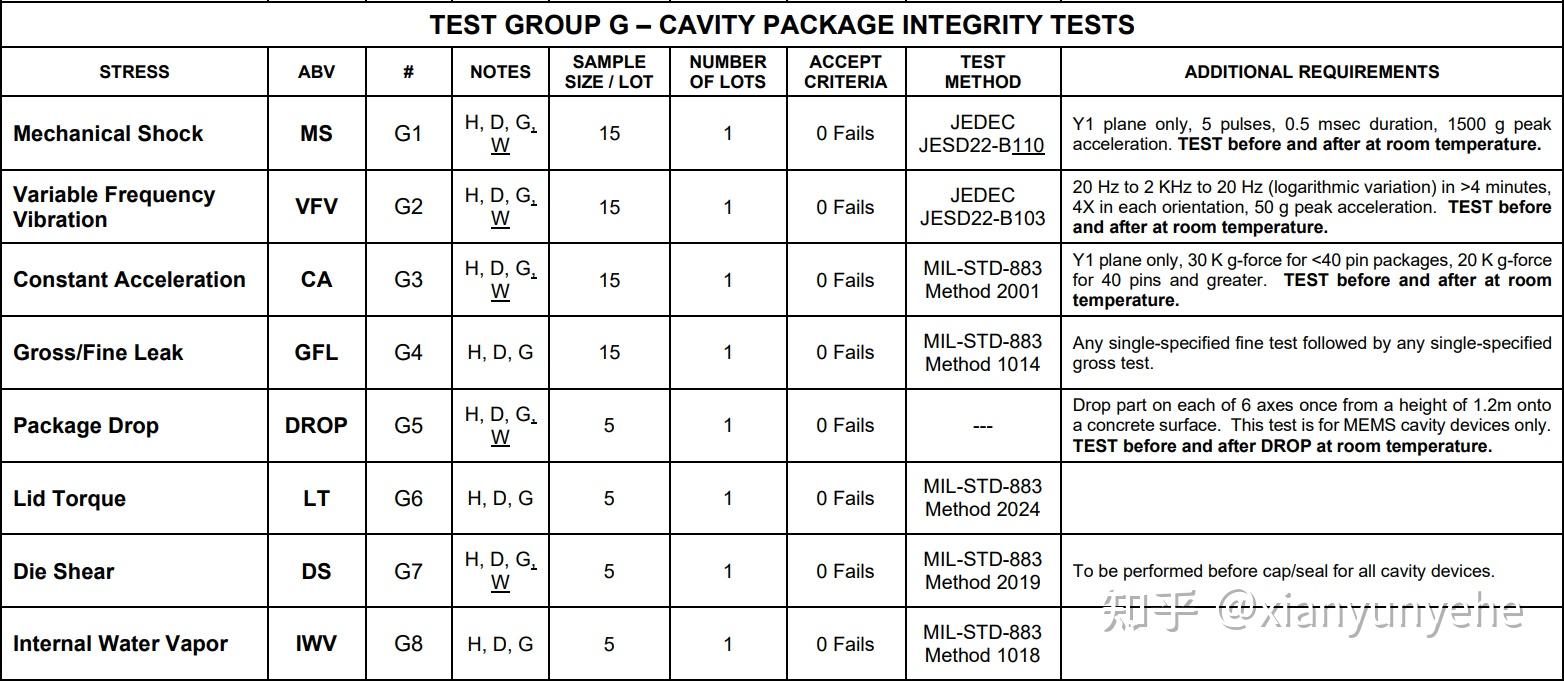

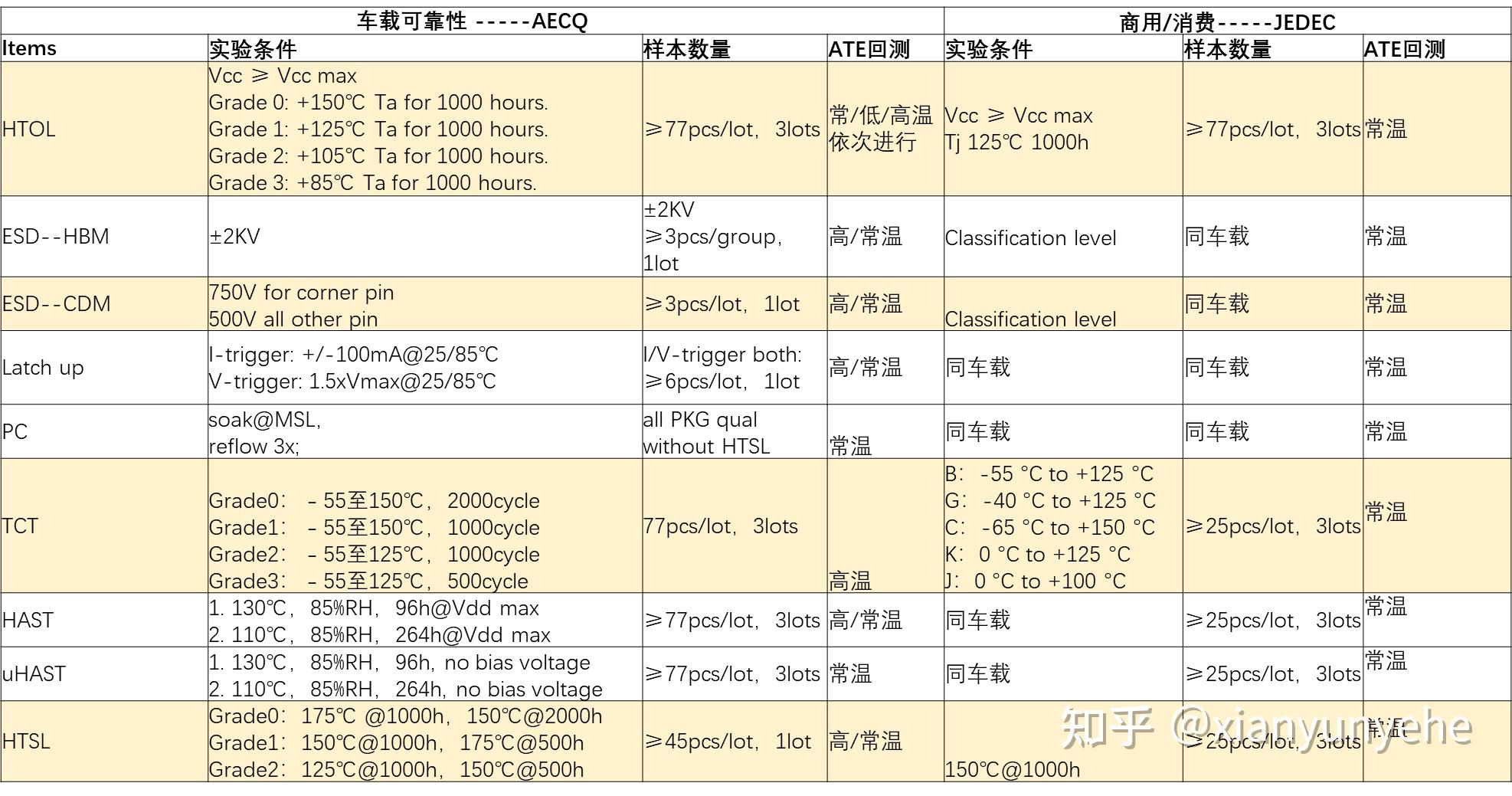

芯片可靠性提升的关键驱动因素之一是汽车的可靠性,因涉及到生命安全,汽车故障在召回成本和品牌声誉方面都是昂贵的。 今天主要聊一聊车规认证跟消费电子可靠性认证的一些区别和注意事项,以及新版AEC-Q100-REV-J相对于AEC-Q100 -REV-H的一些改动。 一辆车越智能,对应的控制模块和传感器越多,需要的芯片也越多。芯片在车内的位置不同,对应的环境温度也不同。比如靠近发动机的环境温度高,而车饰应用温度低。对于不同的模块,验证分不同的grade,H版去掉了0℃~70℃的等级4。目前按照grade0、1、2、3,J版也用H版的grade划分。  AECQ最新的文件可以在官网上下载: AEC Documentswww.aecouncil.com/AECDocuments.html  AEC-Q100的测试分组如下:  Group A: 加速环境应力测试(PC、THB or HAST、AC or UHST or TH、TC、PTC、HTSL)--共6项测试 在之前的可靠性介绍中,提到了一些实验项目,不再赘述。 封装可靠性之BHAST25 赞同 · 9 评论文章 其他可靠性实验20 赞同 · 10 评论文章 对于PTC再稍作解释,PTC(Power Temperature Cycling),功率温度循环,测定集成电路封装结构承受高低功率循环的能力,常用于功率半导体。在功率循环过程中,施加周期性的功率作用于芯片,芯片产生的热量对芯片及封装可靠性造成严重影响,通常用来模拟应用中遇到的最坏情况。适用于功耗变化≥1瓦,且功率上升时间<0.1秒,预期会导致结温Tj (Junction Temperature)变化≥40°C的组件。 Group B--加速生命周期模拟测试(HTOL、ELFR、EDR)--共3项测试 ELFR早夭实验,3lots, 800pcs/lot,实验条件同HTOL,实验时间一般为48h~168h,用来识别silicon和封装潜在的早期失效风险,早期失效率计算可以参考JESD74A。 EDR Endurance, Data Retention, and Operational Life,评估非挥发性memory器件在多次读写后的持久性能,在重复读写之后加速非挥发性memory器件存储节点的电荷损失。 xianyunyehe:flash可靠性测试24 赞同 · 14 评论文章 Group C – 封装组装完整性测试(WBS、WBP、SD、PD、SBS、LI、BST)--共7项测试  WBS-Wire Bond Shear 引线键合剪切 WBP-Wire Bond Pull Strength 引线键合拉力强度 SD-Solderability 可焊性实验 PD-Physical Dimensions 物理尺寸量测 SBS - Solder Ball Shear 焊球剪切 LI-Lead Integrity 引脚完整性实验 BST-Bump Shear Test bump剪切测试,在之前的版本中没有,J版增加用于FC封装产品。 Group D – 晶圆可靠性试验(EM、TDDB、HCI、BTI、SM)--共5项测试 车规认证对生产有特定要求,一般产线需要做过IATF16949车规认证(16949的认证对象是生产/制造(Fab/OSAT)环节,设计公司不需要此认证),车规认证产线独立于其他产品的生产区域,需要在导车规产品前跟foundry和封装厂确认。 晶圆可靠性验证,一般由晶圆厂提供(EM、TDDB、HCI、BTI、SM),H版本中的NBTI (Negative Bias Temperature Instability)改为新版本中的BTI (Bias Temperature Instability),涵盖对NBTI和PBTI (Positive Bias Temperature Instability)的评估。相应的实验项目我们之前也做过整合,具体可以参考: 器件可靠性小结51 赞同 · 102 评论文章 氧化层的PBTI为什么远小于NBTI?42 赞同 · 6 评论回答 Group E--电性验证测试(TEST、FG、HBM、CDM、LU、ED、CHAR、EMC、SC、SER、LF)--共11项测 试 FG fault grade(故障等级)测试,包括故障模型、覆盖率、缺陷激活条件等,最终提供相应的报告。 Char测试(特性化测试),对芯片的工艺、电压、温度、频率等做遍历测试,保证芯片有足够的设计制造窗口。 HBM、CDM在AEC-Q100 -REV-H中要求较严苛,分别为≧2KV HBM (Classification 2 or better), CDM≧ 750V corner pins ≧ 500V all other pins (Classification C4B or better),随着工艺节点减小后ESD能力降低,且RF对ESD承受度与其他芯片有差异,AEC-Q100 -REV-J修改了ESD要求。  Group F--缺陷筛选测试(PAT、SBA)--共两项测试 PAT--Part Average Testing零件平均测试。PAT是用来检测外缘(Outliers)半导体组件异常特性的统计方法。用以将所有异常零件从所有产品中剔除。 SBA --- Statistical Bin/Yield Analysis 统计良率分析。 Group G--腔体封装完整性测试(MS、VFV、CA、GFL、DROP、LT、DS、IWV)--共8项测试  MS:机械冲击 VFV:变频振动试验,振动实验参考之前的介绍: 机械振动试验42 赞同 · 4 评论文章 CA:恒定加速度,在试验过程中,从X、Y、Z方向(AEC-Q100中仅要求Y1方向),对器件施加规定数值的恒定加速度,来检测在冲击和振动试验中不一定能检测出的结构和机械类型的缺陷。 Gross/Fine Leak:粗细检漏,参考MIL-STD-883E 1014,可理解为检测密封性的试验。 Package Drop:包装跌落试验,不同于之前介绍的产品drop test,package drop是模拟装运货物的包裹在运输和搬运过程中可能经历的跌落。 What Is A Package Drop Test? - Sofeastwww.sofeast.com/glossary/package-drop-test/ Lid Torque:封盖扭矩,将扭矩施加到盖板上,确定抗剪强度。 Die Shear: 芯片剪切测试 苏州科准测控有限公司:半导体集成电路芯片剪切强度测试全面解析!0 赞同 · 0 评论文章 Internal Water Vapor: 内部水汽含量,测定金属或陶瓷封装器件内部气体中水汽含量。 Group G的试验项目也可参考GJB548,有相关的试验介绍,比MIL-STD-883E看起来更方便些。 AEC-Q100-REV-J的更新及与JEDEC的差异 J版本与H版的一些差异,在上文有部分提及,比如增加bump剪切测试;晶圆可靠性中将NBTI修改为BTI,ESD能力对28nm以下和RF芯片适当放宽,其余修改部分包括:使用铜打线(Cu wire)需要取得AEC-Q006验证数据;Grade 0测试循环数由2000 cycles下修至1500 cycles;HTOL实验后的回测顺序,由Room→Cold→Hot可替代为Room→Hot→Cold。 AECQ和JEDEC很多实验项目相同,主要差异是sample size和回测温度差异,具体对比如下:  |