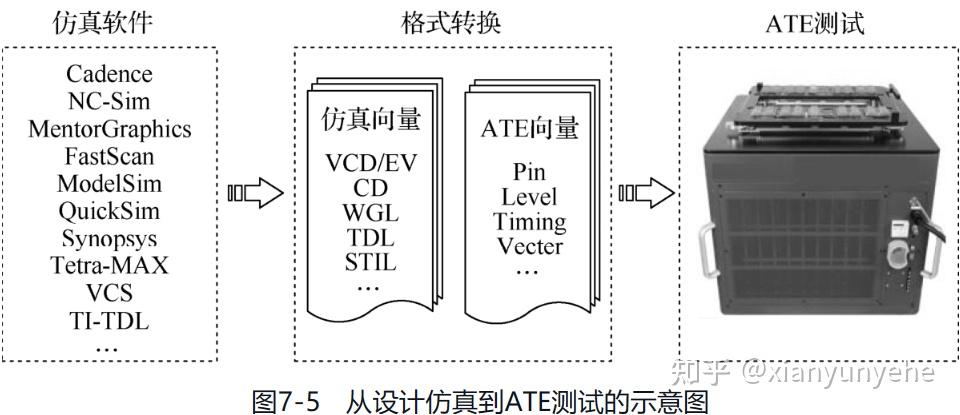

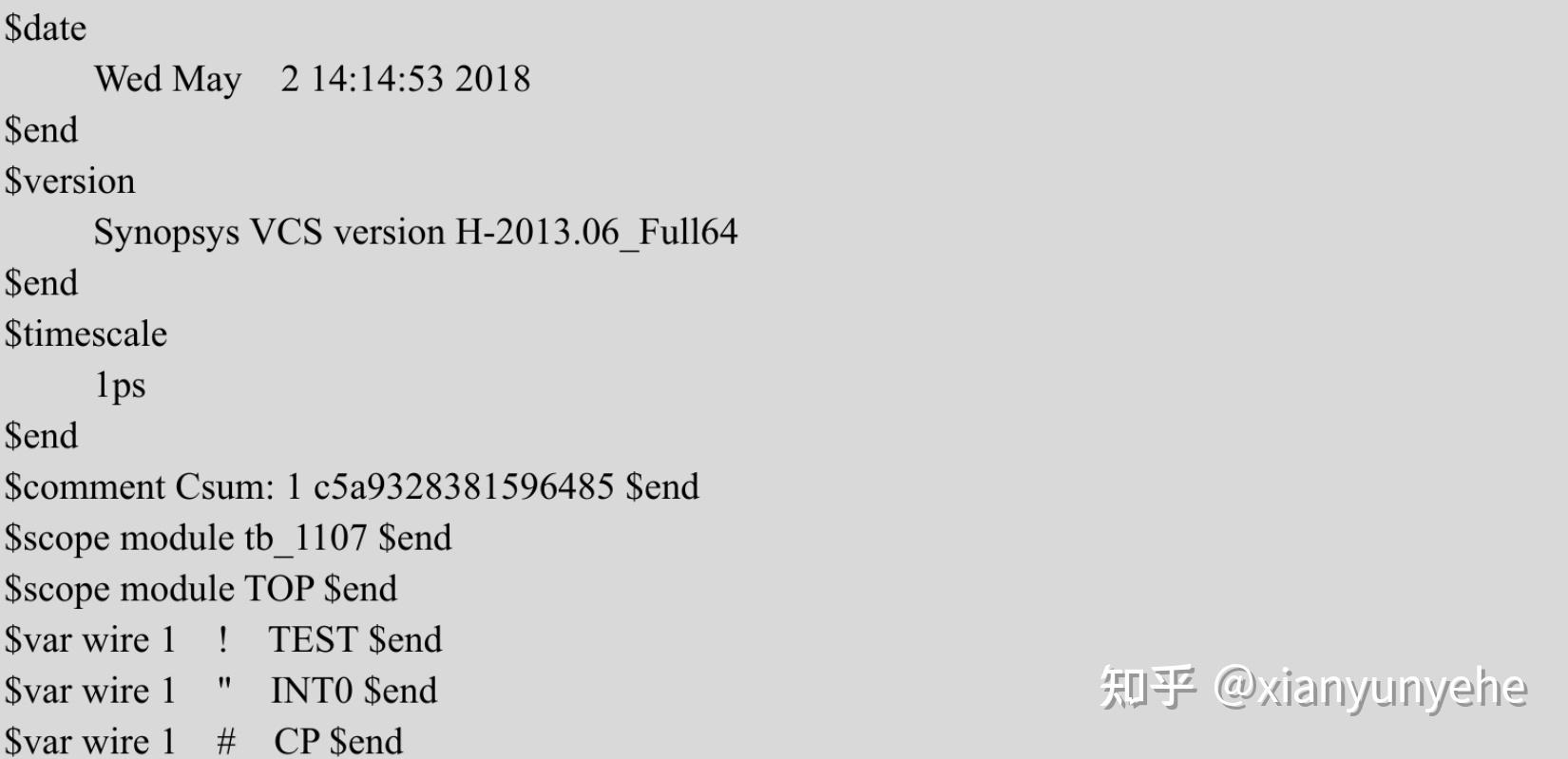

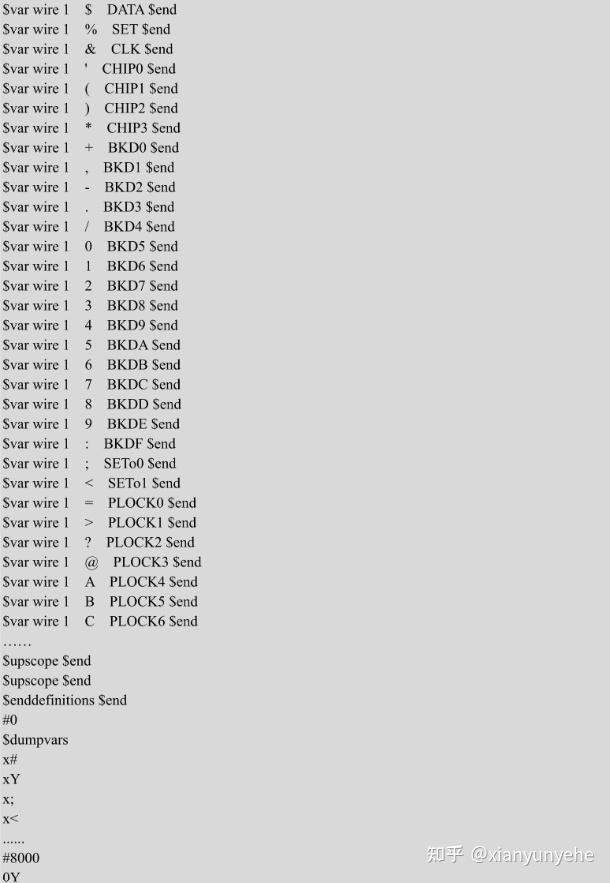

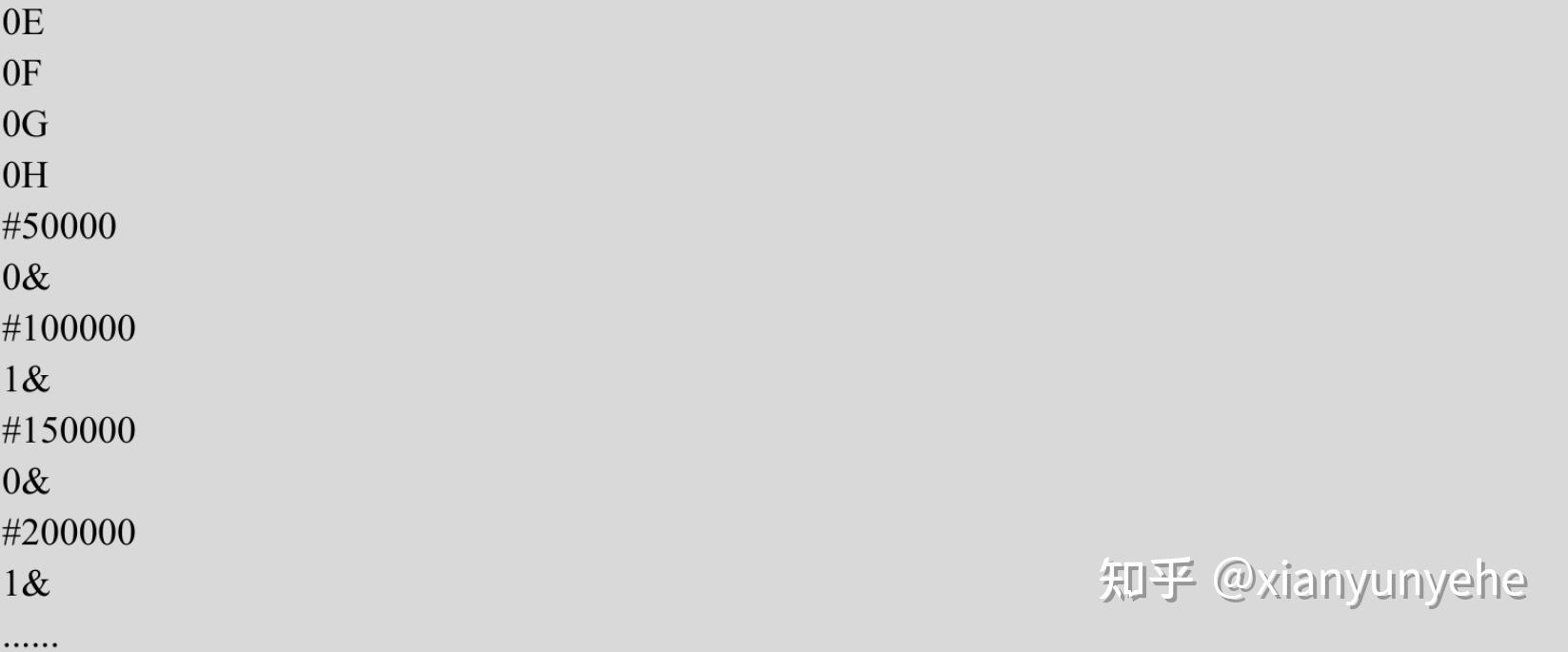

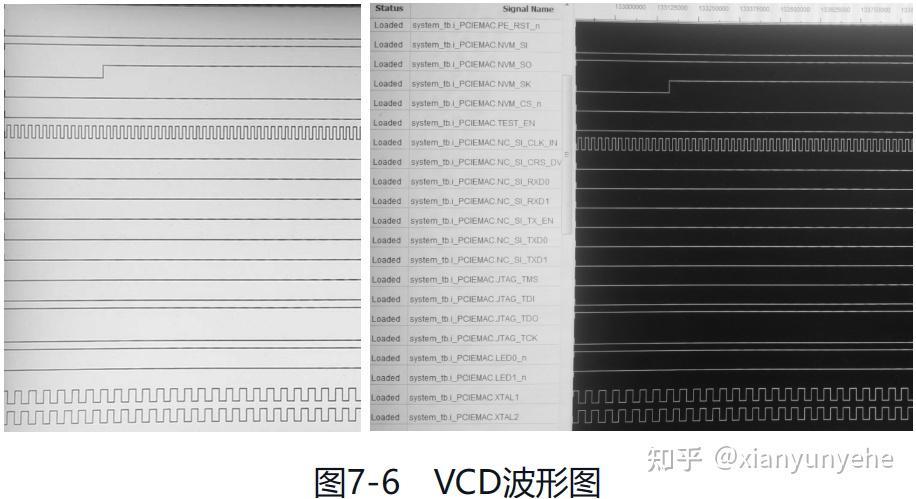

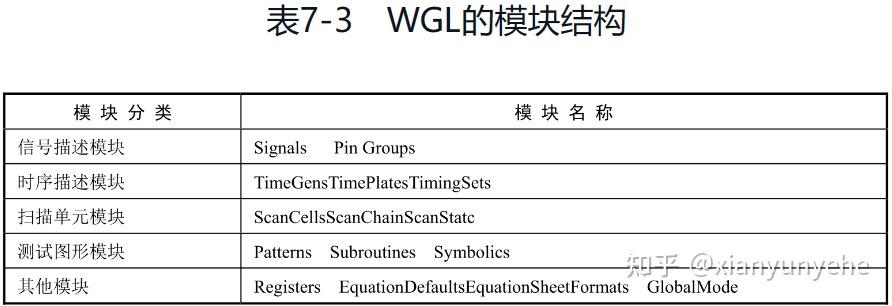

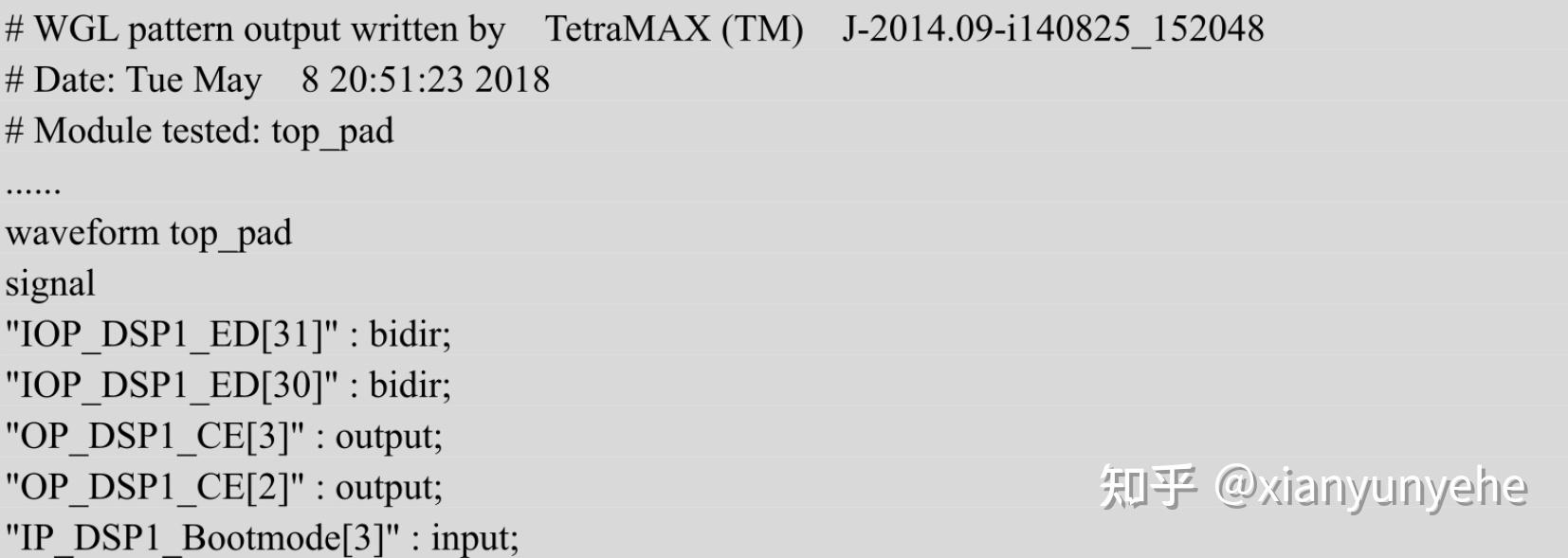

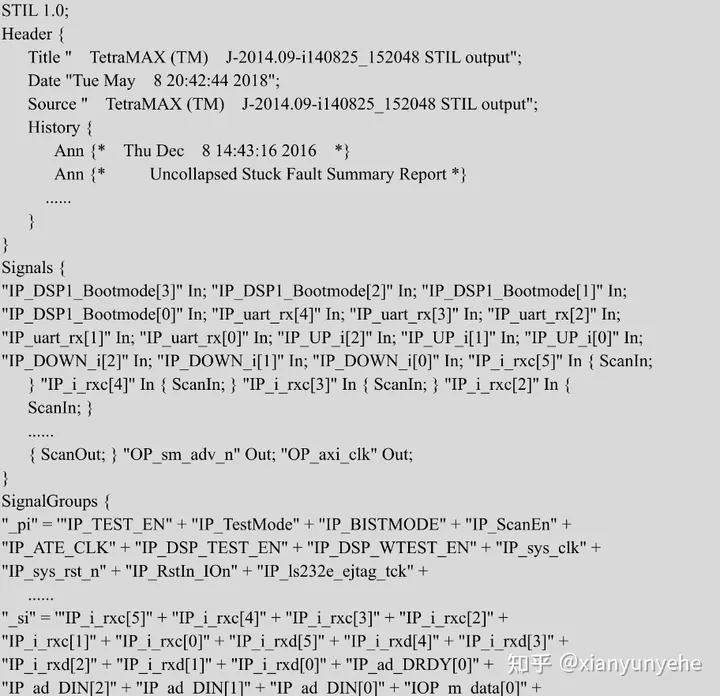

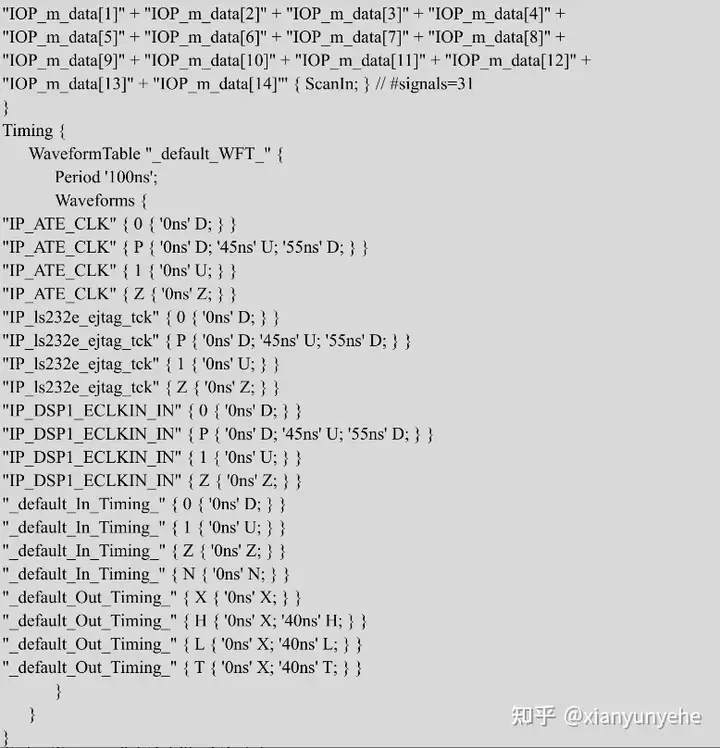

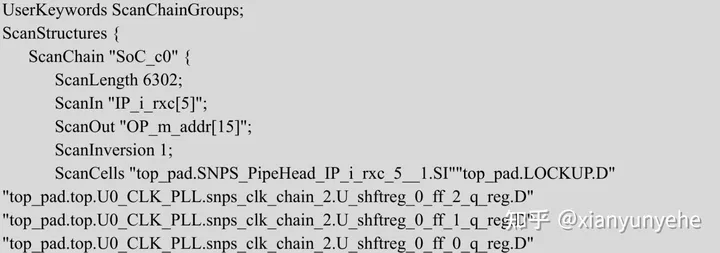

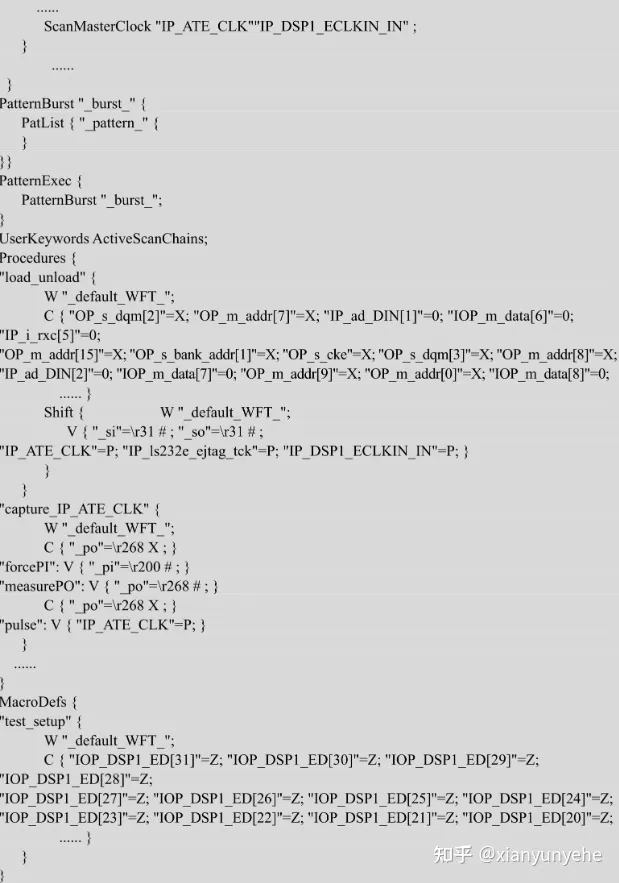

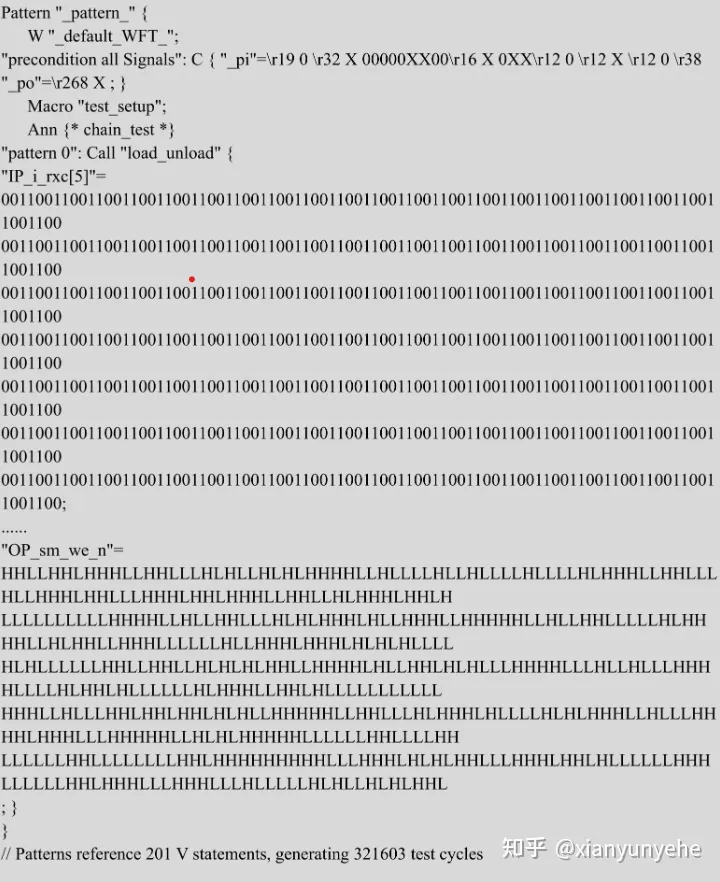

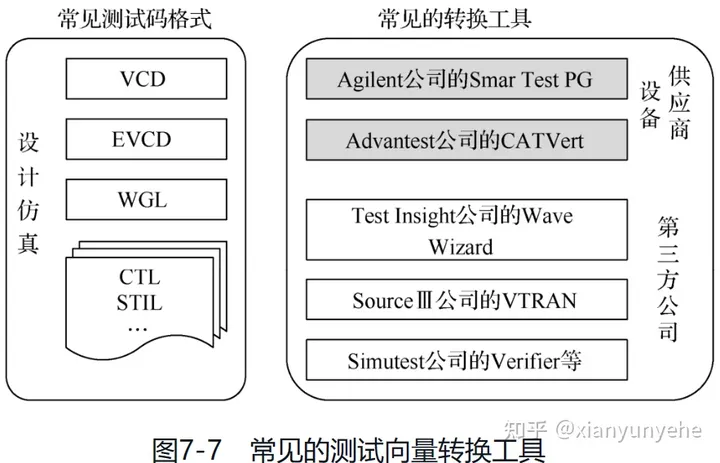

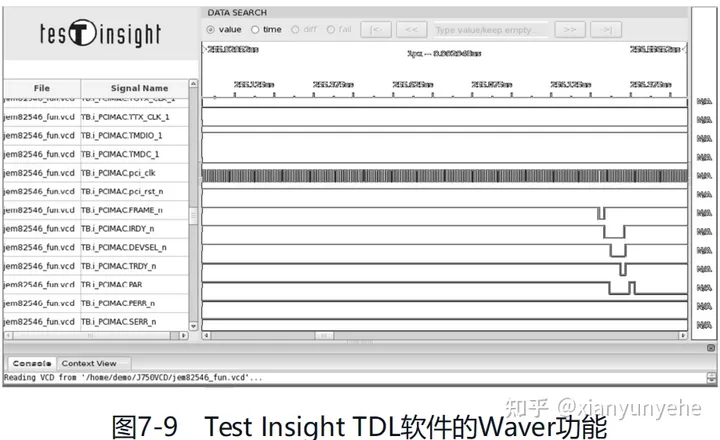

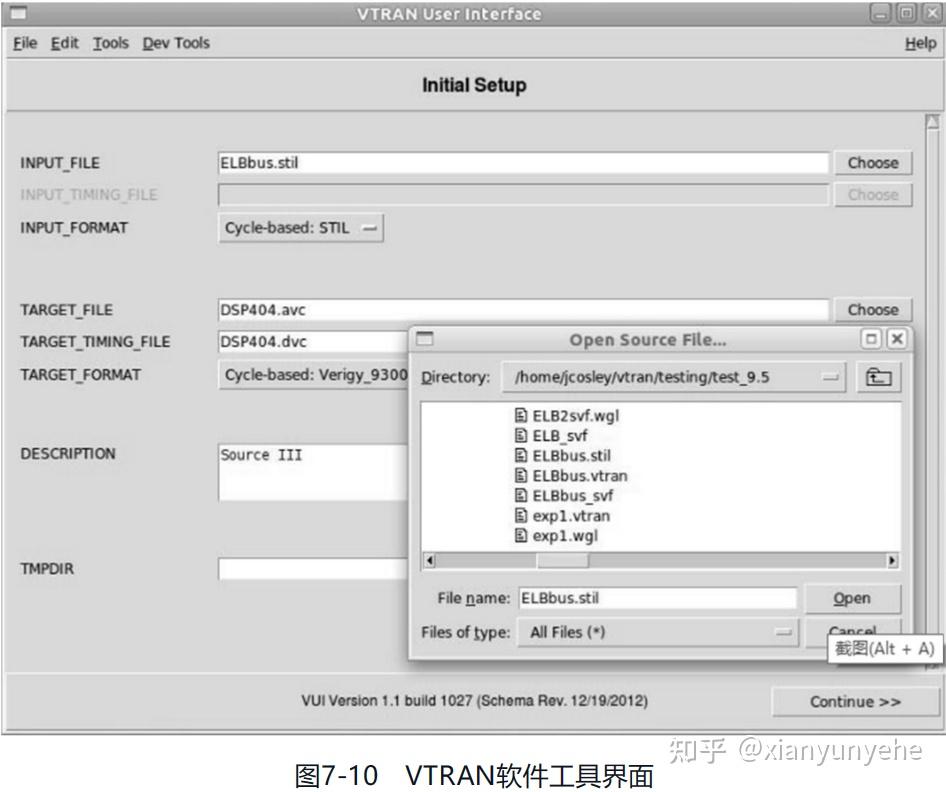

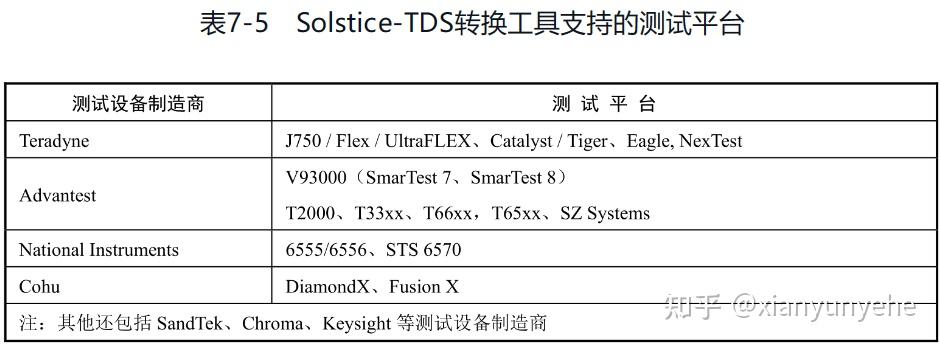

随着集成电路设计水平的不断提高,集成电路的逻辑关系越来越复杂,时序要求越来越严苛,测试已经不可能像早期一样采用人工输入测试向量的方法来实现。目前,在VLSI设计过程中,向量一般是由EDA或ATPG产生的。但是,这些向量一般需要经过格式转换成ATE所能识别的测试向量格式后,才能为ATE所用。测试向量一般包括测试时序(Timing)和测试向量(Vector),均是周期化的结果,其格式与测试平台有关。如前所述,不同厂商的ATE,测试向量格式一般不同,而且产品不断更新换代,即使是同一品牌的ATE,其测试向量的格式也可能不相同。从设计仿真到ATE测试的示意图如图7-5所示。 常用仿真向量格式 常用的仿真向量主要有VCD、EVCD、WGL、STIL等,不同类型的EDA软件一般会使用不同的仿真向量格式。基于结构测试类的仿真输出一般为WGL格式的向量,基于功能测试类的仿真输出一般为VCD/EVCD格式的向量,最新的软件工具一般支持目前较先进的STIL格式的仿真输出。 1.VCD格式 VCD(Value Change Dump)格式是IEEE 1364标准的一部分,它是由Verilog硬件描述语言发展而来的,遵从Verilog的语法规则。VCD格式是基于事件形式的语言,它描述了器件在某一时刻引脚状态的数据规范,采用直线型结构的文件形式,文件内容主要是设计模型中基于事件变化的信息,具体表现为器件某一时刻的输入/输出状态。人们在2001年又对其进行了扩充,增加了方向性和可描述的事件的种类,称其为EVCD(Extended Value Change Dump)文件。 在VCD文件中包括12个以$开头,以$end结束的关键词。这些关键词可分为描述性关键词与仿真性关键词。描述性关键词用于说明文件的基本情况,主要包括生成时间、时间单位、仿真版本信息、引脚信息及注释等。仿真性关键词代表文件的主体,主要用来记录关键值的变化信息。VCD文件的关键词如表7-1所示。  VCD文件以零时刻为起点,主要包含0、1、x、z等电平信号的事件集合。它是测试程序开发过程中被使用最广泛的仿真向量。在下一次跳变之前,每个信号状态会保持上一状态。VCD文件的时间分辨率比较高,可以达到10ps、1ps甚至10fs,因而可以包含丰富的时序信息。VCD文件是一种文本文件,可用文本编辑工具进行编辑,主要包含以下内容。 (1)VCD文件仿真生成时间。 (2)仿真工具名称及其版本信息。 (3)时间分辨率(Timescale)。 (4)信号定义:每个信号用一个简单字符表示,同时指出信号的宽度。若信号为非总线信号,则宽度为1。 (5)信号的初始状态设置。 (6)信号的跳变信息,“#”后的数字代表动作时刻。VCD文件例子如下:    使用EDA工具(如Novas Software公司的Debussy)打开VCD文件就可以直观地查看测试图形,VCD波形图如图7-6所示。  2.WGL格式 WGL(Wave Generation Language)格式用于描述扫描结构和状态,测试图形的时序和数值。它是一种允许变量定义和内嵌方程表达的数据描述性语言,能够同时支持硬件扫描结构和测试程序的生成。WGL作为典型的周期化文件,其应用十分广泛,但它只是由一家公司提出的,尚未成为IEEE标准。WGL最初只是一种在TDS软件周期化工具——Wave Maker's Editor中使用的辅助性描述语言,用来转换或编辑波形数据库(WDB)中的数据。但由于其被一些测试仪器支持,所以也得到了大家的认可。WGL中的关键词如表7-2所示。  从关键字数量可以看出WGL比VCD复杂了许多,它的模块结构如表7-3所示,包括信号描述模块、时序描述模块、扫描单元模块、测试图形模块等。  WGL格式例子如下:   3.STIL格式 STIL(Standard Test Interface Language)格式是一种数字测试向量生成工具与测试设备交互的语言,同样是基于ASCII码的文件格式。STIL文件既有周期型也有事件触发型的描述方式,可以说是对VCD文件和WGL文件的完美结合。数字测试向量的标准测试接口语言(即STIL)的IEEE 1450标准在1999年得到了IEEE标准联合组织的批准[插图],目前IEEE 1450标准已扩展为6个版本。STIL相关标准如表7-4所示。  STIL格式作为集成电路设计到测试的标准数据格式受到了美国的TI、Intel、IBM、Freesacale等巨头及日本以Toshiba为首的集成电路制造厂商的支持[插图]。此外,有关STIL的一些产品也开始得到应用,如Synopsys公司的TetraMAX和Mentor公司的FastScan等均支持WGL和STIL格式。STIL成为EDA-ATE间的标准接口是大势所趋。 在STIL语言中,数据结构的基本单位是块,相同的数据类型都被定义在相同类型的块内。STIL格式主要包含文件说明块、信号组块、信号块、时间定时组块、测试图形块等,各模块具体说明如下所述[插图]。 (1)文件说明块:包括文件名、文件类型(包含事件型向量和周期型向量)和向量总时间长度等[插图]。 (2)信号组块:根据不同条件对信号进行分组,形成信号组块。总线信号一般以组的形式存在。 (3)信号块:包括信号与定时关系块、信号组与信号关系块、信号说明块等。信号与定时关系块对每个定时组包含的信号名称进行定义,并且规定了每个信号的详细跳变时间(如输入的驱动前后沿、输出的响应前后沿等)。 (4)时间定时组块:包括测试周期、定时组号、组名等。时间定时组块可省略。 (5)测试图形块:包括测试图形符号类别、块说明信息、测试向量及测试向量与定时关系块等。对于事件型向量,测试图形块主要存储信号波形跳变数值与时间;而对于周期型向量,测试图形块主要存储周期变化的定时组号与测试向量。 STIL格式例子如下:      2.常用的测试向量转换工具 在基于ATE的测试程序开发流程中,测试向量转换是一个重要步骤[插图]。测试向量的格式转换主要是将面向事件的仿真向量分割成可供测试使用的周期性测试时序和测试向量。 国际上一些知名测试设备供应商在销售ATE的同时,也提供配套的测试向量转换工具,如美国Agilent公司的Smar Test PG、日本Advantest公司的CATVert等[插图],常见的测试向量转换工具如图7-7所示。还有一些第三方公司也提供类似的软件,如以色列Test Insight公司的Wave Wizard、美国Source III公司的VTRAN、美国Simutest公司的Verifier、美国TSSI公司的TDS等。  这些进口工具已经在行业内广泛应用,相对而言,国产工具还比较薄弱,它们所面临的核心问题是周期化算法及转换效率。 1.Test Insight TDL(Tester Data Link)转换工具 以色列Test Insight公司专注于开发从EDA到ATE的转换软件,这些软件通常都支持市场主流ATE的开放式文件格式转换。例如,Teradyne、Advantest、LTX-credence等ATE机台所需的向量文件、时序文件、通道定义文件等,它们的通用性较好。 TDL是Wave Wizard的升级版本,具有更为强大的功能和转换效率。目前一些主流ATE厂商都在设备测试软件中集成了Test Insight的软件转换工具。 Test Insight TDL软件(见图7-8)主要包括VCD2STIL和ATEGen两个部分。VCD2STIL可以将VCD或EVCD格式转换为STIL周期化格式,实现从仿真文件到STIL的快捷转换;ATEGen则可以将STIL格式文件进一步转换为ATE所需的程序文件。图7-9所示为Test Insight TDL软件的Waver功能。   2.Source III公司的VTRAN软件 美国SourceIII公司的VTRAN软件也是一款自动化测试向量转换工具,由于VTRAN提供了一整套批处理命令用于提高转换效率,其转换效率较高,得到了广泛的应用[插图]。图7-10所示为VTRAN软件工具界面,VTRAN的主要应用包括: (1)将仿真数据文件转换为同其他仿真工具兼容的格式; (2)将状态数据文件转换为同仿真工具兼容的文件; (3)修改仿真数据文件,包括更改引脚顺序、引脚列表、时间偏移、时序和时间精度等文件内容; (4)将仿真/ATPG生成的向量转换为测试平台数据文件,再进行Verilog/VHDL仿真和验证; (5)将仿真/ATPG生成的向量转换为ATE使用的功能测试向量; (6)充作图形波形工具的上一端,用于读取和显示向量数据文件。  3.TSSI TDS转换工具 美国的TSSI是一家提供从电子设计到测试自动化全过程解决方案的公司,WGL语言就是TSSI的主要贡献之一。Solstice-TDS是一款测试程序开发软件,由TSSI公司开发,其主要功能是转换各种不同格式的EDA-ATE测试程序文件,Solstice-TDS是一款支持市场主流ATE厂商的转换软件。Solstice-TDS转换工具支持的测试平台如表7-5所示,图7-11所示为Solstice-TDS工具WaveMaker Flow-Based的转换流程。   Solstice-TDS软件与其他向量格式转换软件相比,具有更高效可靠的图形化操作界面;具有功能丰富的波形读取和显示工具;转换速度快,转换效率高,并针对测试仪使用的资源和性能进行了优化;具有转换前后波形比较验证的功能等。 |