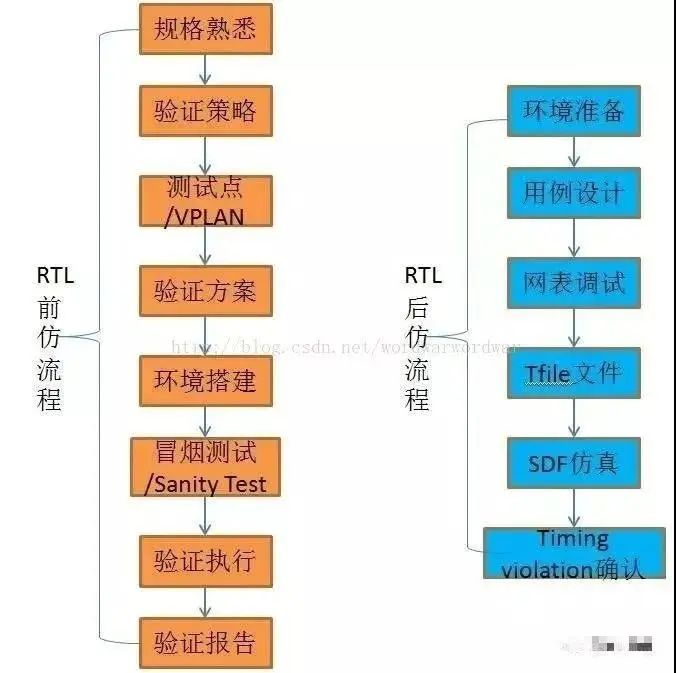

数字验证处于数字IC设计流程的前端,属于数字IC设计类岗位的一种。主要是对数字前端的设计做验证。随着芯片规模不断加大,在IC设计过程中验证的复杂度也进一步加到,需要的用到的岗位人数也越来越多;很多大公司,数字前端设计工程师与验证工程师的比例应该达到1:3,但实际上却是3:1。 正因为芯片的高风险,才凸显了验证的重要性。在流片之前,通过验证人员的验证活动,发现所有的设计bug,这就显得特别重要。 下图是一副比较完整的芯片端到验证端流程图,大多数公司的验证流程是大同小异的,差异点在于各个流程中具体做的事情。  验证做任何事情都需要按照一定的流程来走,否则很容易陷入混乱之中,对刚入门的新手来说,更是如此。通用流程大致如下: 1)提取测试点,明确验什么 分析FS/浮点平台,提取芯片的规格及测试点; 分析AS/定点平台,提取测试点; 分析DS,提取测试点并识别asic与算法的不一致点。 2)制定验证方案,明确怎么验 刷新测试点列表,明确测试点的覆盖方式:功能覆盖率、代码覆盖率、直接用例; 验证环境的搭建策略,这个步骤是可以做成自动化工具的; 验证的重点难点,提前识别重难点,并制定相应的对策; 刷新用例列表,明确测试用例的方法及步骤。 3)用例执行,随机测试,发现bug 执行直接用例,发现大部分的bug; 带随机的大量测试,试图撞出bug。 4)完备性分析,确保无漏验 FA/AS完备性确认,确认FS/AS中的所有点都已纳入测试点,并确保已被覆盖,包括应用场景; 接口完备性确认,保证所有的接口时序都已覆盖,包括正常时序及异常时序; 覆盖率确认,分析所有的代码覆盖率、功能覆盖率,保证全部覆盖; 代码分析,熟练掌握电路的实现逻辑,保证所有的电路corner都已覆盖。 上述这几个步骤是一个比较规范的流程,只要每个步骤都做好,基本就能做到无漏测、零漏验。 形式验证目前还不能完全取代模拟仿真验证。两者各有所长,技术互补,在验证过程中应该结合使用,争取找出设计中所有的bug! |