本篇文章将进入芯片的Physical Domain,后面的几篇文章也都是物理设计相关的内容,本系列文章侧重于从电路的角度去思考,而不是从EDA的领域思考,对这方面的实现算法特别感兴趣的可以看EDA相关的课程。本篇文章有一些图片也来自下面这两个知乎文章介绍的一些课程(请见阅读原文),不一一说明了,在此表示感谢。

接下来进入课程内容:

本节课的课程大纲如下所示:

1、Moving to physical domain

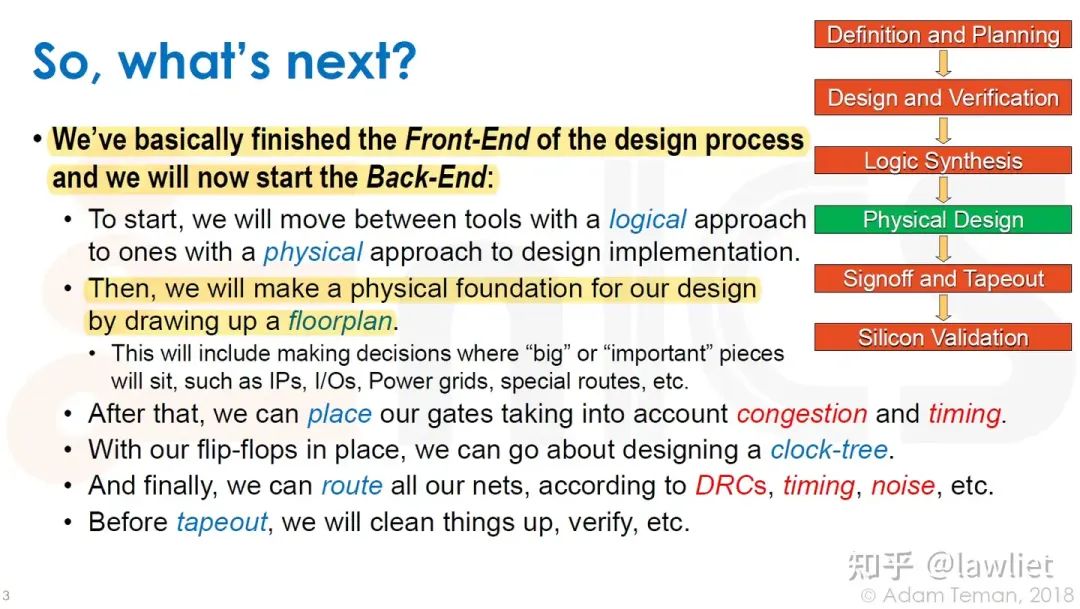

在之前的文章中,我们已经讲解了芯片的前端设计流程,现在我们将正式进入芯片后端的学习。芯片后端设计,也称为物理设计,是在前端设计完成后进行的。它涉及到将前端设计得到的网表转换为实际的几何形状,即进行布局和布线(Place and Route, P&R)。后端设计还包括芯片的时序分析、功耗分析、信号完整性分析、热分析等多个方面。后端设计工程师需要确保芯片的物理设计满足所有性能和制造的要求。

1.1、Floorplanning

我们看一下后端每一步的流程。物理设计的基石,同时也是第一步,便是Floorplanning,中文名一般叫做布局规划。这个过程包括了对设计中较大的或重要的部分进行空间分配和布局决策,比如数字、模拟电路的位置、面积、形状等的规划,更具体点,比如各种IP核、输入输出、电源网络、特殊的线路等的大致位置所在。

1.2、Placement

在完成floorplan以后,下一步是Placement即布局过程,其实就是解决逻辑Cell怎么放的问题。这个阶段的任务是将设计的各个逻辑门和模块放置到芯片上的具体位置。

其主要包括:

· 全局布局:进行粗略的布局优化。

· 详细布局:进一步优化每个标准单元和宏单元的位置。

· 优化:针对时序、功耗等进行局部优化。

· 验证:设计规则检查(DRC):确保布局满足所有工艺和设计规则,电气规则检查(ERC):确保布局不会导致电气问题(例如,电流密度过高)。

在Placement过程中,需要重点考虑以下几个关键因素:

拥塞(Congestion):拥塞是指在芯片布局中某些区域可能会出现过多的逻辑门和连接线,导致布线困难。在放置过程中,需要尽量减少拥塞,确保布线通道的畅通,避免在后续的布线阶段出现严重的问题;

时序(Timing):时序是指信号在芯片中传播的时间。在放置过程中,需要确保所有的时序要求都能得到满足,以保证芯片能以预定的速度运行。通常涉及到对关键路径优化。很多时候我们说让后端修时序,就是指这个。但实际上后端能做的有限,前端设计尽可能不要出现时序违例。

1.3、Clock Tree Synthesis

在完成place以后,下一步是时钟树综合过程。时钟树综合(Clock Tree Synthesis, CTS)是芯片物理设计中的一个重要环节,它的目的是确保时钟信号能够均匀且同步地到达芯片上的所有触发器。时钟树的目的是减少时钟偏斜(clock skew),即时钟信号到达不同触发器的时间差异,因为时钟偏斜会限制芯片的最大工作频率,影响性能。时钟树设计的主要步骤包括:

时钟树综合:使用电子设计自动化(EDA)工具对时钟网络进行分析和设计,以确定如何将时钟源分配到所有的触发器。工具会尝试最小化时钟偏斜,同时考虑到时钟网络的功耗和插入延迟(insertion delay);

时钟树插入:在时钟源和触发器之间插入缓冲器(buffers)和驱动器(drivers),以构建时钟树。这些缓冲器和驱动器会帮助均衡时钟信号,确保信号能够以最小的偏斜到达每个触发器。此外还包括一些后续的优化。大家这里可以简单理解时钟树综合,其实际上就是插各种各样的buffer,以避免不希望的clock skew。

1.4、Routing

在完成时钟树综合以后,下一步是布线即routing过程。也就是应该如何连。布线的目的是将所有放置好的逻辑门和模块之间的连接线(nets)连接起来,确保信号可以正确地在芯片上传播。在布线过程中,需要遵循一定的规则和约束,主要包括:

设计规则检查(Design Rule Checks, DRC):DRC是一系列制造工艺相关的规则,它们确保芯片设计可以在这个工艺下正确制造。布线时必须遵守这些规则,比如线宽、线间距、金属层的垂直交叉规则等,以避免制造过程中的问题;

时序(Timing):布线时需要考虑信号的传播延迟,确保所有信号的时序满足设计要求。时序分析工具会帮助设计者识别并解决可能导致时序问题的问题,如过长的布线或拥塞区域;

噪声(Noise):布线过程中还需要考虑信号完整性问题,包括电磁干扰(EMI)和功率噪声。合理的布线策略可以减少信号之间的干扰,避免信号失真和性能下降。

我们通过一个图总结一下上述的几个概念:

后面的文章会重点再讲解Placement、时钟树综合以及Routing。

在tapeout之前,我们必须完成上述的任务,确保没有不可控的error和warning。

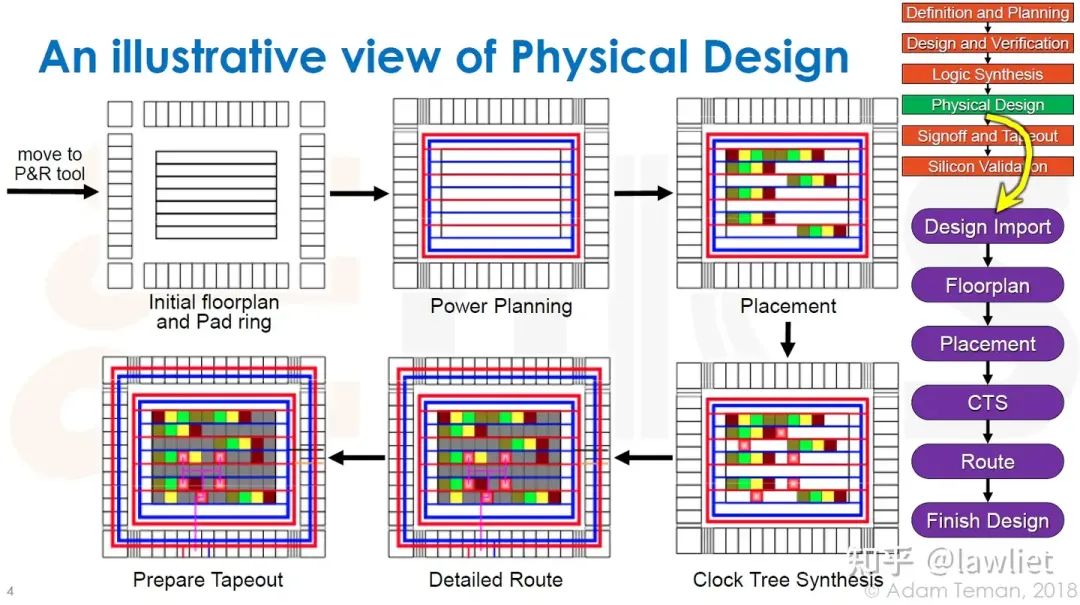

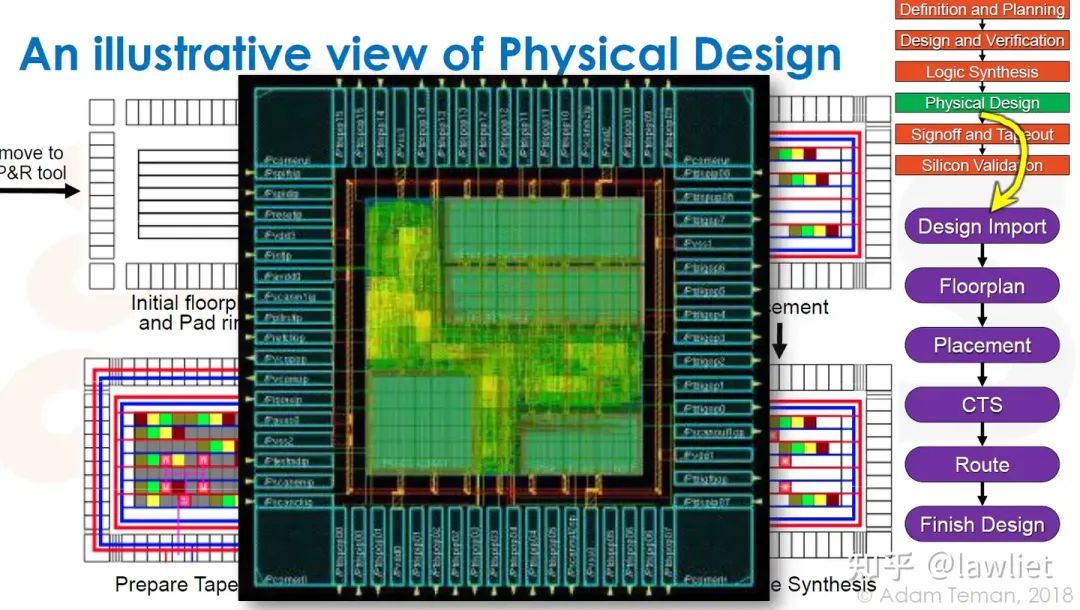

下图是上述流程的一个具体示意图。可以看到其层层递进,从网表一直到最后的版图。

1.5、物理设计前的一些准备工作

在完成逻辑设计以后,我们进入芯片的物理设计。Floorplanning是是物理设计的第一步,它定义了芯片的大致布局。在这个阶段,设计者会决定哪些组件放在哪里,如何安排电源和时钟网络,以及如何优化信号流。这些决策将直接影响芯片的性能和制造难度。

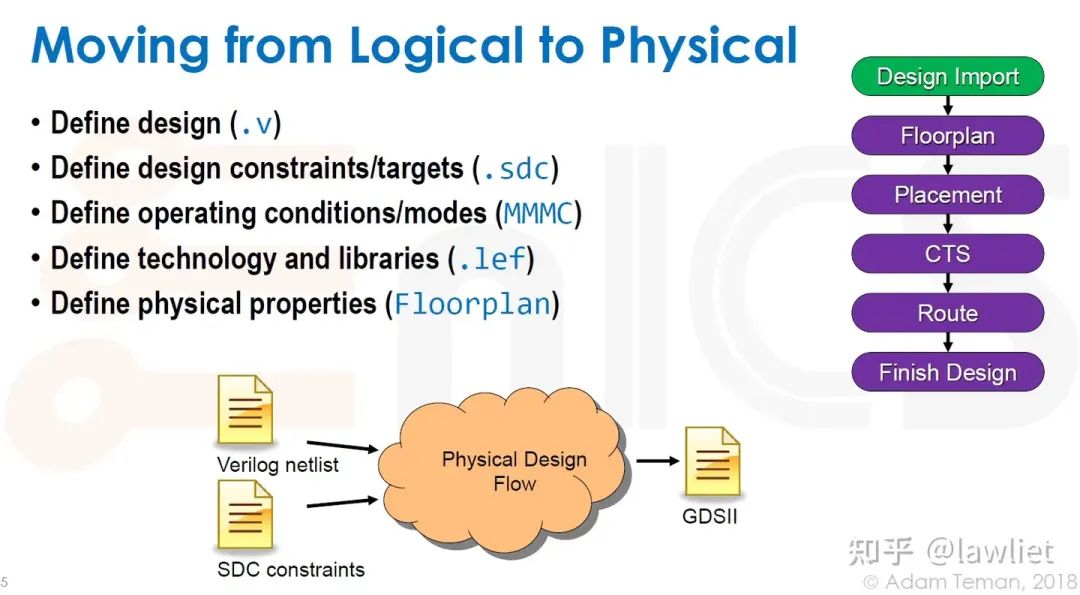

在Floorplan之前,我们还可以认为有导入设计这一步,这一步其实就可以理解为准备原材料,我们简单过一下这一部分PPT即可。

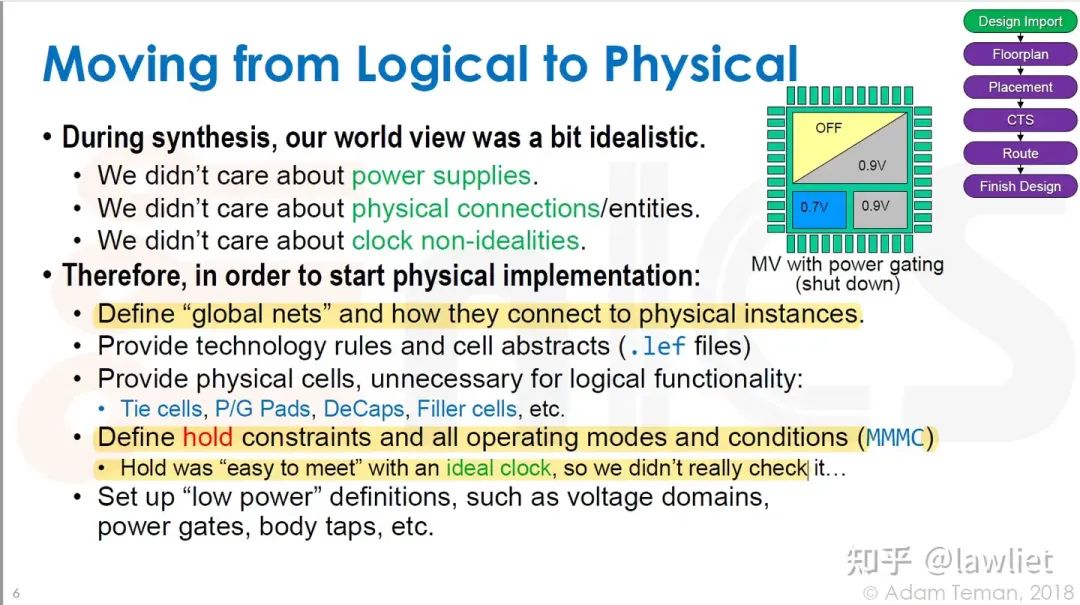

在逻辑设计阶段的综合部份,我们认为芯片面对的世界是相对理想的。如下所示,我们很多东西都没有考虑。我们通常不会过多考虑电源网络的设计和分布,如电源线、地线的布局,以及电源噪声对电路性能的影响。也不涉及具体的物理连线,如金属层的布线、通孔(vias)的使用,以及信号在芯片上的实际路径。

但是既然已经进入物理设计了,那自然而然需要考虑很多物理特性,这也是一些更底层的东西。

首先需要定义“全局网络”及其如何连接到物理实例:全局网络通常指的是那些需要在整个芯片上传播的信号,如时钟信号和复位信号。需要定义这些信号如何连接到芯片上的各个物理实例,例如逻辑单元和宏单元。

提供技术规则和单元抽象(LEF文件):LEF(Library Exchange Format)文件包含了工艺库中标准单元、宏单元等物理信息,如尺寸、布局和电气特性。这些信息对于物理设计至关重要,因为它们决定了设计中的各个组件如何在物理层面上实现。

提供物理单元,这些单元对逻辑功能不是必需的,综合的时候往往会禁用这些单元:这些单元包括:Tie cells: 用于提供逻辑上的高电平或低电平。P/G Pads: 用于芯片与外部电源的连接。Decaps: 用于电源和地之间的噪声过滤。Filler cells: 用于填充芯片上的空白区域,以提高制造良率。

定义保持约束以及所有操作模式和条件(MMMC):在理想的时钟模型中,保持约束很容易满足,因此通常不会进行检查。但在物理实现中,需要考虑时钟的非理想性,如时钟偏斜和抖动,并定义相应的约束。

设置“低功耗”定义,例如电压域、电源门控等:为了实现低功耗设计,需要定义电压域,即芯片中不同部分可以独立操作的不同电压级别。此外还包括power gates,body taps等。

2、A bit about Multiple Voltage Domains

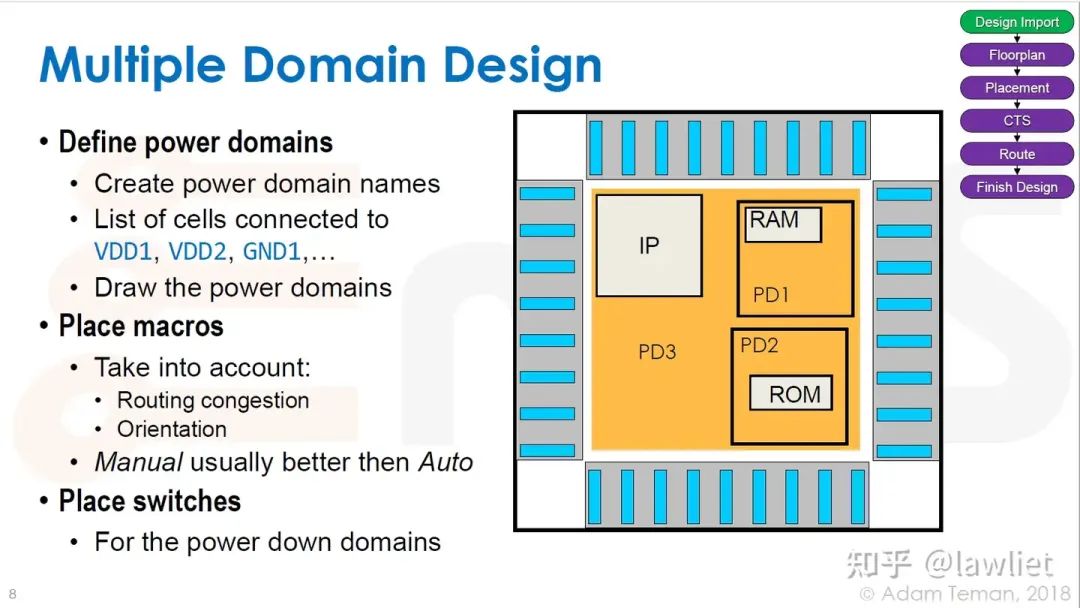

为了节省能耗,目前芯片设计普遍采用多Power Domain。对于每个电源域,需要确定连接到该域的电源(如VDD1, VDD2)和地(如GND1)的单元列表。这些单元在电源域中共同开启或关闭。然后需要绘制电压域,在芯片的布局中,需要明确地标识出每个电源域的范围。这通常涉及到在芯片布局图上绘制电源域的边界,以及确定电源和地网络的连接方式。

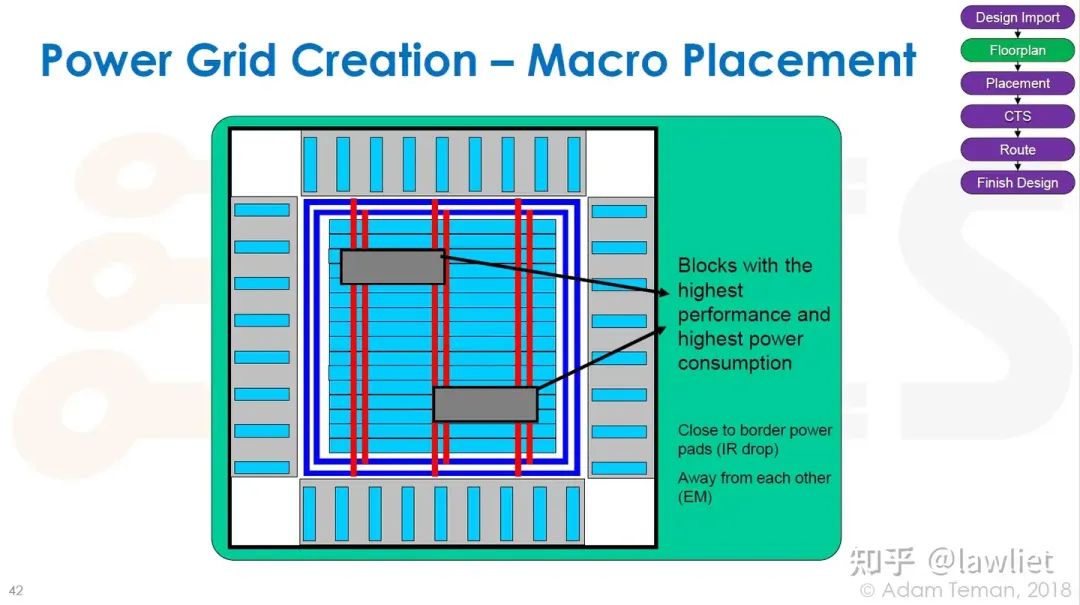

接着需要放置宏单元(macros)。宏单元通常指的是较大的设计模块,如处理器核心、内存块、模拟电路等。以下是在放置宏单元时需要考虑的因素:

路由拥塞(Routing Congestion):在放置宏单元时,需要考虑芯片上的路由通道,避免在某些区域放置过多的宏单元,导致路由通道拥塞,影响后续的布线。

方向(Orientation):宏单元可以有不同的放置方向。在放置时,需要根据宏单元的连接需求和芯片的整体布局来选择最佳的方向,以减少信号线的长度和交叉,优化布线。

手动放置通常优于自动放置(Manual usually better than Auto):虽然现代EDA工具可以自动放置宏单元,但在某些情况下,手动放置可以提供更好的布局和布线结果。手动放置允许设计者根据经验和设计特定要求来进行优化。

然后需要放置开关:对于需要电源管理的电源域,需要放置电源开关(power switches),这些开关用于控制电源域的开启和关闭。放置时需要考虑开关的位置,以便于与电源域中的单元连接,并确保开关的动作不会影响其他电源域。

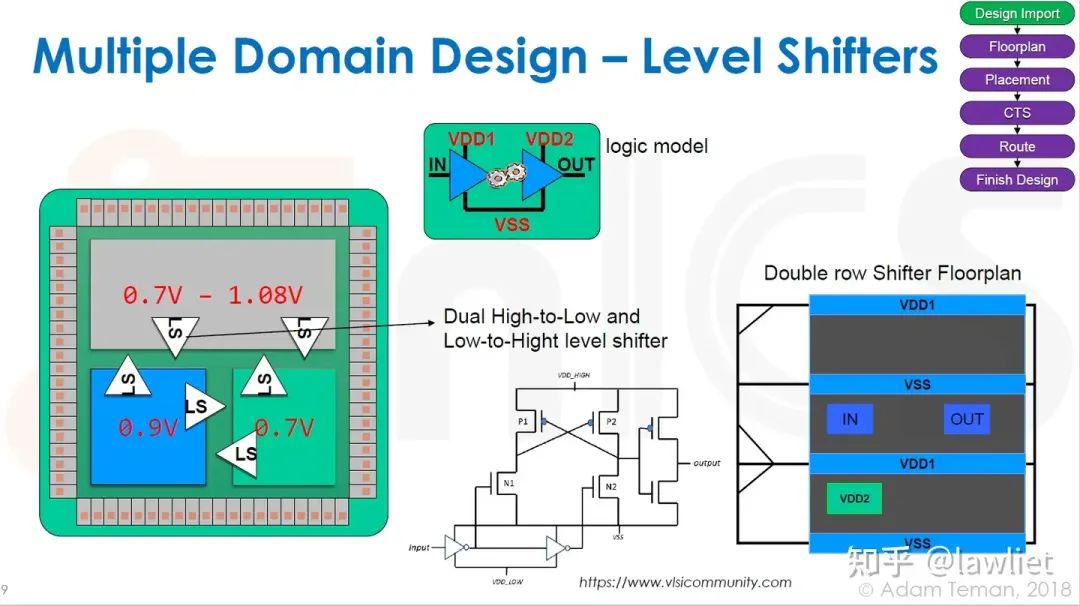

接下来是多电压域用到的模块:Level Shifters,上篇文章我们已经简单介绍过,具体的内容大家可能需要学习一些模拟IC的东西才能掌握清楚,这里简单看一下即可。

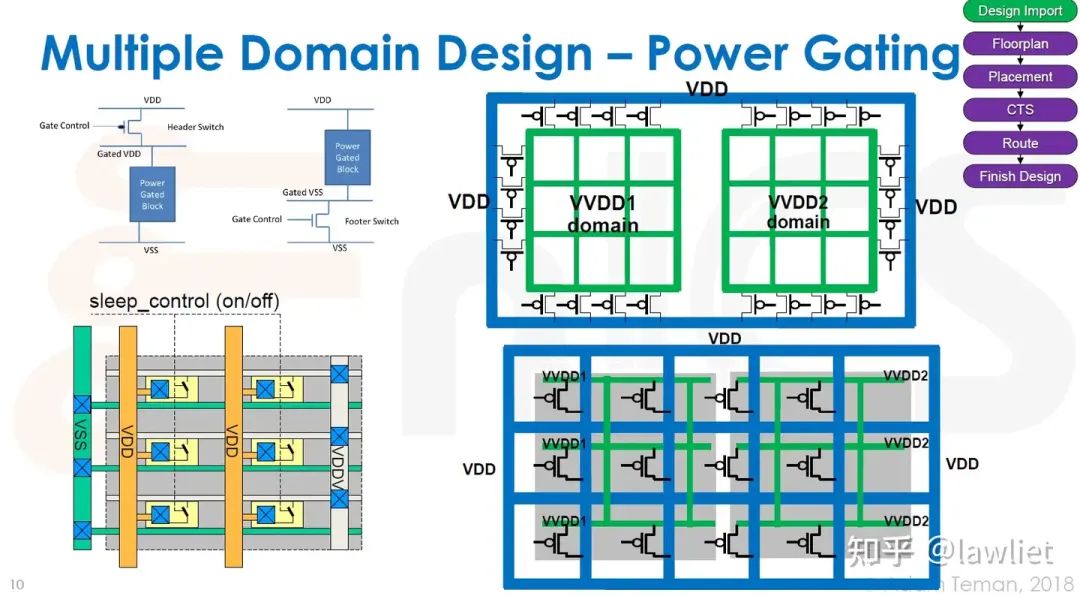

为了提高能效比,设计师通常会将芯片划分为多个电源域,每个电源域可以在不需要时关闭电源,从而降低整体功耗。这也就是Power Gating。

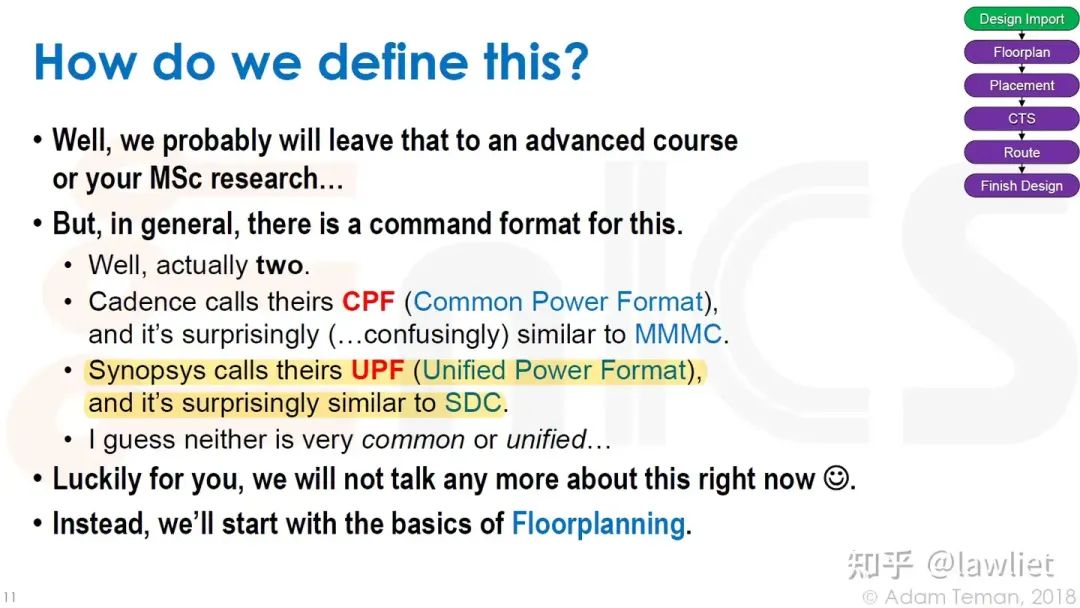

到目前为止,我们已经大概了解了多电压域的一些东西。我们如何定义它们?用的比较多的是UPF文件格式。这一部分大家可以自行搜索相关资料(B站直接搜UPF就有一些视频),本门课程本质还是一门通识课程,所以不会所有内容都具体深入讲解。

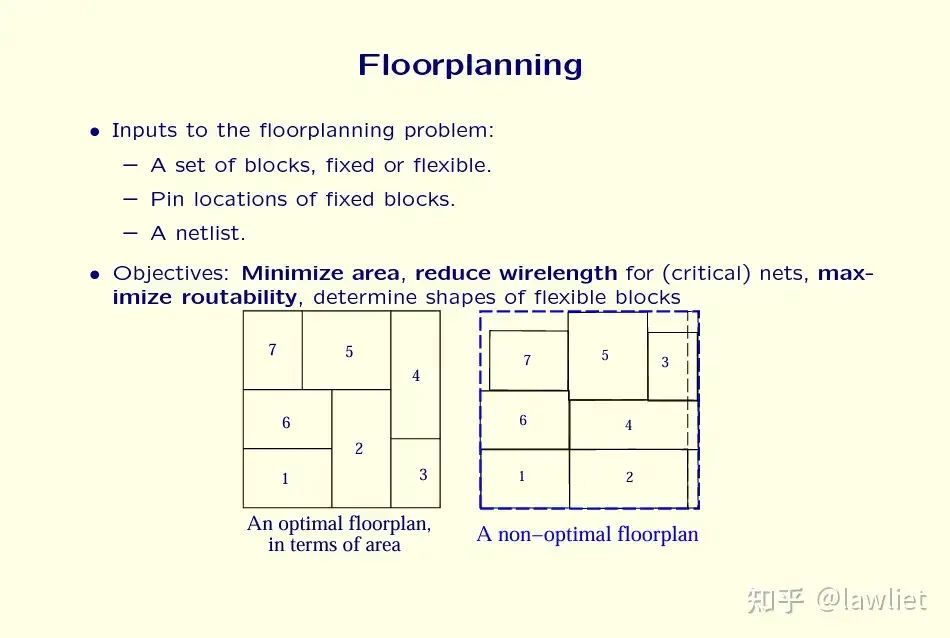

3、Floorplanning

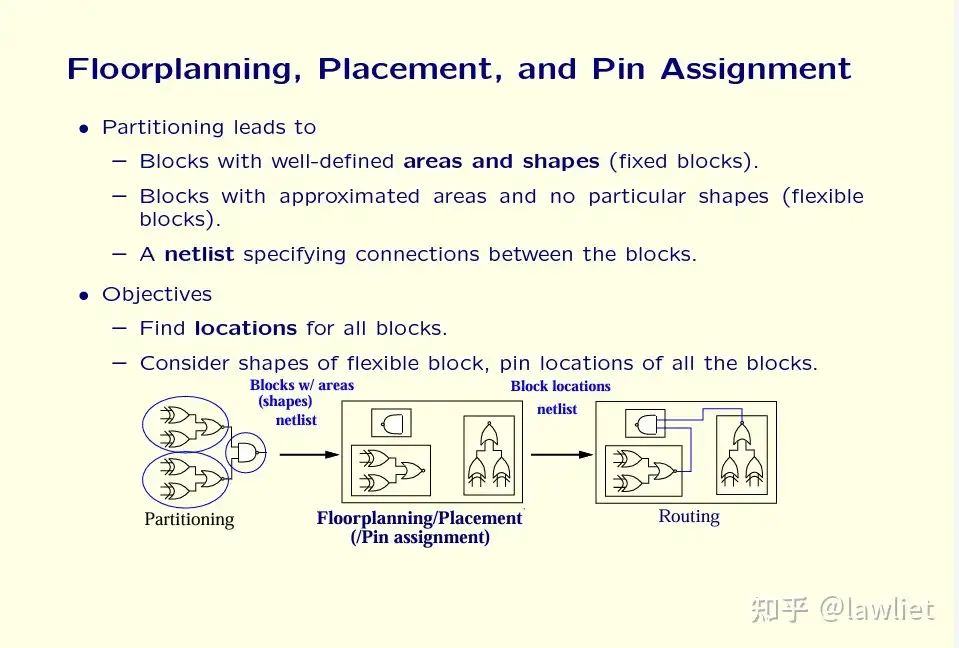

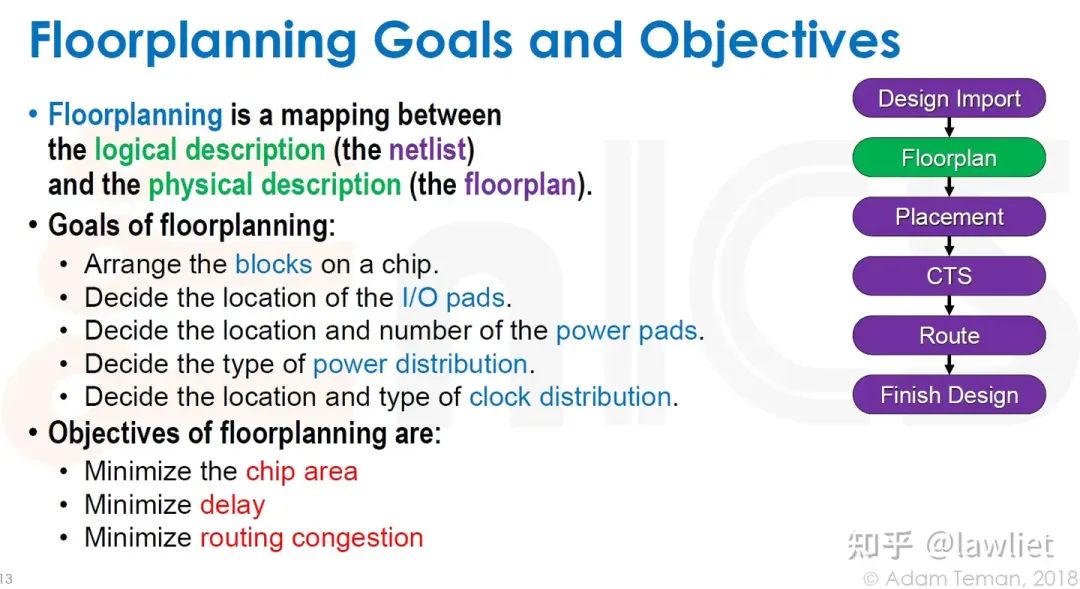

我们首先看一下Floorplanning。其将逻辑描述(netlist)映射到物理描述(floorplan)。在这个过程中,设计师需要将抽象的逻辑设计转换为具体的物理布局,确保设计的可行性、性能和可制造性。

我们直接看Floorplan做了些什么内容:

Arrange the blocks on a chip:将芯片上的各种功能模块(如处理器核心、内存、模拟电路等)合理地放置在芯片上,以优化性能和减少互连的复杂性。

Decide the location of the I/O pads:确定芯片与外部通信的输入/输出端口(I/O pads)的位置,以便于与外部设备的连接,并考虑到信号完整性、电磁干扰(EMI)和热管理等因素。

Decide the location and number of the power pads:确定电源和地端口的位置和数量,以确保电源网络的性能和效率,同时考虑到电源噪声和芯片的功耗。

Decide the type of power distribution:选择合适的电源分配网络类型,如全局电源网格、局部电源网格或电源岛(power islands),以支持不同电源域的需求和低功耗设计。

Decide the location and type of clock distribution:确定时钟信号分布网络的位置和类型,包括时钟树的布局和时钟缓冲器的放置,以减少时钟偏斜和时钟抖动,保证时钟信号的同步性和稳定性。

我们最终要达到一个什么要的目标呢?实际上和综合比较类似,让芯片面积尽可能小,延迟尽可能低,尽可能减少路由拥塞。

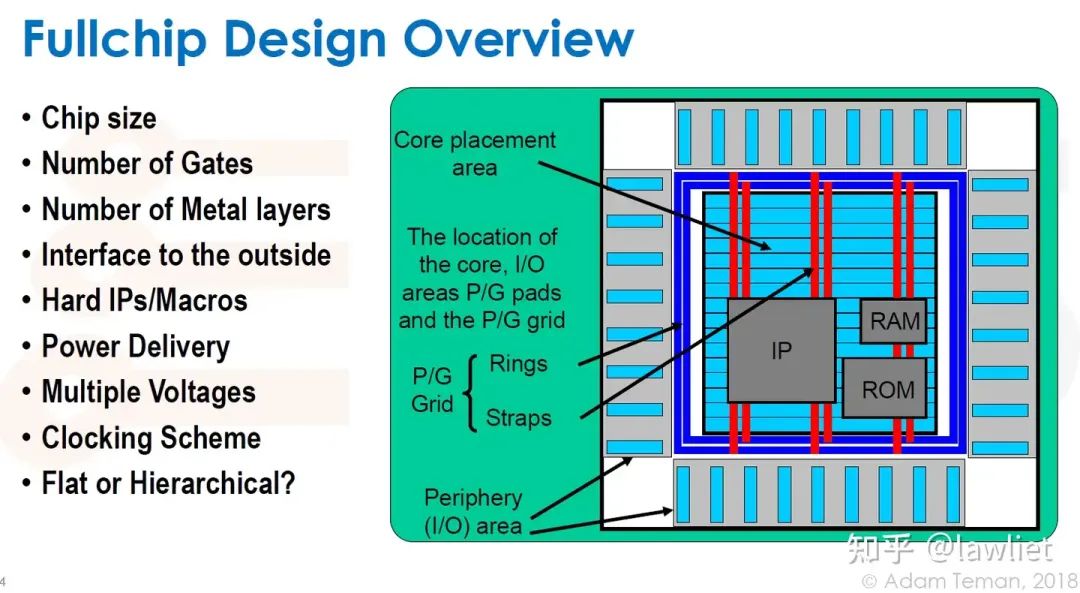

我们来看一个实际的例子:通过这个图我们可以看到芯片的大小,金属层的数量,接口信息,各种各样的IP在哪个位置等等。Floorplan的周围是芯片PAD。PAD实际上指的是芯片引脚的一块金属,通过它可以将芯片焊接在电路板上。

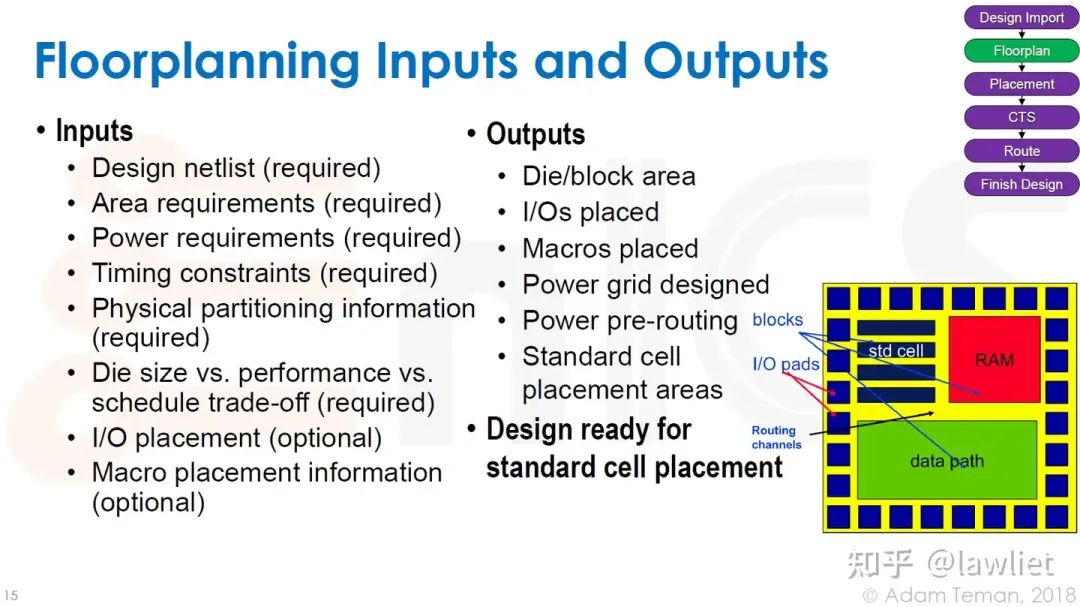

我们接着看Floorplanning的输入和输出。这一部分我就不一一解释了,相信大家能够看懂。我重点讲一下什么是Design ready for standard cell placement。

在完成Floorplan以后,芯片的整体布局已经确定,包括宏单元(如处理器核心、内存块等)的位置、I/O端口的位置、电源和时钟分布网络等。此时我们的标准Cell怎么放还没确定下来,所以Floorplan的下一步将会是Place。

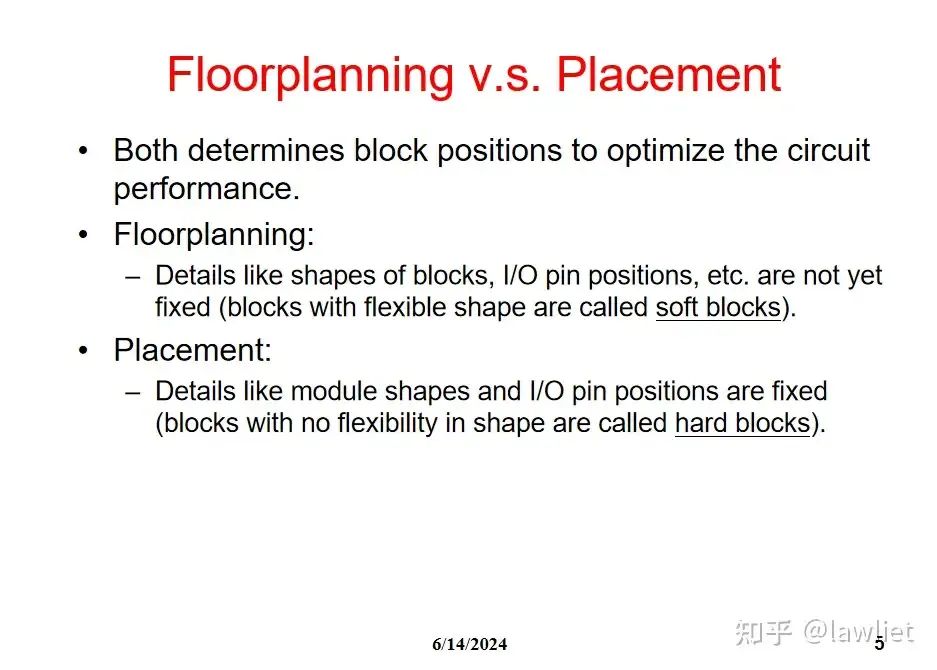

其实Floorplan已经完成了一定的Place工作,通俗来讲,Floorplanning 关注的是芯片的宏观布局,而 Placement 关注的是逻辑单元的微观布局。Floorplanning 为 Placement 提供了一个基本的设计框架,而 Placement 则在这个框架内进行详细的设计优化

我们巩固一下概念,通过下面这个图,结合上面的讲解,相信大家可以理解Floorplanning和Placement的区别。可以说二者确实有很多共同之处,Placement是在Floorplanning的基础之下进行的。

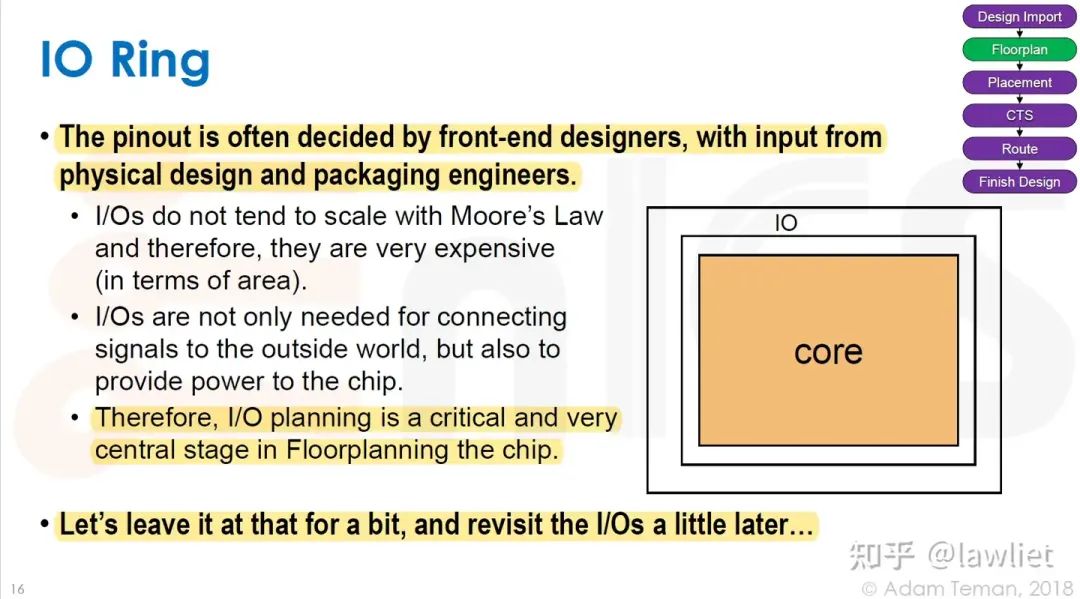

我们再来看一下什么是IO RING。I/O RING(I/O 环)是指芯片封装边缘上的一个环形区域,其中包含了芯片与外部世界通信的输入/输出(I/O)引脚。这些引脚可以是数据信号、电源信号、接地信号或其他类型的信号。

芯片的引脚分配通常由前端设计师决定,他们会根据芯片的逻辑功能和系统要求来规划引脚。同时,物理设计工程师和封装工程师也会参与进来,因为需要考虑到引脚的物理实现、封装的限制、信号完整性、电源和地分配、热管理等因素。

IO并不像摩尔定律一样,呈现指数级别增长,IO的成本是很高的,非常占据面积。在floorplanning阶段,对I/O引脚的规划是一个非常关键和核心的步骤,需要考虑到信号连接、电源供应以及整体系统设计的兼容性。

有关IO RING我们先简单看到这里,我们先看别的内容。

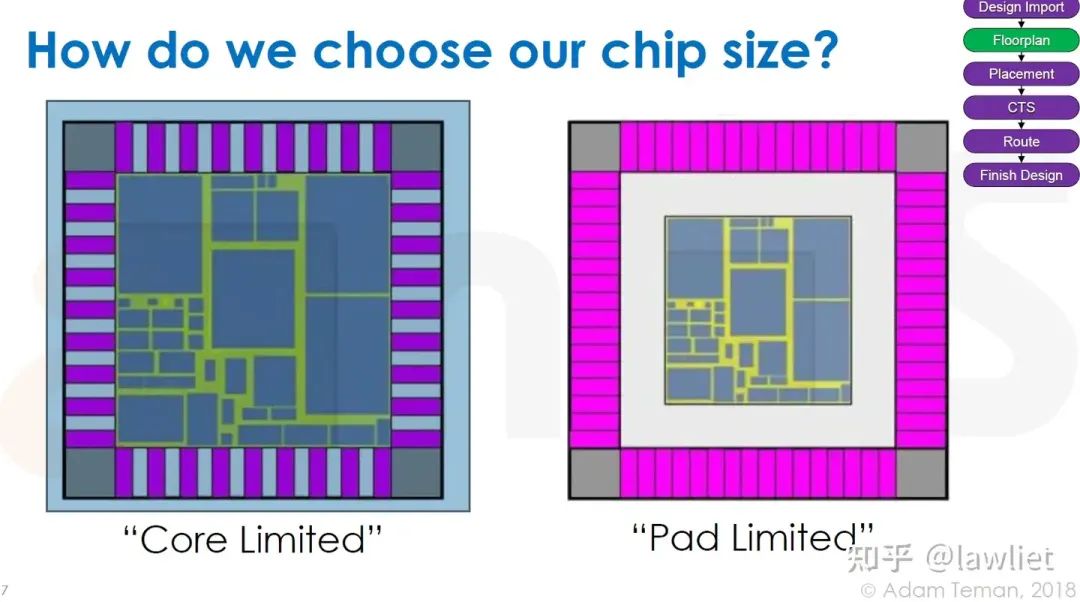

我们应该如何选择芯片的大小呢?下面这张图告诉我们,我们的芯片不可避免的会出现“Core limited"和”Pad Limited"的情况。(左边那个中心区域不够用,右边PAD不够用)

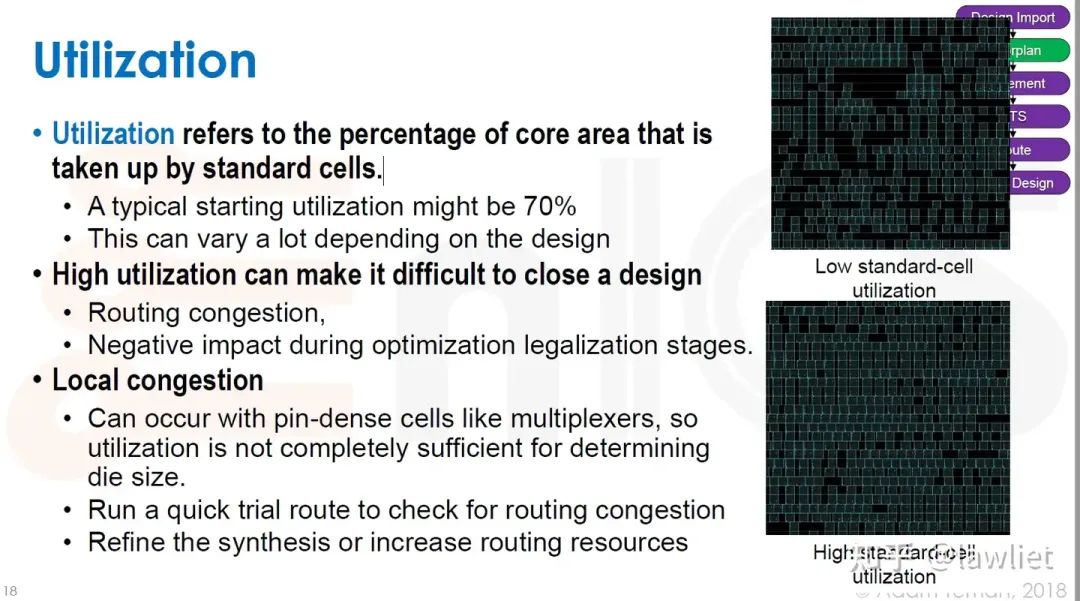

所以为了量化这一点,我们要引入一个指标,利用率Utilization。通俗来讲就是尽可能把能用的面积都利用上,避免浪费。当然利用率特别高的时候,会存在一些路由阻塞的问题。尤其是对于pin-dense的Cell,比如一个4选1的mux,它有6个pin,由于引脚数量较多,可能会在布局时占据较大的空间,从而导致其他逻辑单元的利用效率并不完全能反映芯片的实际面积需求。

所以在考虑芯片面积时,仅仅通过逻辑单元的利用率来确定是不够的。设计者需要考虑到多路复用器等具有密集引脚的单元可能会占据更多的空间,从而影响芯片的整体布局和面积。在设计时需要综合考虑这些因素,以确保芯片的布局既高效又满足性能要求。

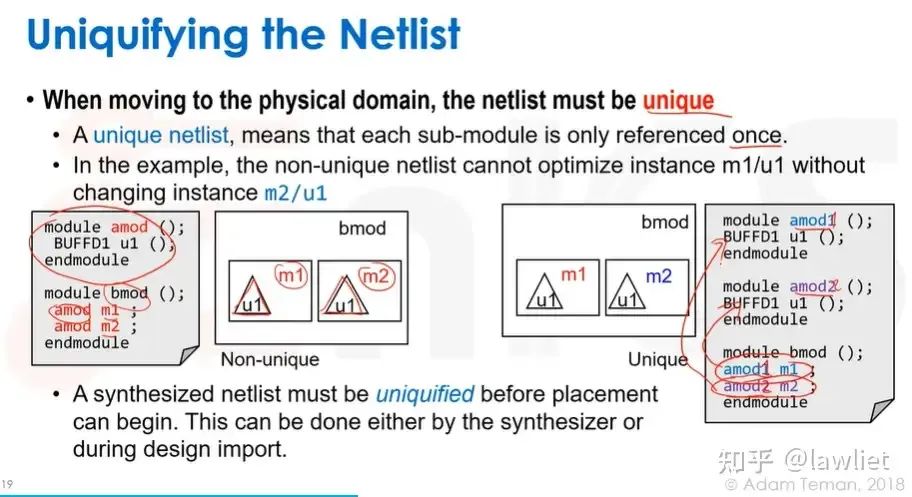

此外在物理设计中,还应该保证网表是唯一的。网表是唯一的意味着每个子模块在网表中只能够被引用一次,我们看下面这个例子。左边那个图,m1和m2因为都是amod,其下面的例化都是u1。此时认为amod子模块被引用了两次,也就是non-unique。因此在物理设计阶段,会将两个同时优化,而不可以优化其中一个固定另外一个。比如我们让m1/u1变大一点,此时m2/u1也会变大。因为m1和m2调用的是一个sub-module,也就是amod。

为了解决这个问题,将其中一个模块叫做amod1,另外一个模块叫做amod2,这样sub-module的对应就是唯一的了。这个过程叫做uniquifying the Netlist,实际上综合工具会为我们做这一点,因此大家只要了解即可。

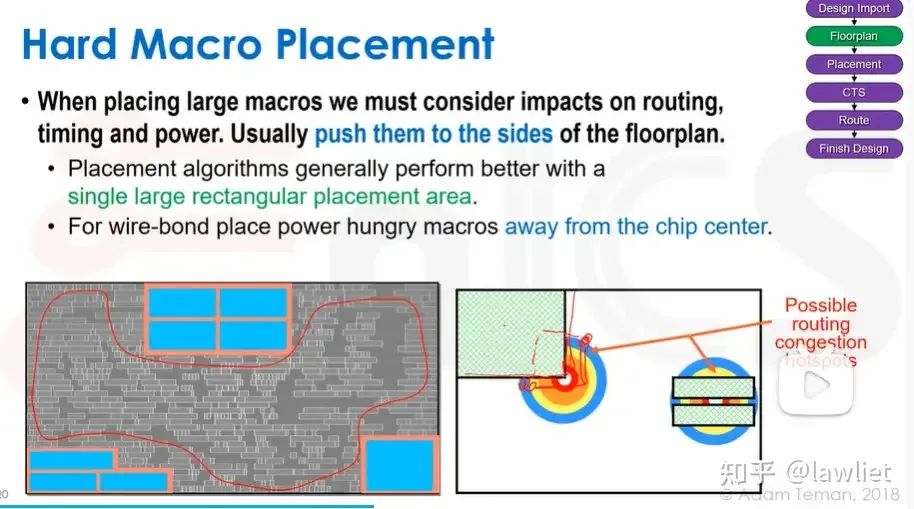

我们看一下如何摆Hard Macros。我们一般将其放在一侧,这样剩下的形状有利于后续的Placement进行,就比如下图的左侧红色线条包裹区域,这么一大片区域有助于后续的Placement。就好比盖房子,最好是留下来一整块的地方,而不是这里一点,那里一点。

摆好以后认为它们已经固定好了,后续不要再去改动这一部分Hard Macros。

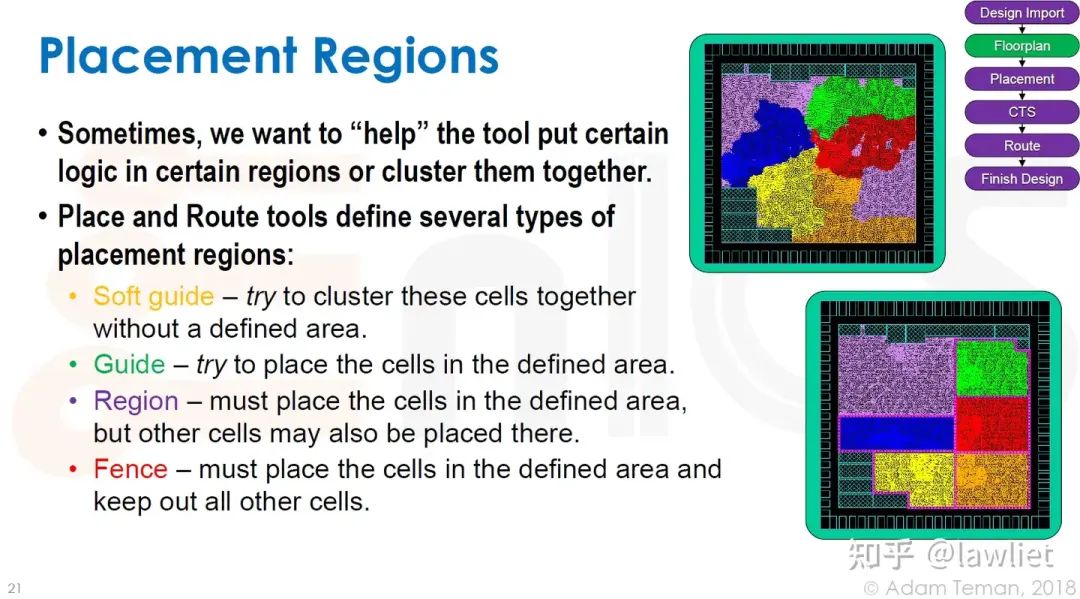

Placement Regions 指的是在芯片设计中为逻辑单元指定特定的放置区域或集群区域。有个时候我们希望可以根据具体的设计要求和目标来指定 Placement Regions,以帮助布局和布线工具更好地实现设计目标。P&R工具一般提供了下面的指导方式,具体看图即可。

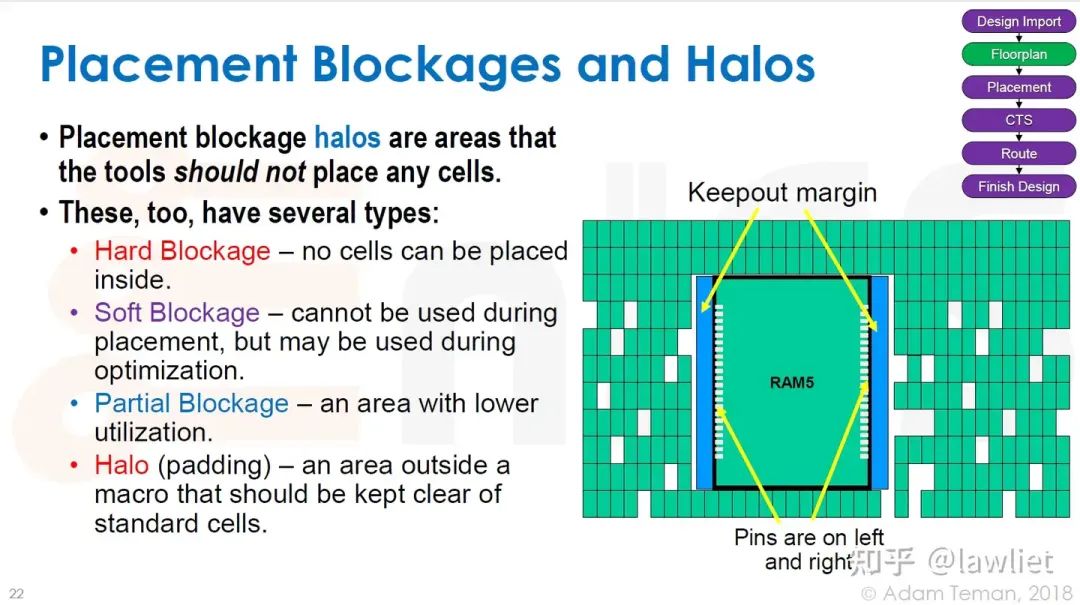

还有一些地方我们不能放逻辑单元。Placement Blockages是芯片设计中需要特别注意的区域,这些区域不允许逻辑单元放置。例如,某些区域可能被用于电源和地网络的布局,或者用于时钟分布网络,或者因为制造工艺的限制而不适合放置逻辑单元。在布局过程中,这些区域会被视为不可放置的障碍,布局和布线工具会避开这些区域。

而Halos是一种布局策略,它涉及在芯片的边缘或特定区域内设置一个边界,以限制逻辑单元的放置。设置 Halos 的目的是为了保护芯片的边缘区域,防止逻辑单元过于靠近边缘,从而影响芯片的封装和性能。

更加具体的分类我们直接看下图即可。

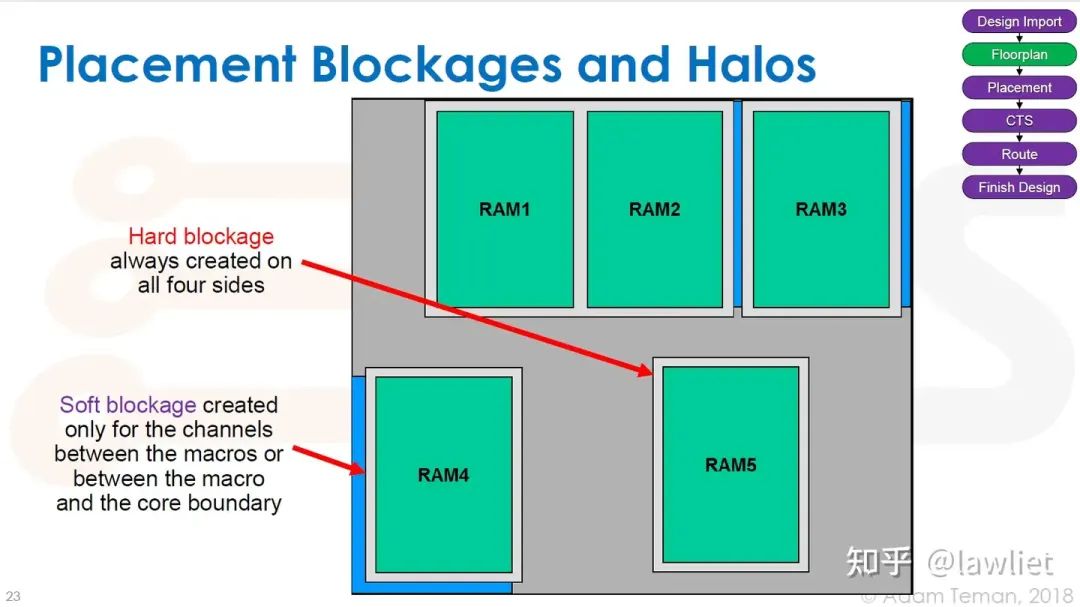

我们再看一个示意图加深一下概念:

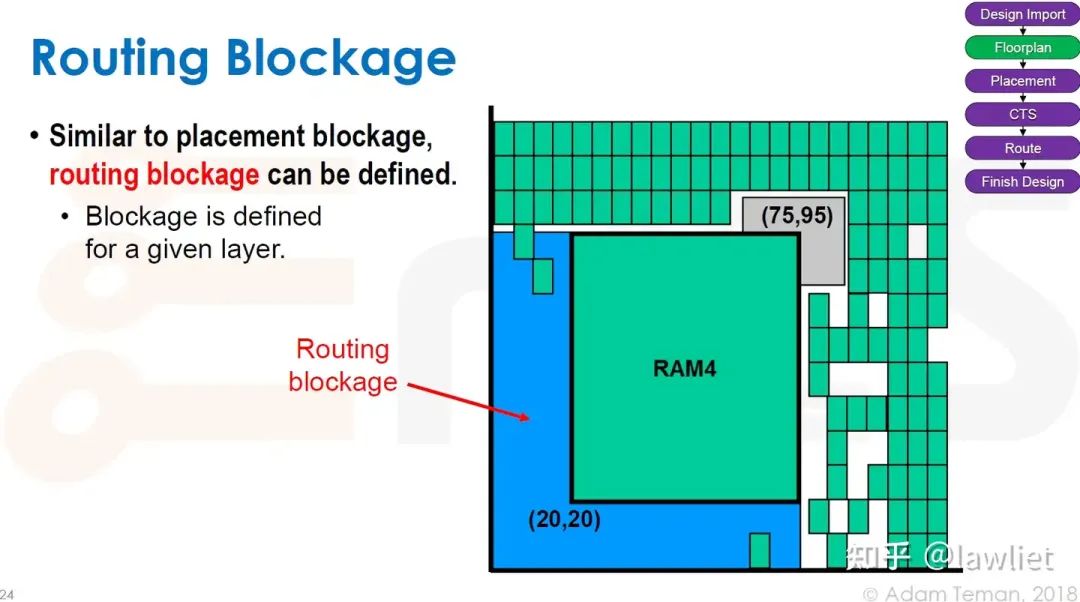

类似的,还可以将这个概念引入到Routing。

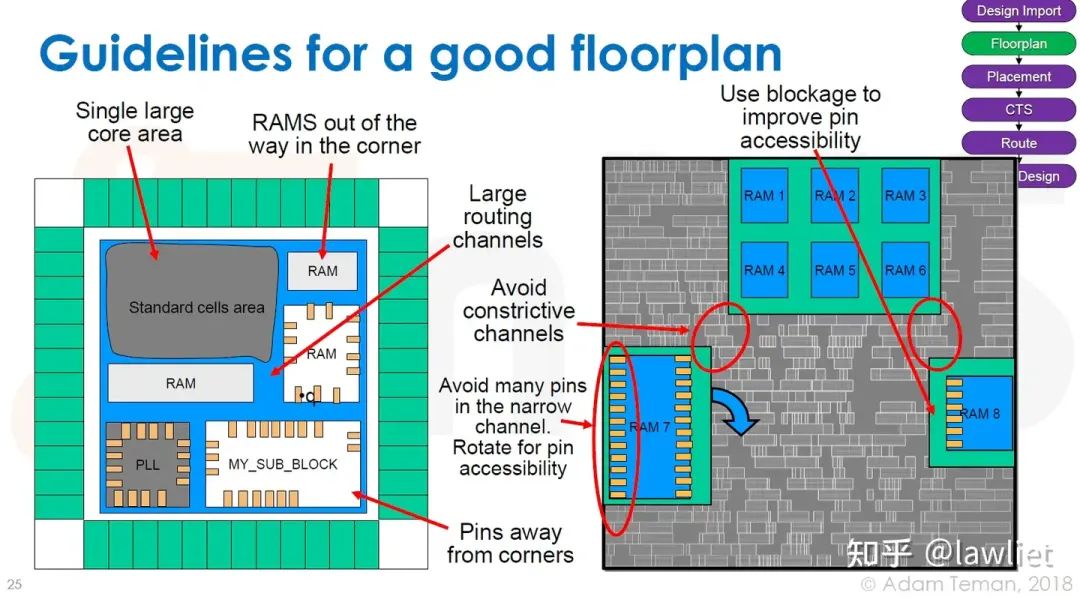

我们来总结一下,Floorplan中一些优秀的设计思想:

Single large core area:将逻辑核心区域(如处理器核心、内存模块等)设计为一个单一的大型区域,这样可以减少互连的复杂性,提高性能;

RAMS out of the way in the corner:将存储器单元放置在芯片的角落或边缘,这样可以减少它们对核心逻辑区域的干扰,同时保持核心区域的连通性;

Large routing channels:在芯片布局中保留宽大的布线通道,这样可以减少布线拥塞,提高信号的传输效率;

Avoid constrictive channels:避免在布局中创建狭窄的布线通道,这样可以减少信号的延迟和干扰,提高信号质量;

Avoid many pins in the narrow channel:在布局中避免在狭窄的通道中放置太多的引脚,这样可以减少布线冲突,提高信号的传输效率;

Rotate for pin accessibility:根据引脚的访问需求,考虑旋转芯片的布局,以便于引脚的布局和布线;

Pins away from corners:将引脚远离在芯片的边缘或角落,这样可以减少引脚与芯片边缘的干扰,提高引脚的布局和布线效率;

Use blockage to improve pin accessibility:在布局中使用blockage来改善引脚的访问性,例如,将引脚放置在障碍物附近,以便于引脚的布局和布线;

4、Hierarchical Design

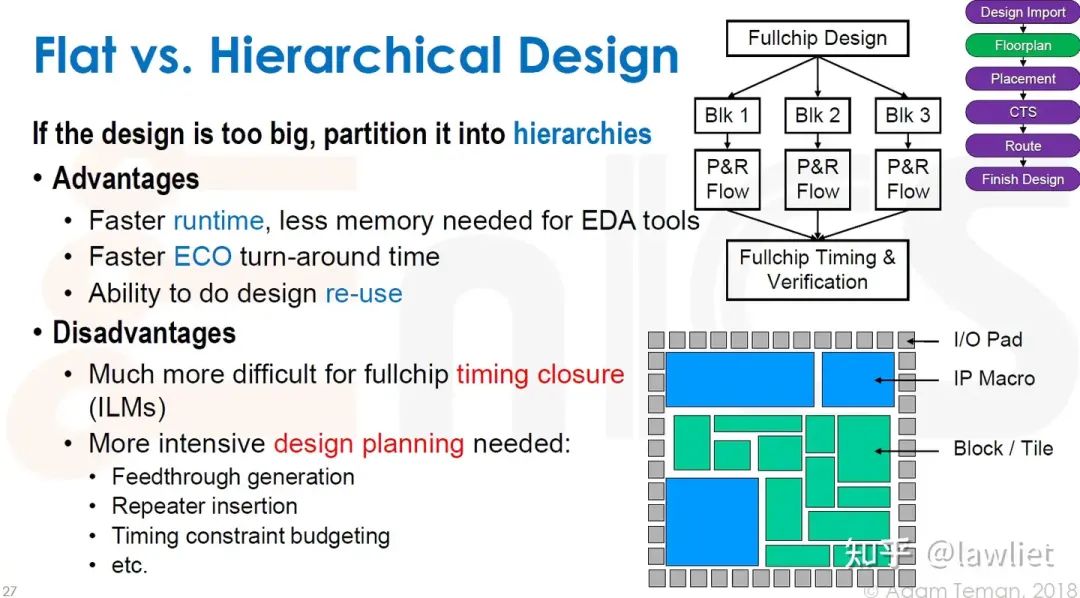

如果设计太大的话,我们可以将其分成多个Block。其具体如下图右边所述。我们可以看看Flat和Hierarchical的优点和缺点:

Flat Design:

优点:

简单直观,易于理解和维护。整个设计是一个单一的实体,不需要额外的层次结构;

· 缺点:

当设计变得非常大时,可能需要更长的运行时间,因为需要处理大量的数据,可能需要更多的内存来运行EDA工具;

设计更改(ECO,Engineering Change Order)的周转时间可能较长,因为需要重新分析整个设计

Hierarchical Design:

优点:

设计可以被分割成更小的、易于管理的部分,这些部分可以独立地分析和优化;

运行时间更快,因为只需要处理当前工作区域的数据;

内存需求较低,因为不需要存储整个设计的数据;

设计重用更加容易,因为可以单独替换或修改某个子模块。

· 缺点:

层次结构可能使得全芯片时序收敛变得更加困难,因为需要确保所有子模块的时序都能满足要求;

设计规划需要更加密集,因为需要处理多个层次的反馈和重用;

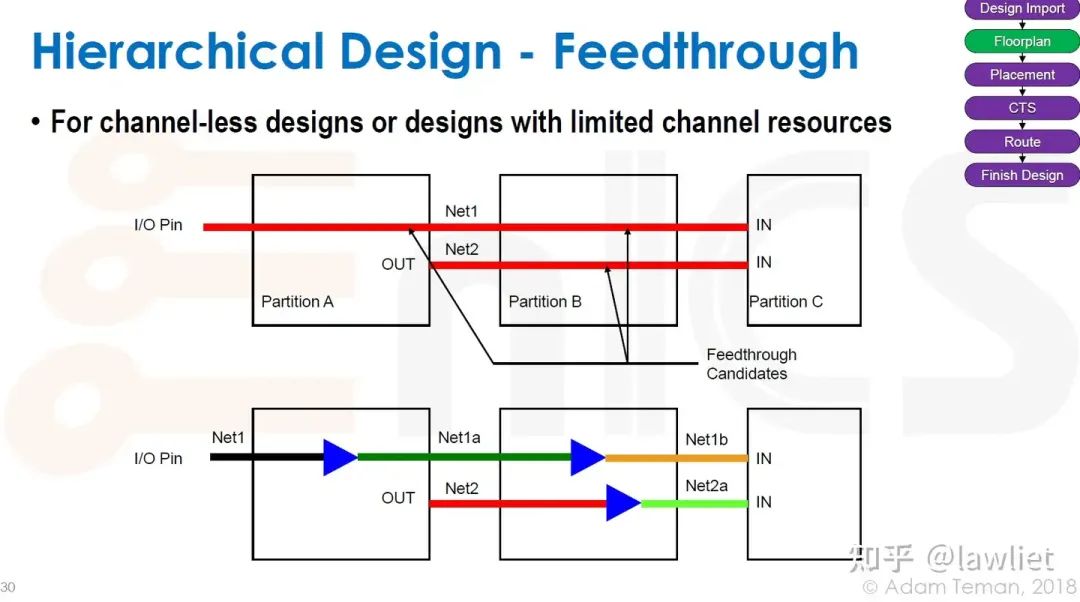

需要生成feedthrough、repeater insertiom、timing constraint budgeting等,这些都是确保时序收敛的关键步骤;

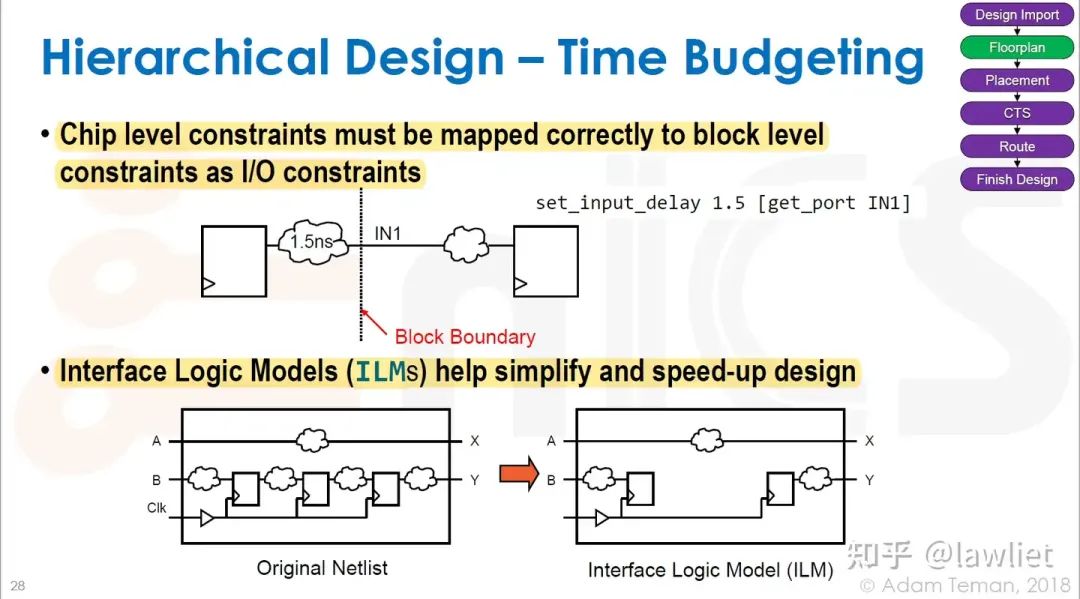

我们来看一下层次化设计中的时间预算问题。如果采用整体设计的话,所有的设计都是一个整体,只需要确定一组input delay和output delay即可。但如果采用层次化设计的话,要注意这些问题。

芯片级约束映射到块级约束:在层次化设计中,芯片级的时序约束需要正确地映射到各个块级约束。例如,如果芯片级时序要求某个关键路径的时延不超过某个值,那么这个约束需要被分解并分配给相关的块级时序约束。同样,I/O约束也需要被正确地映射到块级约束,以确保芯片的I/O端口能够满足设计要求。

接口逻辑模型(Interface Logic Models, ILMs):ILMs 是一种简化设计时间和资源的方法,它允许设计者使用简化的模型来表示复杂的接口逻辑。它可以快速地评估接口逻辑对时序的影响,而不需要详细地分析整个设计。使用 ILMs 可以显著加快设计时间。我们直接看下面这个图,原本的网表是比较复杂的,这里将中间的逻辑都简化了,仅仅剩下入口和出口,还有直通逻辑。

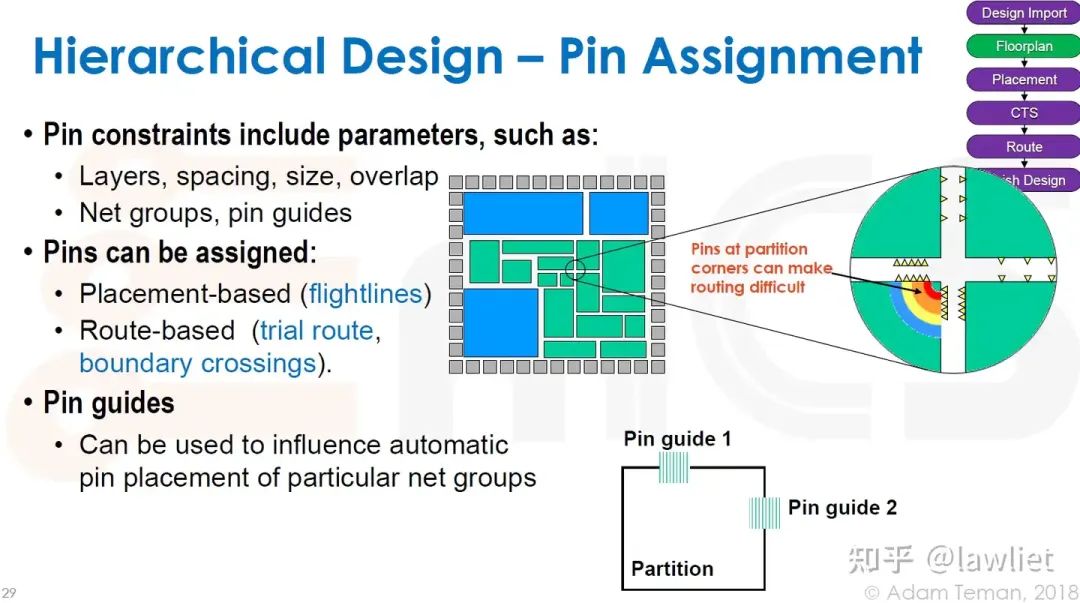

我们再来看一看Pin的规划。对于Pin,我们要使用相应的约束,这些约束包括以下参数:层(Layers):指定引脚所在的层,如信号层、电源层、接地层等。间距(Spacing):指定引脚之间的最小间距,以确保电气隔离和防止短路。大小(Size):指定引脚的物理尺寸,如宽度、长度等。重叠(Overlap):指定引脚与其他元素(如布线、电源和地线等)的重叠要求,以避免电气冲突。

Pin constraints 还包括以下内容:网络组(Net groups):将具有相似特性或连接需求的引脚分组,以便于布局和布线工具进行处理。引脚指南(Pin guides):指定引脚的放置方向和位置,以指导自动布局工具的放置。

Pin可使用以下两种优先级的约束:基于放置的约束(Placement based):使用飞线(flightlines)来指导引脚的放置,确保它们在芯片上的布局符合特定的规则。基于布线的约束(Route based):指定尝试布线(trial route)和边界交叉(boundary crossings),以指导引脚的布线路径。

Feedthrough路径定义从顶层I/O引脚进入和穿过Block,以减少长路由和拥塞。中继器需要被添加到这些路径中,以保持信号强度并避免max slew和扇出违规。

5、Power Planning

我们再来看一个重要的话题,Power Planning,中文名一般叫做电源规划。其基本可以认为是Floorplanning的一部分。(大部分电源规划可能已在Floorplanning阶段完成,但在Placement阶段也可能需要进行一些细致的调整。例如,为了满足特定模块或逻辑块的电流需求,可能需要添加额外的电源或地连接。)

初步Power Planning主要包括:

电源网格设计(Power Grids):创建电源和地网格来提供电流和参考电压。

电源环(Power Rings):在芯片外围设计电源环,用于电源和地的分发。

电源铺垫(Power Pads):确定用于外部电源连接的电源和地铺垫的位置。

Power planning 的目标是在芯片上创建一个高效的电源和地网络,以确保电源和地能够有效地分布到芯片的各个部分,同时考虑到电源噪声和信号完整性。

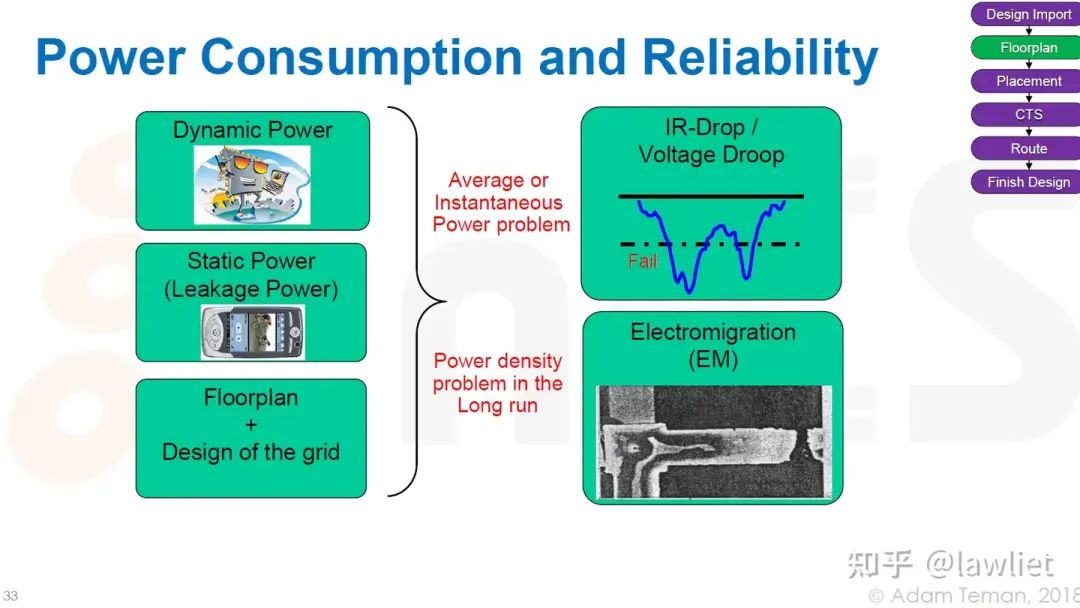

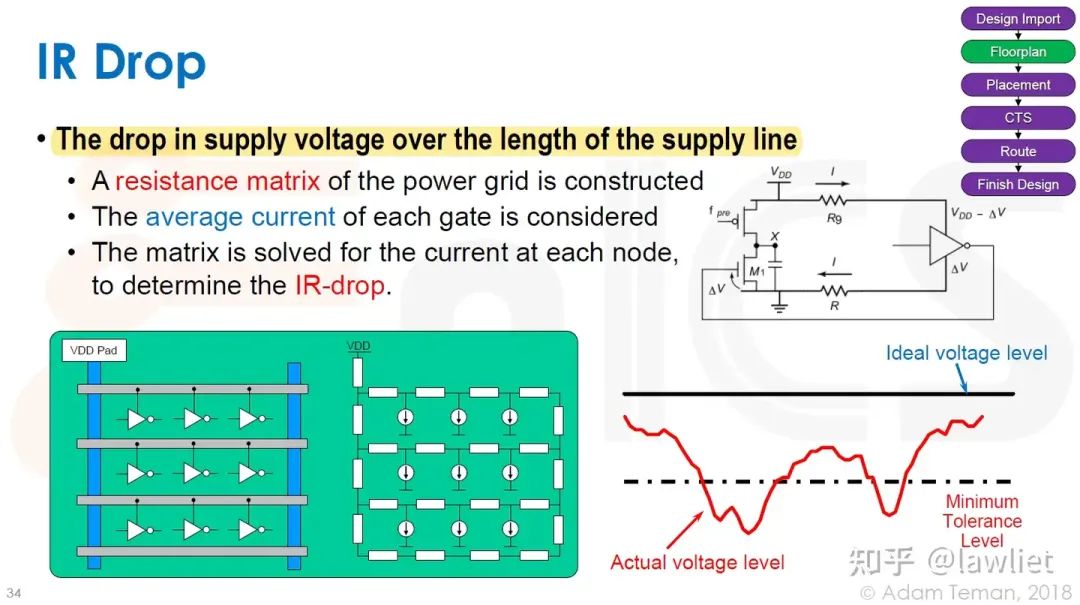

我们来具体看一下什么是IR-Drop。IR Drop 是指在电源线(power line)长度上,由于电源线电阻导致的电源电压(supply voltage)下降。IR Drop 是电源规划和设计中需要考虑的一个重要因素,因为它会影响到芯片的性能和可靠性。

我们应该怎么分析这个问题呢?通常采用矩阵的方式进行求解。

电阻矩阵的构建:在电源网络中,电源线和电源层之间存在电阻,这些电阻会导致电压下降。设计者需要构建一个电阻矩阵,其中包含电源网络中每个节点的电阻值。

平均电流的考虑:每个逻辑门的平均电流是计算 IR Drop 的重要参数。设计者需要考虑每个逻辑门的平均电流,以计算在电源线上的电压下降。

矩阵求解:一旦构建了电阻矩阵并考虑了平均电流,设计者可以使用矩阵求解的方法来计算每个节点上的电流。通过矩阵求解,设计者可以确定电源线上的电压下降,即 IR Drop。

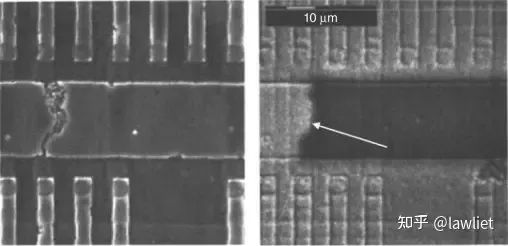

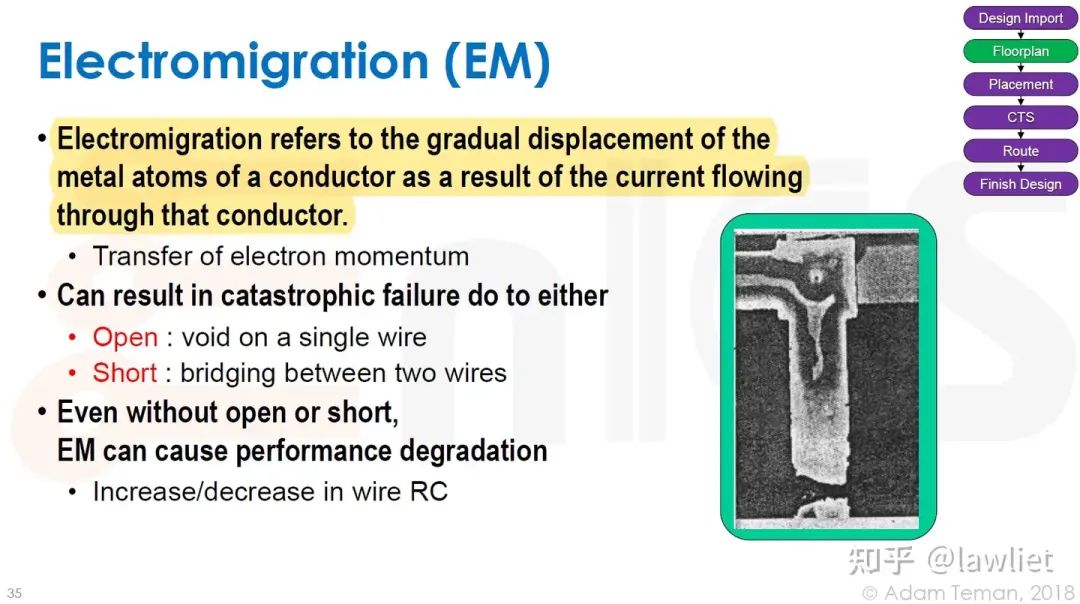

我们再来看一个概念,电迁移。在集成电路后段会部署大量金属连线结构,本来这些金属连线的作用就是让电子迁移,实现导电。但反过来,电子的流动会造成金属材料迁移,最终导线被“掐断”:

这种现象就叫做电迁移,其可通过形成空隙或小丘来改变导体的物理结构,从而导致短路、开路、性能劣化或设备故障。随着流经互连器件的电流密度增大,电迁移率也随之增加,这使得电迁移成为一个失控过程。事实上,电迁移是电路故障的主要原因。

为了避免电子组件中金属迁移所带来的失败和危险,芯片设计人员可以采用以下几种方法:

增加互连宽度,以降低电流密度。

使用具有高电迁移耐力的材料,如金和铜。

使用冗余通孔来分流电流强度。

减少互连器件之间的间距。

设计低电压水平的电路。

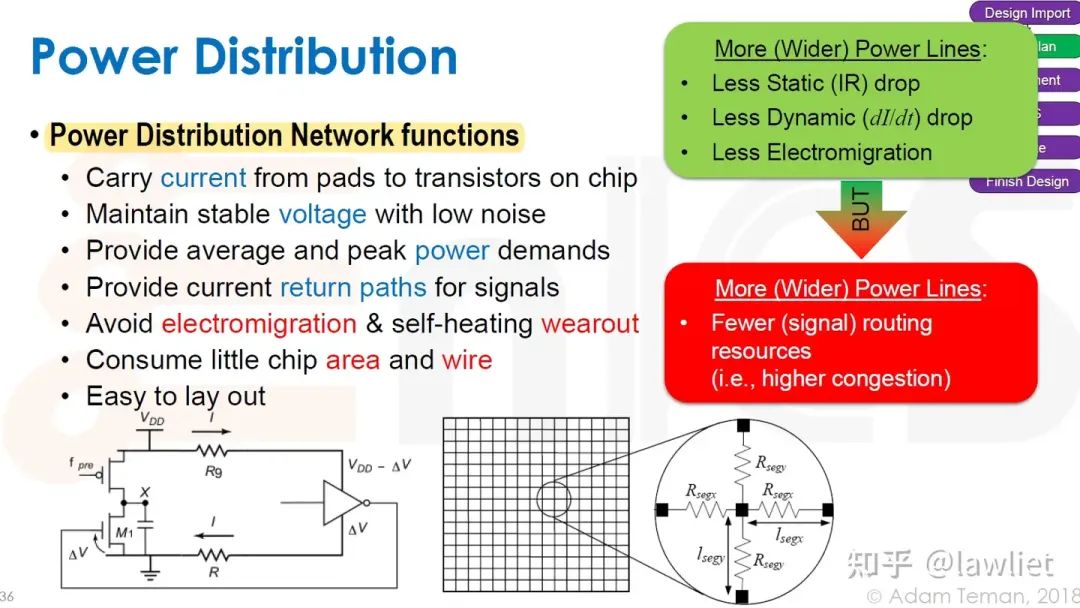

Power Distribution Network(PDN)是芯片设计中的一个关键组成部分,其功能包括:

从焊盘(pads)向芯片上的晶体管传输电流:PDN负责将电流从芯片的输入/输出(I/O)端口传输到芯片内部的逻辑单元。

保持电压稳定并降低噪声:PDN设计需要确保芯片的电压稳定,以支持逻辑单元的正常工作。同时,它还需要降低电源噪声,以避免对芯片性能的影响。

提供平均和峰值功率需求:PDN需要能够满足芯片在正常操作和峰值负载下的功率需求。

为信号提供电流返回路径:PDN设计需要确保芯片上的信号可以有效地返回电源和地,以支持信号的正确传输和处理。

避免电迁移(electromigration)和自加热导致的磨损:PDN设计需要考虑电源线和地线的布局,以减少电迁移和自加热导致的材料损坏和寿命缩短。

占用芯片面积和线宽最小:PDN设计需要优化电源线和地线的布局,以最小化对芯片面积和线宽的占用。

易于布局:PDN设计需要考虑到布线的便利性,以便于后续的布局和布线工作。

我们还可以看到,更宽的Power Lines,可以降低IR DROP,可以减少电迁移。但同时会导致routing变得困难。

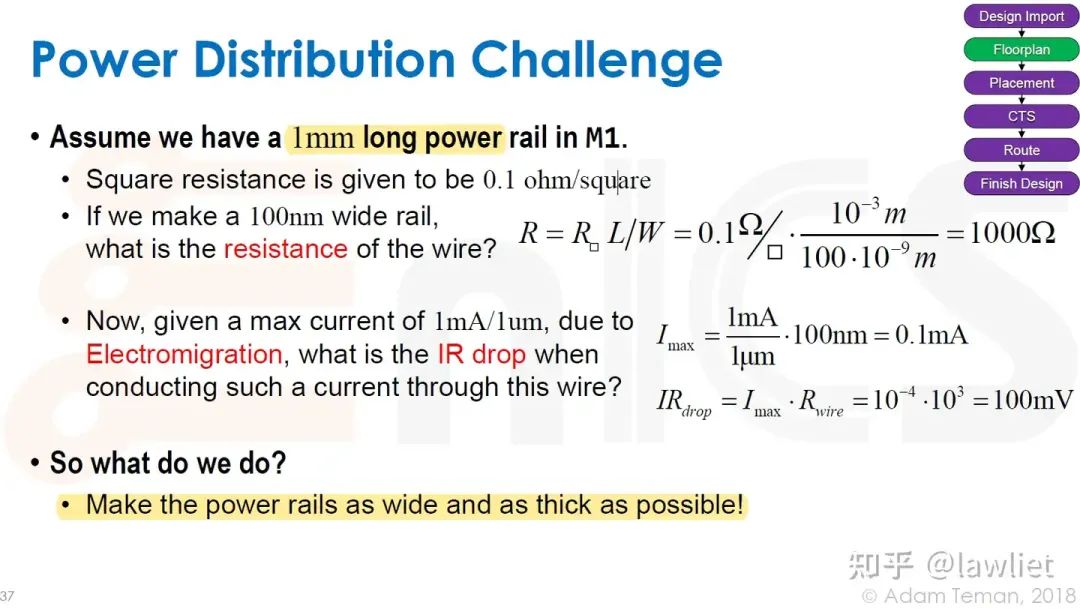

我们来看一个实际的例子。假设在金属层1有一个1毫米长的电源轨,我们根据给出的条件可以算出其电阻为1000欧姆。进而求出对应的IR DROP。由于电迁移会导致电源轨的电阻增加,从而引起IR Drop,因此需要采取措施来减少这种影响。

一种方法是增加电源轨的宽度,这样可以降低电流密度,从而减少电迁移的影响。另一种方法是增加电源轨的厚度,因为更厚的电源轨可以承受更高的电流密度。综合考虑,设计者通常会尽可能地使电源轨宽和厚,以减少电迁移和IR Drop的影响。

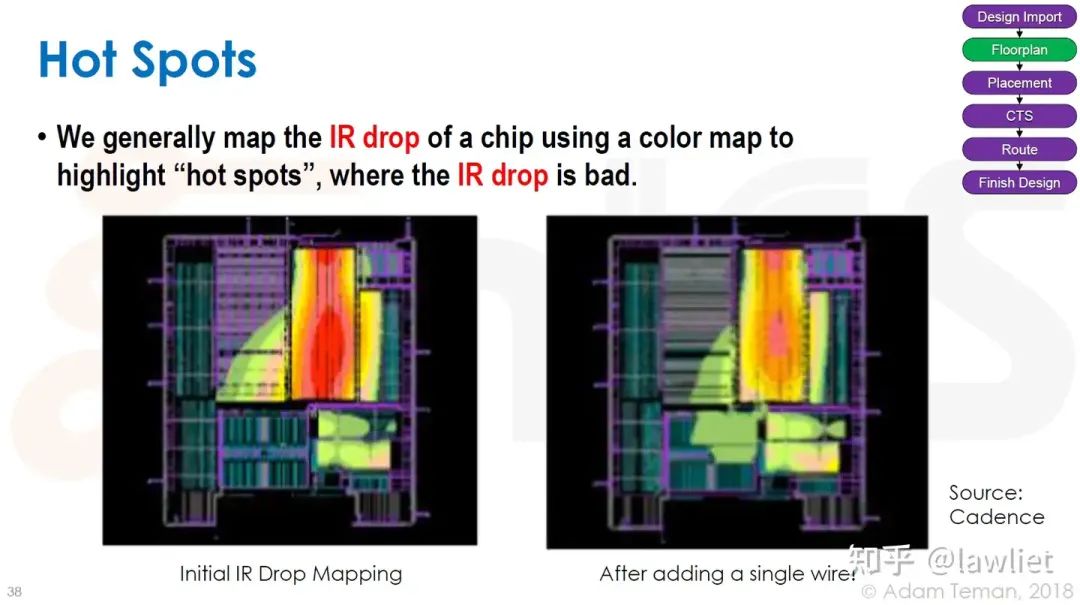

下图是一个实际的图片,在增加宽度以后,IR DROP效应变小了。

我们再来看一下电源和地网络的一些设计规则。

电源和地信号的连接:

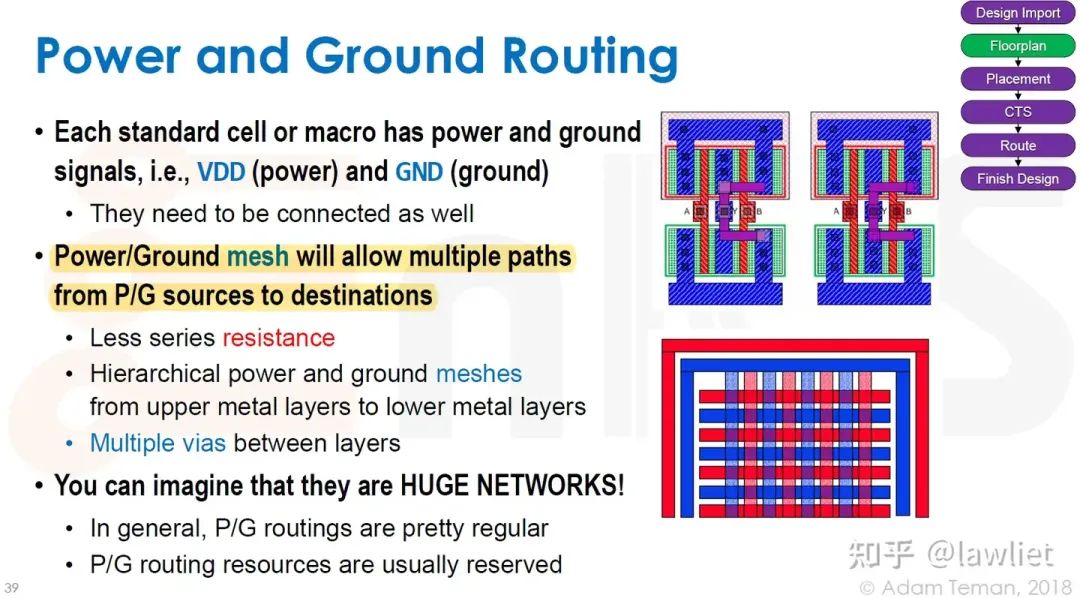

每个标准单元或宏单元都需要与电源和地信号连接,以确保它们能够从电源源(如电源分配网络)接收所需的电压。

电源/地网格(Power/Ground mesh):

电源/地网格允许电源和地信号通过多个路径从源到达目的地,这样可以减少串联电阻,提高电源和地网络的性能。

电源/地网格从高层金属层到低层金属层,形成一个层次化的网络,以提供有效的电源和地分布。

在不同层之间需要多个通孔(vias)来连接电源和地网络。

电源和地布线的规则性:

电源和地布线通常是比较规则的,因为它们需要在整个芯片上均匀分布,以提供稳定的电源和地参考。

电源和地布线资源的预留:

由于电源和地布线是芯片设计中的基础,因此通常会预留足够的布线资源来确保电源和地网络的性能。

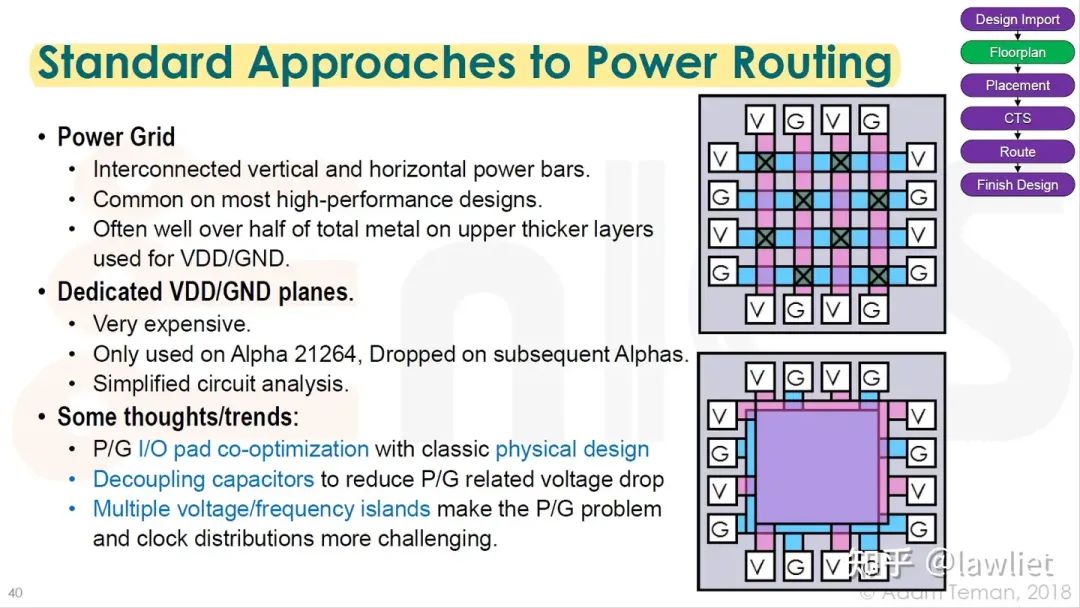

我们再来看一下Power Routing中的一些经典方法:

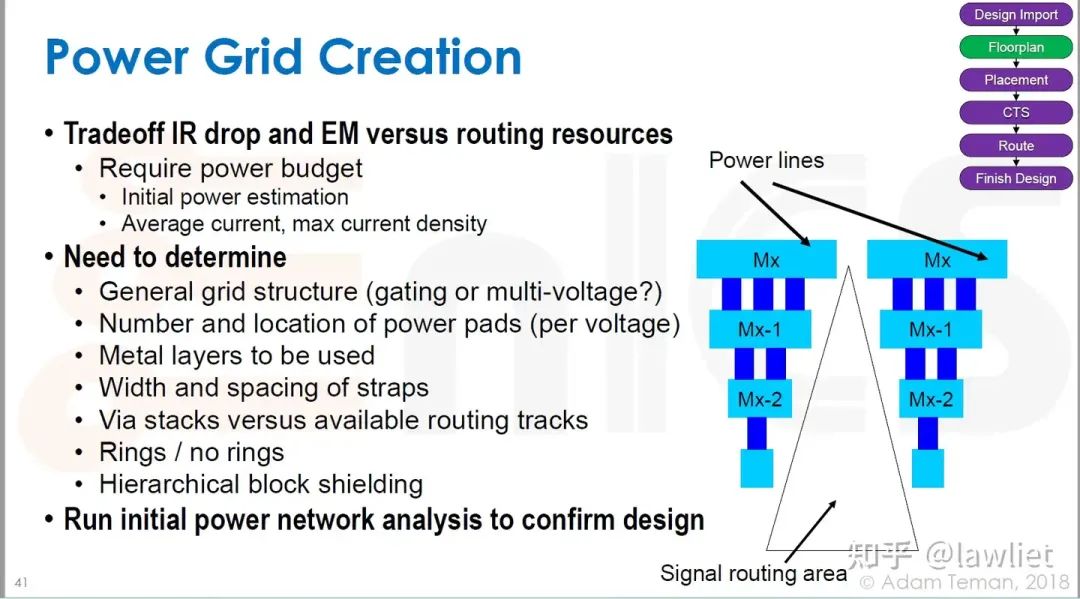

我们再来看一下电源网络中的一些权衡点:

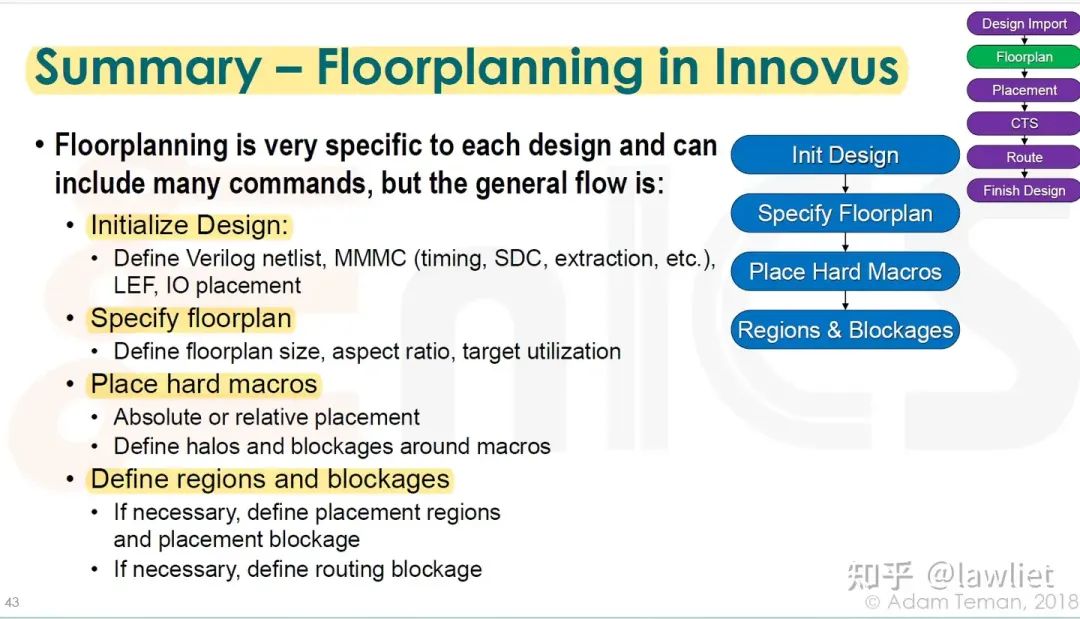

最后我们做一个总结,如何在Cadence的EDA工具Innovus中做FLoorplanning:

|