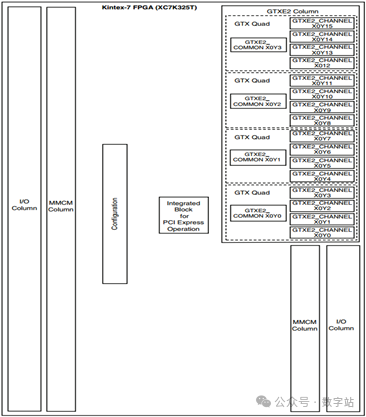

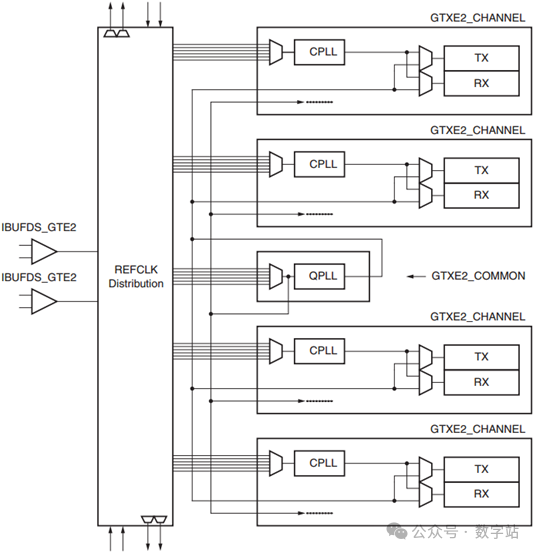

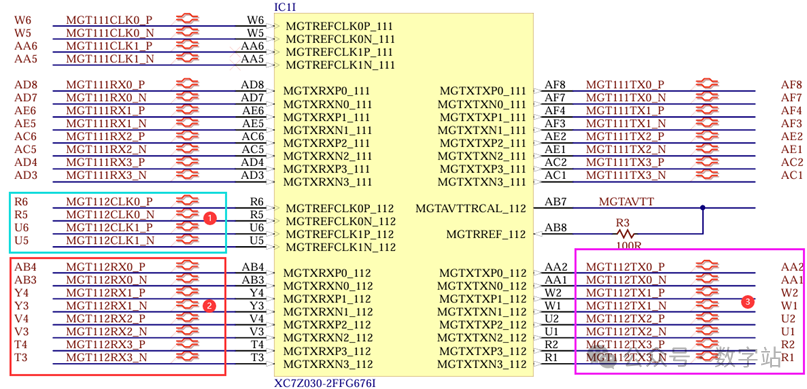

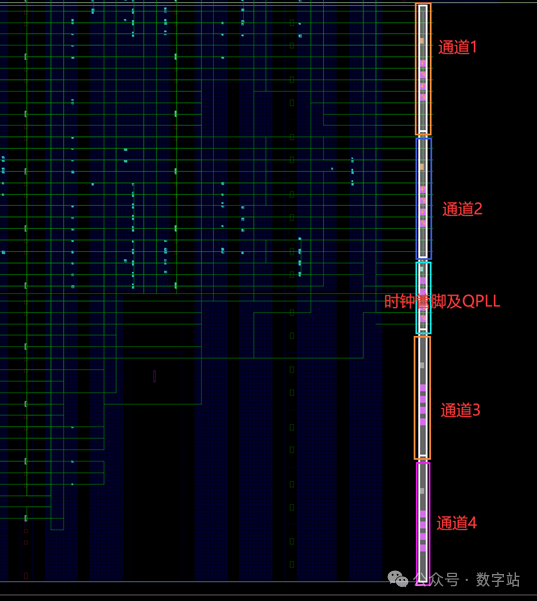

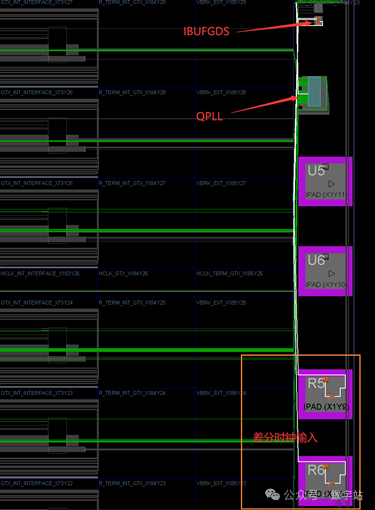

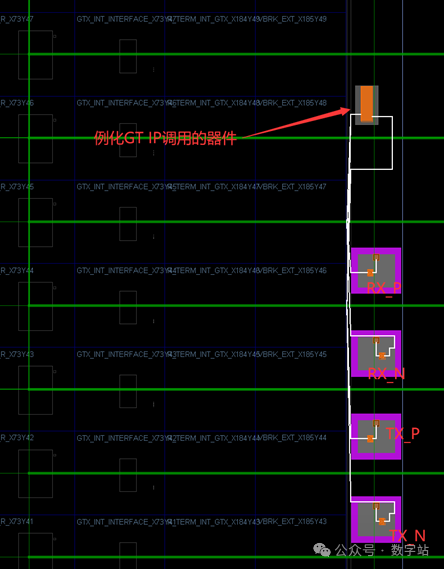

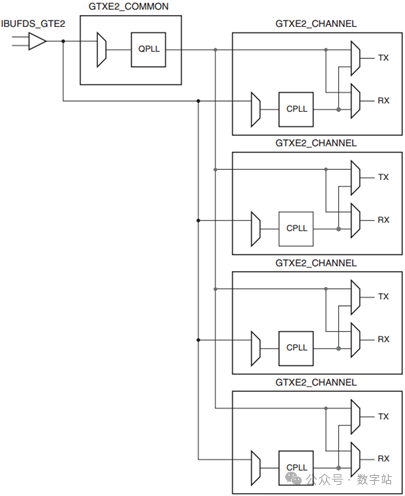

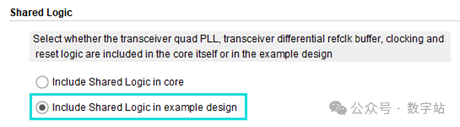

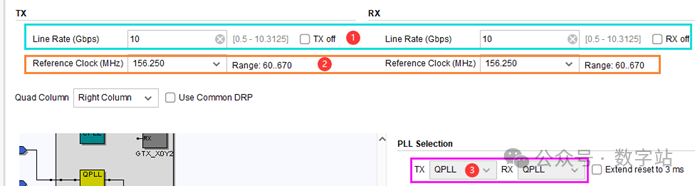

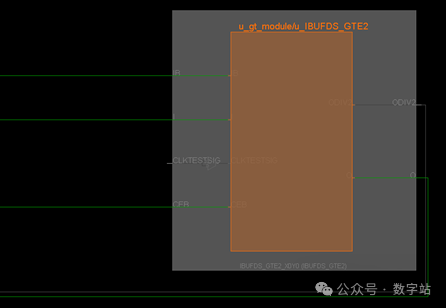

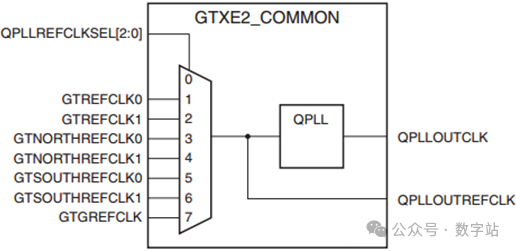

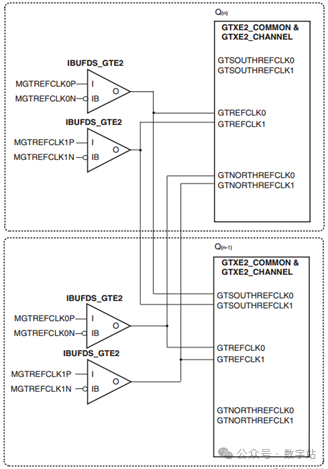

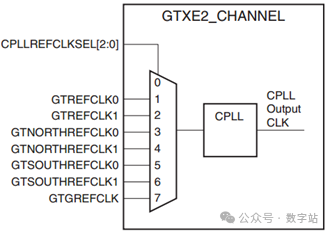

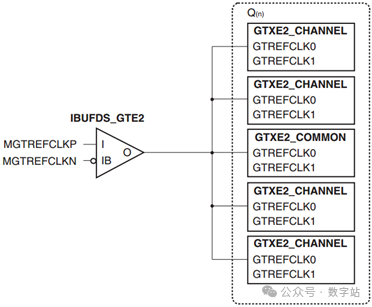

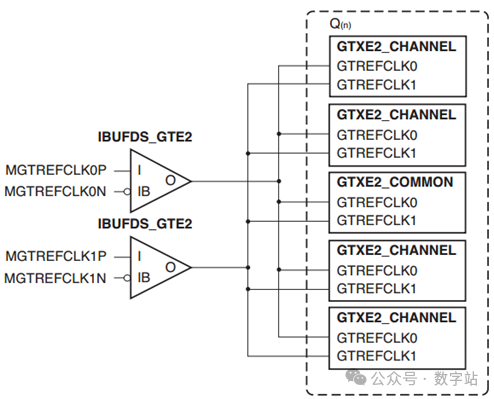

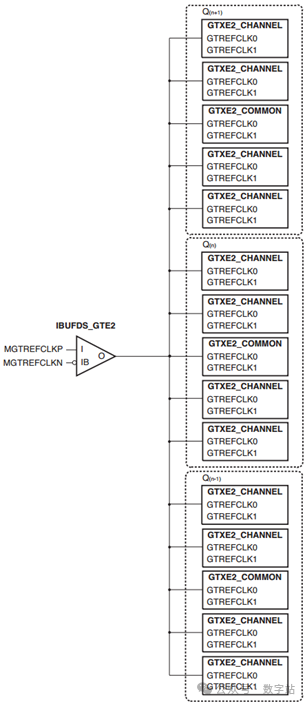

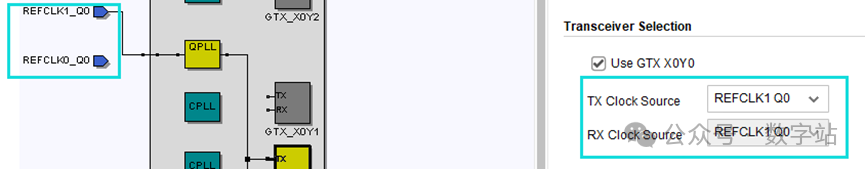

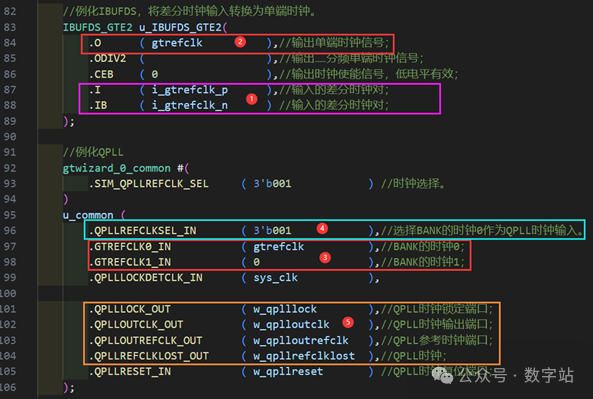

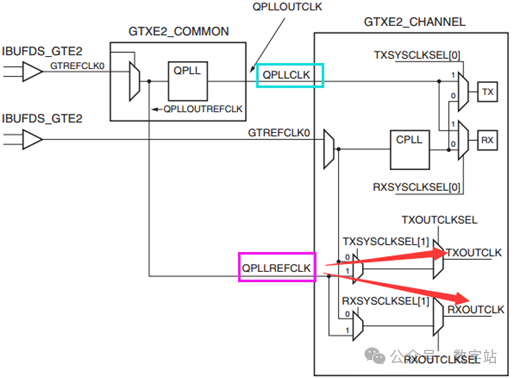

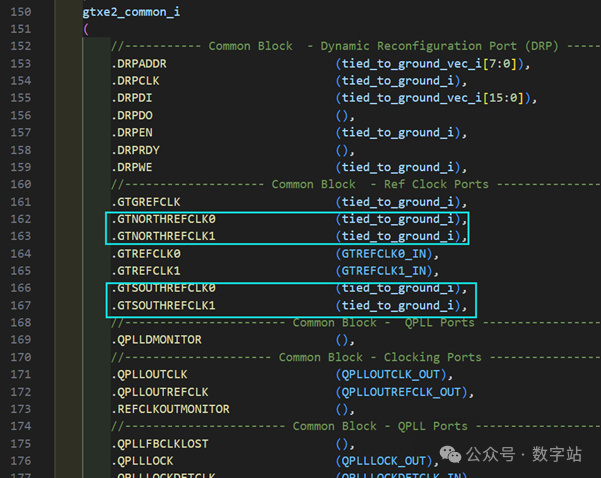

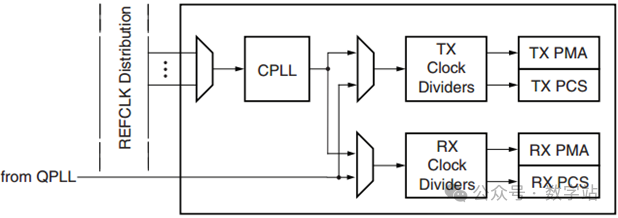

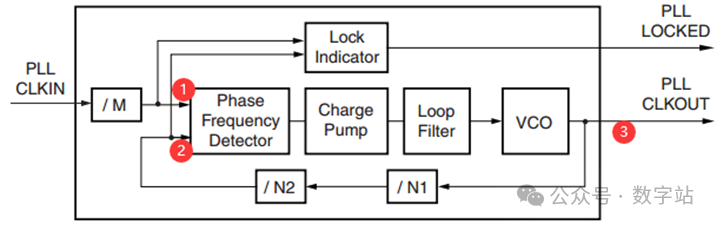

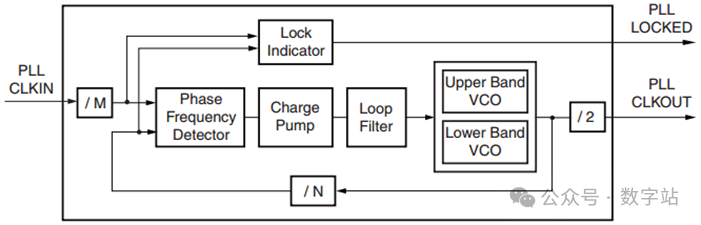

由于GTX 涉及的内容比较多,应该大致会用三节内容进行讲解,本文结合手册和芯片中的布局图对时钟进行讲解,后文分别对通道的发送和接收部分进行讲解。01 了解GTX整体结构 下图是xc7k325t的高速收发器分布图,该芯片包含四个GT bank,GT bank被称为Quad,每个Quad中包含四个gt通道,每个通道就是一个高速收发器。  图1 GT收发器分布图 因此每个bank包含4个高速收发器,如下图所示,每个高速收发器通道(GTXE2_CHANNEL)包含一个CPLL和独立的发送、接收通道。四个高速收发器通道共用一个QPLL,且每个通道左边都有两对差分时钟引脚。  图2 高速bank构成 注意上图中的GTXE2_COMMOM是将QPLL封装得到的,手册中讲解了QPLL和GTXE2_COMMOM的原语,两者都是调用QPLL。 为了便于理解,可以结合原理图进行查看,如下所示,原理图为了兼容zynq 7035芯片,下图多画了一个GT bank的引脚,zynq 7030是没有111 bank的,所以阅读的时候注意一下。 下图1是112 GT bank的两对差分时钟输入管脚,注意高速收发器只能使用GT bank两对差分管脚的输入时钟作为参考时钟,不能使用其余bank的时钟信号作为参考时钟,猜测是因为其余bank的时钟走线速率达不到吧。 2是4个高速收发器的接收差分引脚对,3是4个高速收发器的发送差分引脚对。  图3 GT bank原理图 之后在打开一个高速收发器的vivado工程,看一下各个通道及QPLL在芯片中具体的位置,便于理解真实情况。 如下图所示,每个bank会给用户预留四对差分输入和差分输出管脚,两对差分时钟输入管脚,总共20个管脚。时钟管脚位于中间部分,其上面和下面均包含两个高速收发器通道。  图4 FPGA中高速收发器通道分布 如下图所示,差分时钟信号进入FPGA之后,先通过IBUFDS_GTE2转换为单端时钟信号。由于本工程使用QPLL,所以单端时钟信号作为QPLL的输入时钟,QPLL的输出时钟作为GT收发器的时钟信号。 因为CPLL位于每个高速收发器通道内部,使用CPLL时,单端时钟可能直接输入GT收发器的通道中,目前还没使用CPLL,只是猜测,后续验证。  图5 时钟输入流向 在实际使用时,因为他的原语在软件中并没有直接开放给用户,一般会直接调用GT的IP,调用IP实际上就是使用下图的器件,该器件直接与接收和发送的差分引脚相连。  图6 GT IP对应的器件 02 GTX输入时钟 对GTX的整体结构做了初步讲解,需要知道每个bank包括四个高速收发器通道,每个通道内部都包含一个CPLL,四个通道共用一个QPLL,每个bank有两对差分时钟输入引脚。 下面时钟的使用进行讲解,后续对用户时钟进行讲解。如下图所示,差分时钟进入FPGA之后,先经过IBUFDS_GTE2转换为单端时钟,然后作为QPLL或者CPLL的时钟输入,QPLL或者CPLL的输出时钟作为发送和接收部分的时钟信号。  图7 四通道配置 要注意在生成IP时,一般将QPLL的代码放到IP外部,那么用户就可以在调用多通道高速收发器时,直接把剩余的IP多次例化,共用一个QPLL。IP界面的配置如下:  图8 将QPLL放在示例工程中 一般当线速率大于6.6Gb/s时,必须使用QPLL,否则可以选择使用QPLL或者CPLL。如下图所示,如果线速率设置为10Gbps,则将差分时钟频率设置为156.25MHz,之后3处的发送和接收通道的时钟来源只能是QPLL,因为线速率大于6.6Gbps。  图9 参考时钟频率即来源设置 下图是IBUFDS_GTE2原语对应的器件图,IB和I是差分输入引脚,CFB是低电平使能引脚,O是输出单端时钟引脚,ODIV2是将输出时钟二分频的信号引脚。图中另一个引脚手册中也没有说明,实际也没有使用,暂时不知道功能。  图10 IBUFGDS_GTE2器件 下图是GTXE2_COMMON的框图,与图7相对应。QPLL前面有一个数据选择器,用于控制QPLL的输入。 其中GTREFCLK0和GTREFCLK1是该bank的两对差分时钟管脚转换后的单端时钟信号。  图11 QPLL时钟输入 芯片必须有三个及以上的高速bank,才会同时有GTNORTHREFCLK0、GTNORTHREFCLK1、GTSOU THREFCLK0、GTSOUTHREFCLK1这四个时钟信号。 如下图所示,虚线框分别表示两个不同的bank,上面的bank位于下面bank的北面,那么下面的bank可以将北面bank的差分时钟通过GTSOUTHREFCLK0、GTSOUTHREFCLK1端口作为QPLL的时钟输入。 同样的道理下面的bank位于上面bank的南面,上面bank可以通过GTNORTHREFCLK0、GTNORTHR EFCLK1把下面bank的差分时钟作为自己QPLL的输入时钟。  图12 两个bank时钟输入方式 注意7系列FPGA的每个差分时钟最多只能驱动12个高速收发器,且只能驱动bank内部高速收发器或者南北相邻bank内部的高速收发器。 图11中的GTGREFCLK端口是指来自FPGA内部逻辑的时钟信号,这个端口只能用作仿真,不能用来上板,原因应该是其他bank的逻辑时钟无法达到高速bank要求的时钟质量和速度吧。 下图是CPLL的外部结构,与QPLL基本一致,只不过CPLL位于高速收发器通道内部。  图13 CPLL时钟输入 差分输入时钟的一般使用方式如下所示,采用一个时钟驱动bank内部的4个高速收发器通道。  图14 一个bank时钟输入方式 两个差分时钟管脚驱动通道的不同时钟端口,如下图所示,此时需要通过控制数据选择器的地址信号确定具体的时钟信号。  图15 一个bank时钟输入方式 经过前文分析,一对差分时钟管脚可以最多驱动三个bank的高速收发器通道,如下图所示,只不过图中上、下两个bank的时钟端口应该是画错了,不应该连接GTREFCLK0。  图16 中间bank时钟驱动上、下三个bank时钟连接 在IP核例化时,如下图所示,可以选中图中左侧黄色的块,勾选Use GTX X0Y0确定启用该高速收发器,同时可以选择该高速收发器的时钟来源。 但这种方式很麻烦,必须知道该通道在FPGA中的位置。在实际使用时,可以随意选择,直接在XDC文件中约束收发器的引脚即可,XDC的优先级大于此处设置的优先级。时钟的来源也与后续图18中的代码有关,此处设置只对IP的示例工程有效,后续可以在自己工程代码中进行修改。  图17 时钟来源及启用高速收发器 在设计GT IP核之后,示例工程中会使用IBFGDS_GTE2和GTEX2_COMMON原语即模块,一般用户可以把这两个模块放在GT收发器模块的顶层,与多个高速收发器共同使用。 将示例工程整理之后,如下图所示,1是外部的差分时钟引脚输入,2是单端时钟输出,单端时钟引脚接到GTEX2_COMMON模块的参考时钟0,因此数据选择器的地址信号为3’b001,5处就是输出给GT_CHANEL的参考时钟信号了。  图18 QPLL及差分时钟转换 对于上图中5的信号,锁定信号与普通锁相环的锁定信号一致。主要关注一下qpllclk和qplloutrefclk,如下图所示,qpllclk用于TX和RX通道,与用户其实没有多大关联。 而qplloutrefclk可以通过数据选择器生成TXOUCLK和RXOUTCLK,这两个信号可以通过MMCM生成用户数据接口的时钟信号,也就是处理用户输入、输出并行数据的。 关于TXOUCLK信号将在发送通道的时候进行讲解。  图19 QPLL输出时钟信号 图18的u_common是对GTXE2_COMMON原语进行封装,将不使用引脚去掉了的,由于zynq7030只有一个GT bank,南北的参考时钟信号不可能用到,因此在内部直接将该端口接地处理,如下图所示。  图20 GT_COMMON原语调用 每个GTX收发器通道包含一个CPLL,内部通道时钟架构如下图所示。TX和RX时钟分频器可以分别选择来自QPLL或CPLL的时钟,从而允许TX和RX数据路径使用不同的参考时钟输入以异步频率工作。  图21 内部通道时钟架构 TX和RX时钟分频器模块控制PMA和PCS模块使用的串行和并行时钟的产生。如果TX和RX数据路径以相同VCO频率的整数倍线路速率工作,则它们可以共享CPLL。 下图是CPLL的内部原理框图,M、N这些参数都可以在原语中设置,进而改变倍频/分频系数,但很多时候都是直接在GT IP中对其他数据、协议参数配置后,自动生成CPLL的时钟,不需要人为配置系数,可以暂时不关心。 但本文既然提到了,就简单计算下输出时钟的频率吧,下图其实就是一个常用的锁相环结构。对于分频和倍频系数的计算,主要就是抓住输出信号频率及phase Frequency Detector,当其两个输入信号的频率相等时,整个回路锁定。  图22 CPLL内部框图 1处的频率为Fclkin/M,2处的频率为Fclkout/N1/N2,当锁相环锁定时需要满足Fclkout/N1/N2 = Fclkin/M,得到Fclkout = ((N1*N2)/M)*Fclkin,分频系数为(N1*N2)/M。 下图是QPLL的内部框图,原理与上图一致,通过计算可以得到分频系数为(N/(2*M))。  图23 QPLL内部框图 最后还有一个动态重配置的时钟信号,这个信号的频率只要在要求范围内即可,可以是其他bank的时钟信号,对时钟来源没有要求。 动态重配置通过配置一些内部寄存器来修改模块功能,很多芯片都有类似功能。比如摄像头SCCB接口、以太网PHY芯片的MDIO接口,均支持在芯片在工作时通过一些慢速接口来修改寄存器内容,从而实现模式切换的目的,这种方式一般对时钟的频率、质量不会有太高要求,因此DRP时钟可以使用任意的时钟信号。  图24 DRP时钟设置 关于GTX的差分时钟相关内容就讲解到此处,手册前两部分还有回环、复位、动态重配置等功能,但是这些功能必须结合收发通道进行讲解,才有效果。 环回模式一般用于测试FPGA板卡自身的收发通道是否正常,内部的收发逻辑电路的设计是否完成。 GT IP的发送和接收通道会提供给用户两个大复位,一般不会去复位局部的结构。而动态重配置其实很重要,就是在FPGA运行时,通过DRP接口修改内部预留寄存器的参数,达到模式切换的目的,但是初学一般也用不到。 |