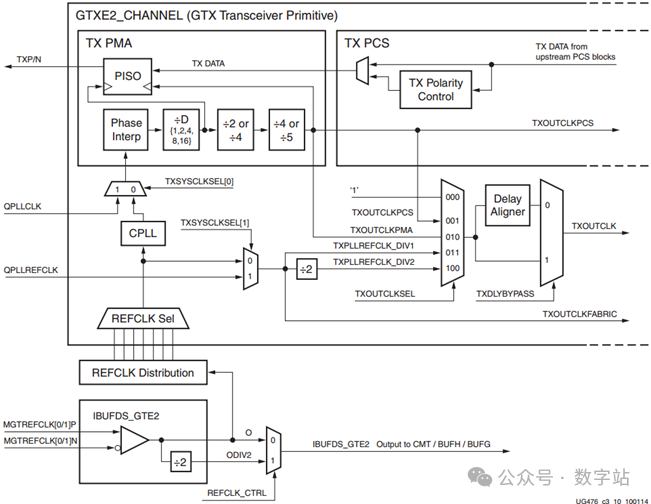

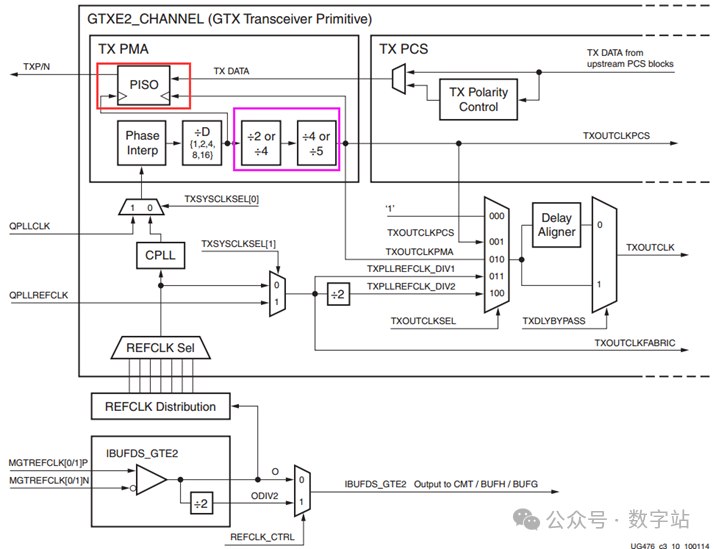

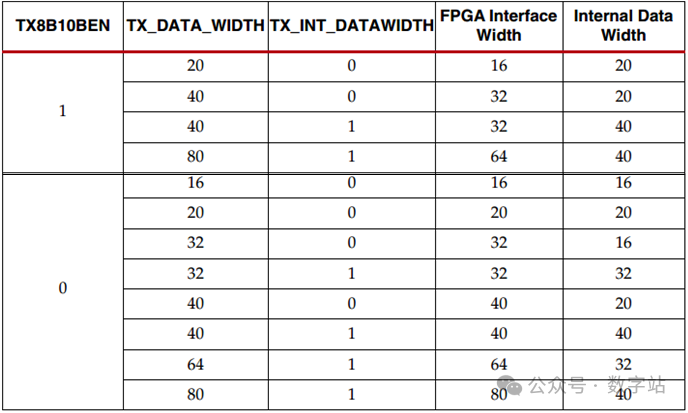

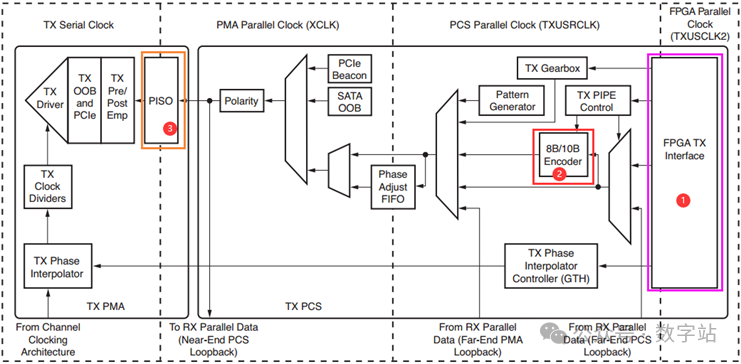

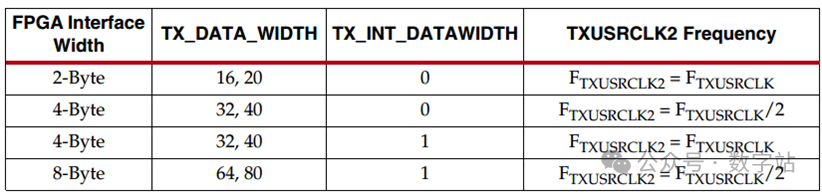

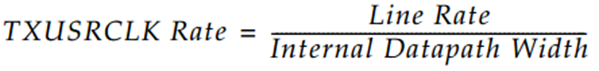

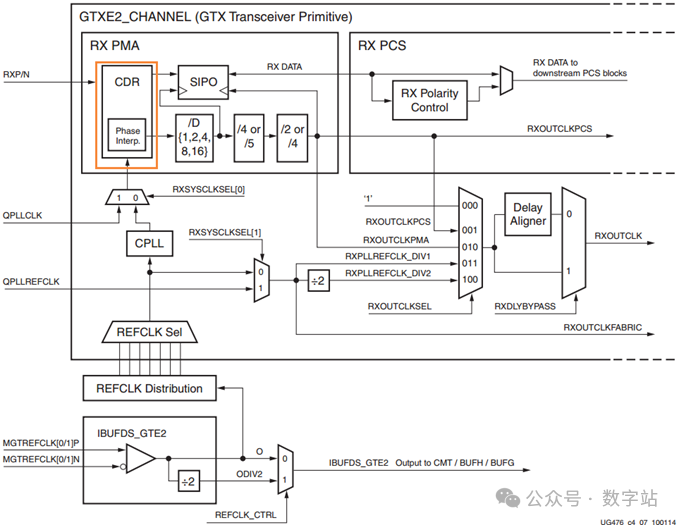

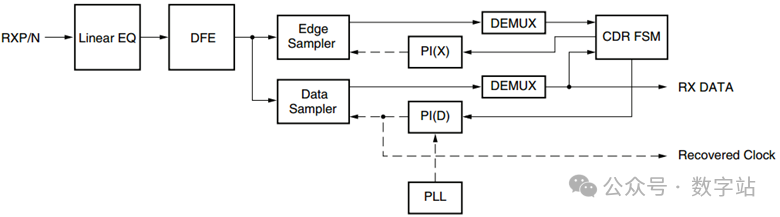

深入解析GTX收发器的时钟架构与数据位宽关系(高速收发器四)前面两篇文章对GTX的外部时钟和内部时钟都做了讲解,而用户对GTX的疑问往往也在于时钟的关系。本文通过前文提到的手册里面的几张框图,对高速收发器内部时钟和共享时钟在进行详细分析,做到大家以后只要看到这些框图,就能够知道其内部工作的一些原理,不需要去背什么文字内容,这也是我比较喜欢分析手册框图的原因。GTX一般会包含参考时钟、USRCLK、USRCLK2、OUTCLK等几个时钟信号,参考时钟只能从高速收发器bank的差分时钟引脚输入,通过IBUFGDS_GTE2转换为单端时钟,输入到QPLL或者CPLL。下图两路差分时钟,一路作为QPLL输入,一路作为CPLL输入,注意QPLLOUTREFCLK就是QPLL输入时钟。  图1 外部参考时钟 上图体现的是共享逻辑的参考时钟和部分通道内部的时钟信号,而内部详细的时钟信号则要通过下图体现。  图2 TX串行和并行时钟分频器 前文对上图各个部分已经详细讲解过了,有兴趣的可以点击查看。本文只是分析并串转换PISO的两个时钟分频系数的关系,跟输入数据位宽的相关关系,进而推出TXUSRCLK和TXUSRCLK2的关系。  图3 TX串行和并行时钟分频器 前文得知并串转换PISO的输出应该是双沿传输数据的,串行时钟通过两个分频器得到并行时钟,分频系数相互组合可以得到8、10、16、20。加上输出串行数据是双沿传输,那么并行数据位宽应该分别对应16、20、32、40。 再看下表,其中FPGA Interface Width是用户需要发送的数据位宽,TX_DATA_WIDTH是用户数据经过编码后的数据位宽,Internal DATA Width是PCS内部每次传输的并行数据位宽。 可以发现Internal DATA Width也只有16、20、32、40这四种取值,由于并串转换模块的限制,导致PCS内部每次最多只能传输40位并行数据。  图4 数据位宽 此处就会涉及到TXUSRCLK和TXUSRCLK2的频率关系,如下图所示,用户数据处于TXUSRCLK2时钟域,而8B10B编码模块输出数据处于TXUSRCLK时钟域。而XCLK的时钟频率与TXUSRCLK基本一致的,如果8B10B编码后的数据位宽与PCS传输并行数据位宽一致,则TXUSRCLK与TXUSRCLK2频率保持一致。  图5 发送通道框图 如果8B/10B编码后的数据位宽是PCS并行传输数据的2倍,则需要将TXUSRCLK变为TXUSRCLK2的2倍,来保证数据吞吐量保持一致。进而得到下表关系,需要结合图4一起观看。  图6 TXUSRCLK2 频率与 TXUSRCLK 的关系 那么TXUSRCLK的频率应该等于高速收发器的线速率除以PCS内部传输的数据位宽,进而通过PCS内部数据位宽与8B10B编码后数据位宽的关系推出TXUSRCLK2的频率,得到下面的表达式。  图7 线速率计算TXUSRCLK 上面是发送通道时钟相关的分析,接收通道其实类似,只不过多了一个CDR,如下图所示。 高速收发器在传输数据时,是没有随路时钟信号,只能过CDR从数据中恢复时钟信号,官方也不可能公开CDR具体实现方式,属于IP关键内容,手册中也只是提供了一些框图,用户也不需要分析其具体实现方式,但需要清楚CDR到底恢复的是什么?  图8 接收通道的时钟结构 上图中QPLL或CPLL输入CDR之后,经过分频处理作为串并转换SIPO的时钟信号。当知道发送方的线速率之后,接收方需要的时钟频率其实就是已知的了,CDR只不过是恢复时钟和数据之间的相位关系而已。 上述其实是通过QPLL或CPLL生成指定频率的时钟,然后CDR对接收的数据和时钟进行处理,调整时钟相位,让时钟边沿与数据中心对齐,从而稳定采集数据。 下图是CDR原理款图,其中的PLL输入时钟就是上图中QPLLCLK或者CPLL输出时钟,采集数据边沿和中心去调整时钟相位。  图9 CDR框图高速收发器时钟相关知识就到此结束了,其余内容可以查看前面两篇内容,本文只是把时钟与数据位宽的关系通过框图联系,使得知识更加连贯。 |