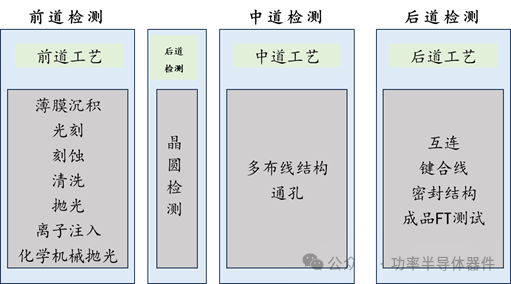

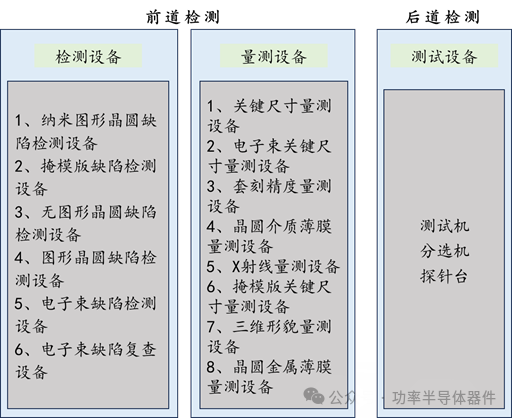

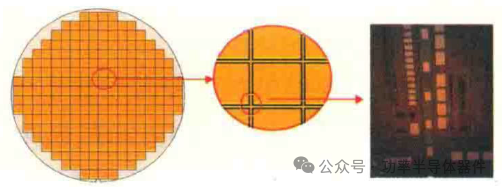

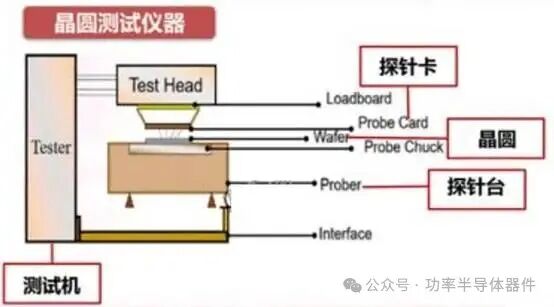

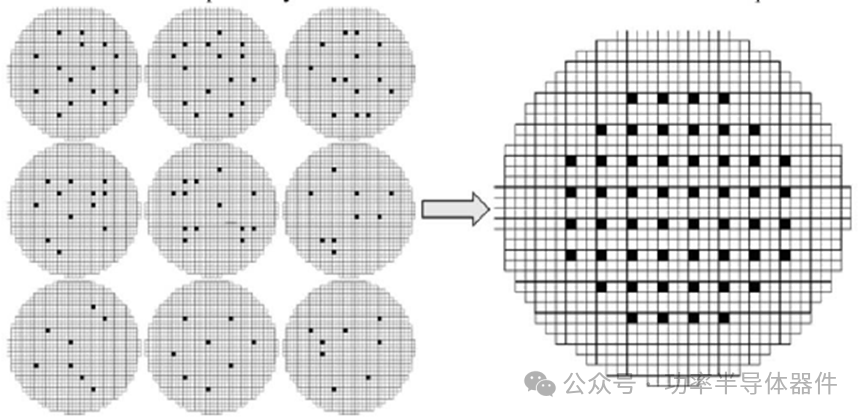

在半导体产业的制造流程上,主要可分为集成电路(器件)设计、晶圆制造、测试及封装四大步骤。而整个半导体生产环节中,测试可分为前道检测、中道检测和后道测试。不同阶段测试内容有所不同,所用到的测试设备也有所不同,如下图所示。  前道检测主要在芯片制造过程的早期,对晶圆上的芯片进行一系列测试,主要包括颗粒度、薄膜测试等,这主要是由于在芯片制造过程中会产生颗粒、互连、静电损伤等工艺缺陷。具体缺陷有空气中分子污染或由环境引起的有机物或无机物颗粒;工艺过程引起的划痕、裂纹和颗粒、覆盖层缺陷和应力;在从掩膜到晶圆的图形转移过程中,由于设计偏差导致的布局和关键尺寸的偏差和变化;原子通过层和半导体散装材料的扩散等。前道检测中不少检测和量测设备以及项目都在失效分析篇有所介绍。 中道检测则是主要面向先进封装,以光学等非接触式手段针对重布线结构、凸点与通孔等晶圆制造环节的质量控制。 后道检测主要是晶圆级测试(Wafer Level Test),包括晶圆接受测试(Wafer Acceptance Test,WAT),晶圆测试(Chip Probing,CP)和成品最终测试(Final Test,FT)。 WAT测试 WAT是工艺控制检测(PCM)。WAT是在晶圆产品流片结束之后和品质检验之前,测量特定测试结构的电性参数。WAT的目的是通过测试晶圆上特定测试结构的电性参数来检测每一片晶圆产品的工艺情况,以评估半导体制造过程的质量和稳定性,判断晶圆产品是否符合该工艺技术平台的电性规格要求。 WAT数据可以作为晶圆产品交货的质量依据,而且WAT数据还可以反映流片线上的实际生产情况,通过收集和分析WAT数据可以监测产线情况,也可以判断产线变化的趋势。 晶圆上用于收集WAT数据的测试结构成为WAT测试结构(WAT testkey)。WAT测试结构并不在实际芯片产品内部,如果要设计在实际芯片产品内部则是会占用额外的芯片面积,而额外的芯片面积会增加芯片成本(当然也可以单独划一片区域作为工艺检测图形)。晶圆厂一般会把WAT测试结构设计在晶圆上芯片(die)之间的划片槽中。划片槽的宽度可以从60um做到150um。  CP测试 芯片测试是检查晶圆上芯片各项性能是否满足规格书中的要求,主要包括漏电流、电阻、压降、耐压等等。其主要是通过对晶圆上的每颗芯片进行电特性检测等,以检测和淘汰不合格芯片,因此CP测试是提高半导体器件良率的关键步骤之一。 CP测试的原理如下,首先需要将晶圆固定在待测卡盘上吗,根据芯片大小和晶圆上芯片布局设置探针台,测试机的测试头持有探针卡。将探针卡定位在摸具的键合面上,接触探针以建立用于测试的电连接,并在测试之后提起探针并将它们定位在下一个芯片上。  探针台通过数据传输到一个测试仪上。当某颗芯片被检测出有问题时,测试机即会将此颗芯片进行标注,所有芯片测试完成后,测试机将会输出一个芯片布局图来表示该颗晶圆上好芯片和坏芯片的位置,如下图所示。在下一步划片和封装时,坏芯片就会被挑选出来并抛弃,从而有效提高产品良率,降低成本。  FT测试 FT测试主要是指芯片完成划片和封装后,通过分选机和测试机配合使用,除了CP测试中的静态测试项目,还有对芯片进行功能参数性能以及可靠性测试,保证最终出货芯片的功能和性能都能够达到设计规范要求。 |