芯片测试不仅仅是发现和剔除有缺陷的芯片,它更是一个贯穿芯片设计、制造、封装乃至应用全生命周期的质量保证体系。通过系统化的测试,可以验证芯片是否满足设计规格,确保其在各种工作条件下的稳定性和一致性,并最终保障终端产品的质量和用户体验。本文将深入探讨集成电路芯片测试的各个方面,包括其基本概念、主要类型、关键流程、常用技术、面临的挑战以及未来发展趋势,旨在为读者提供一个全面而详尽的芯片测试知识图谱。

芯片测试的基本概念与重要性

集成电路芯片测试,简而言之,就是通过施加特定的输入信号(激励)并测量其输出响应,来验证芯片的功能、性能和可靠性是否符合设计要求和规格书的过程。其核心目标是识别并剔除因制造缺陷、设计错误或材料问题导致的失效芯片,确保只有合格的芯片才能进入市场。

测试的重要性体现在多个层面:

质量保证:这是最直接的目的。通过测试,可以确保出厂的每一颗芯片都能正常工作,满足预定的电气参数和功能要求,从而维护品牌声誉和客户信任。

成本控制:虽然测试本身需要投入成本,但相比于将有缺陷的芯片组装到更复杂的系统中(如手机、服务器)后再发现问题,其成本要低得多。早期发现并剔除坏芯片,可以避免后续昂贵的返修、召回和保修成本。

可靠性提升:严格的测试流程,特别是老化测试(Burn-in)和环境应力筛选(ESS),可以加速暴露潜在的早期失效问题,筛选出“早夭”芯片,从而提高最终产品的长期可靠性。

工艺反馈:测试结果为晶圆制造厂(Foundry)和封装厂提供了宝贵的反馈信息。通过分析测试数据,可以定位制造过程中的薄弱环节,优化工艺参数,提高良率(Yield)。

设计验证:对于设计公司(Fabless),测试是验证其设计是否成功的关键步骤。量产前的工程测试(Engineering Test)和小批量试产测试,有助于发现设计中的潜在问题并进行修正。

芯片测试的主要类型

集成电路芯片测试是一个多层次、多阶段的过程,根据测试目的、阶段和方法的不同,可以分为以下几大类:

1. 功能测试 (Functional Test)

功能测试是最基础也是最重要的测试类型。它主要验证芯片是否能正确执行其设计的功能。测试向量(Test Vectors)通常是根据芯片的功能规格书(Datasheet)或硬件描述语言(HDL)模型生成的,模拟芯片在实际应用中的各种输入组合,并检查输出是否与预期相符。功能测试通常在较低的频率下进行,侧重于逻辑正确性而非速度。

2. 结构测试 (Structural Test)

结构测试关注的是芯片内部的物理结构,特别是晶体管和互连线的连通性。其核心是扫描测试(Scan Test) 和 内建自测试(Built-In Self-Test, BIST)。

· 扫描测试:通过在设计阶段插入特殊的扫描链(Scan Chain),将时序电路转换为可控制的组合逻辑。测试时,可以串行地将测试向量移入扫描链,然后捕获输出响应并串行移出,便于自动化测试设备(ATE)进行比较。这种方法极大地提高了测试的可控性和可观测性。

· 内建自测试(BIST):在芯片内部集成测试电路,使其能够自行生成测试向量、执行测试并评估结果。BIST常用于存储器(Memory BIST)和复杂的数字逻辑模块,可以减少对外部测试设备的依赖,缩短测试时间。

3. 参数测试 (Parametric Test)

参数测试测量芯片的电气特性参数,如电压、电流、电阻、电容、增益、带宽、建立/保持时间等。这些测试确保芯片的电气性能在规定的规格范围内。例如,测量电源电流(IDD)是否在正常范围内,或者输出驱动能力是否满足要求。参数测试对于模拟电路、混合信号电路和功率器件尤为重要。

4. 速度测试 (Speed Test) 或 时序测试 (Timing Test)

速度测试验证芯片能否在规定的最高工作频率下稳定运行。这通常通过施加高速的测试向量并检查时序裕量来完成。对于高性能处理器、高速接口(如DDR、PCIe)等芯片,速度测试至关重要。它可能涉及延迟测试(Delay Test),专门检测由于制造缺陷导致的信号延迟增加。

5. 可靠性测试与环境测试

这类测试旨在评估芯片在极端或长期使用条件下的表现。

· 老化测试(Burn-in):将芯片置于高温和高电压条件下运行一段时间,以加速暴露潜在的早期失效(如“婴儿死亡率”)。

· 环境应力筛选(ESS):包括温度循环、热冲击、湿度测试、机械振动等,模拟芯片在不同环境下的可靠性。

· 寿命测试:通过加速老化模型预测芯片的长期使用寿命。

芯片测试的关键流程

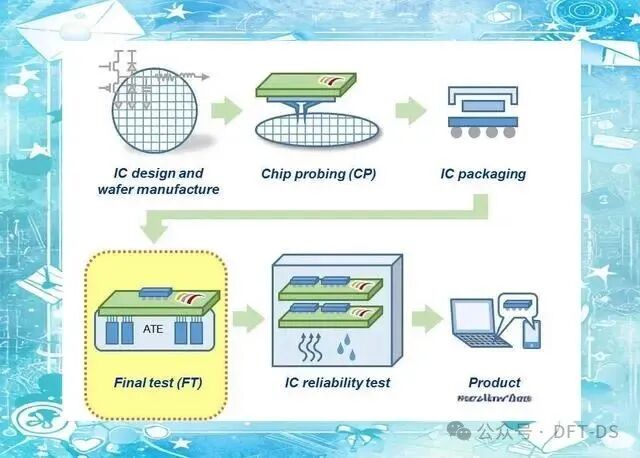

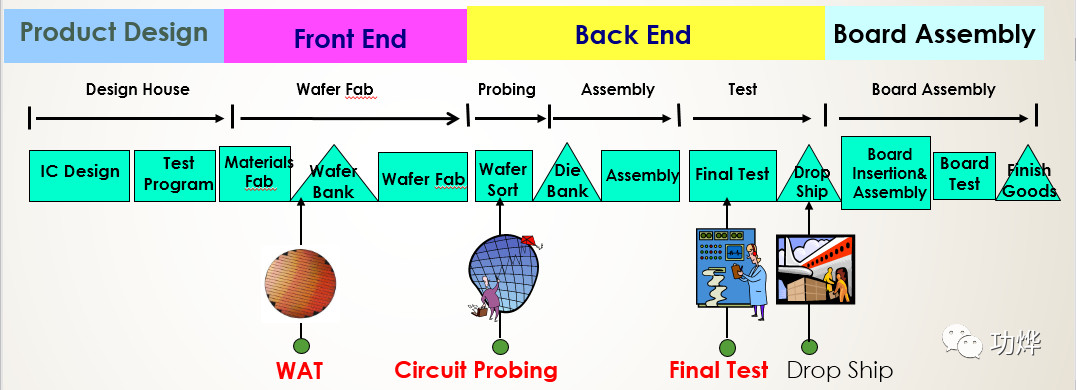

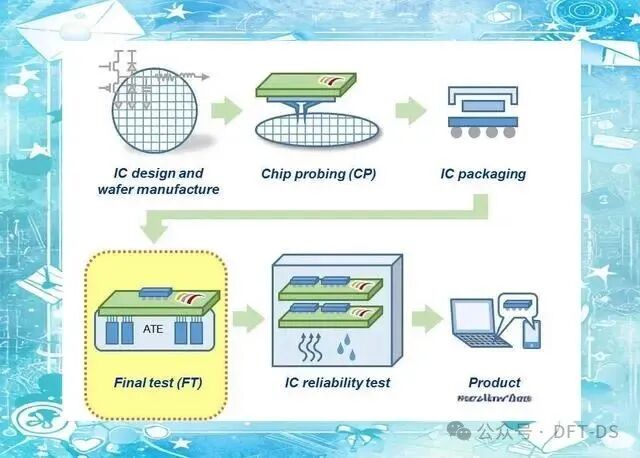

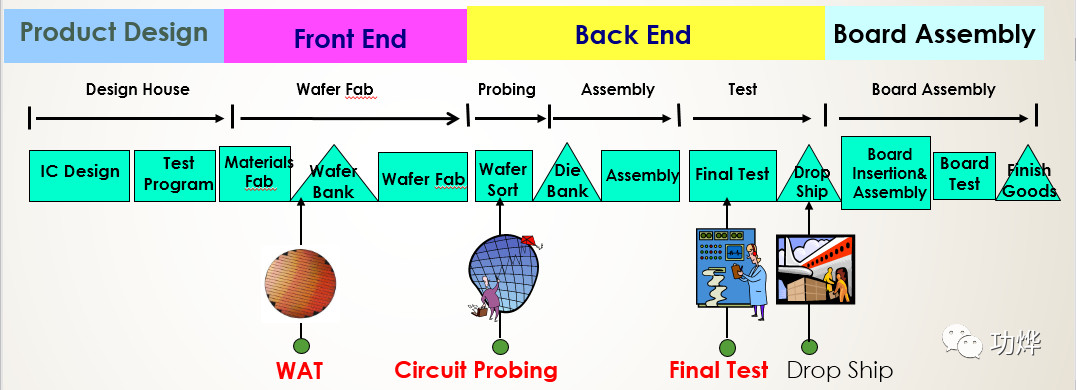

一个完整的芯片测试流程通常贯穿于芯片的整个生命周期,主要分为以下几个阶段:

1. 设计阶段:可测试性设计(DFT)

可测试性设计(Design for Testability, DFT)是在芯片设计初期就考虑如何便于后续测试。DFT工程师在电路设计中嵌入特定的结构,如扫描链、边界扫描(Boundary Scan, JTAG)、BIST模块等。DFT是现代复杂芯片测试的基础,它极大地提高了测试的覆盖率和效率。DFT设计完成后,需要进行DFT验证,确保测试结构正确无误。

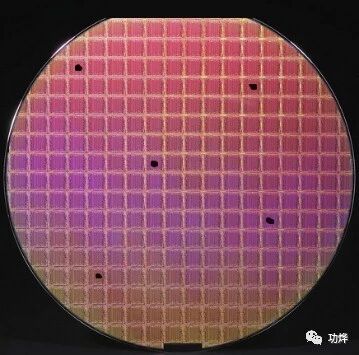

2. 晶圆测试(Wafer Test / CP Test)

晶圆测试,也称为晶圆探针测试(Wafer Probe Test)或CP(Circuit Probing)测试,是在芯片被切割和封装之前,在晶圆(Wafer)上进行的。使用精密的探针卡(Probe Card)与晶圆上的焊盘(Pad)接触,连接到自动测试设备(ATE),对每个芯片(Die)进行初步的功能和参数测试。主要目的是筛选出明显的制造缺陷,避免将已知的坏芯片送去封装,从而节省封装成本。测试结果会生成“晶圆图”(Wafer Map),直观地显示每个芯片的测试状态(通过/失败)。

3. 封装后测试(Final Test / FT Test)

封装后测试是在芯片完成封装(如QFP、BGA、CSP等)之后进行的最终测试。由于封装过程本身也可能引入缺陷(如引线断裂、虚焊、封装体开裂等),因此需要再次进行全面的测试,包括功能、参数、速度等。封装后测试通常在更接近实际应用的条件下进行,可能包括不同温度、电压的测试。这是芯片出厂前的最后一道质量关卡。

4. 系统级测试(System-Level Test, SLT)

对于一些极其复杂或对可靠性要求极高的芯片(如服务器CPU、AI芯片),在封装后测试之外,还可能进行系统级测试。SLT将芯片安装在模拟真实应用场景的测试板上,运行实际的操作系统和应用程序,以验证其在系统环境中的完整功能和性能。SLT能发现一些在传统ATE测试中难以捕捉的复杂交互问题,但成本和时间开销也更大。

常用的测试技术与设备

1. 自动测试设备(ATE - Automatic Test Equipment)

ATE是芯片测试的核心硬件平台,通常由高性能计算机控制,集成了多种精密的仪器模块,如:

· 数字向量发生器(Digital Pattern Generator):产生复杂的数字测试向量。

· 精密测量单元(PMU - Parametric Measurement Unit):测量电压、电流等参数。

· 数字波形采集器(Digital Waveform Capture):捕获和分析芯片的数字输出响应。

· 任意波形发生器(AWG)和数字转换器(ADC):用于模拟和混合信号测试。

· 时钟发生器和时序测量单元:提供精确的时钟信号并测量时序参数。

· 电源单元(PSU):提供稳定可调的电源电压。

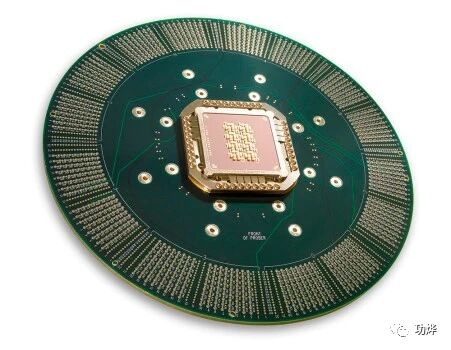

2. 探针卡(Probe Card)

用于晶圆测试,是连接ATE和晶圆上芯片焊盘的桥梁。探针卡上安装有微小的探针(Probe Needle),精确对准并接触芯片的焊盘。探针卡的设计和制造非常精密,需要考虑信号完整性、热膨胀系数匹配、耐用性等因素。

3. 测试插座(Test Socket)与负载板(Load Board)

用于封装后测试。测试插座用于固定和连接被测芯片(DUT - Device Under Test),负载板则连接ATE和测试插座,有时也集成一些信号调理或测试辅助电路。

4. 测试向量生成与压缩技术

随着芯片复杂度的指数级增长,测试向量的数量也急剧膨胀,导致测试时间过长,成本高昂。因此,高效的测试向量生成和压缩技术至关重要:

· 自动测试向量生成(ATPG - Automatic Test Pattern Generation):利用EDA工具根据电路网表和故障模型(如Stuck-at Fault, Transition Fault, Path Delay Fault)自动生成高覆盖率的测试向量。

· 测试压缩(Test Compression):通过在芯片内集成编码/解码电路,将大量的测试向量在ATE端压缩后传输,在芯片内部解压后施加,显著减少测试数据量和测试时间。常见的压缩技术有Mentor Graphics的TestKompress、Synopsys的TetraMAX等。

5. 边界扫描(JTAG - IEEE 1149.1)

边界扫描是一种标准的测试技术,通过在芯片的I/O引脚周围添加一个移位寄存器链(边界扫描链),实现对芯片间互连、引脚连接性的非侵入式测试,特别适用于PCB板级的测试。

集成电路芯片测试WAT/CP和FT/SLT介绍

图 集成电路设计、制造、封装流程示意图

WAT 测试:

WAT(Wafer Acceptance Test)测试,也叫PCM(Process Control Monitoring),对Wafer 划片槽(Scribe Line)测试键(Test Key)的测试,通过电性参数来监控各步工艺是否正常和稳定,例如CMOS的电容,电阻, Contact,Metal Line 等,一般在wafer完成制程前,是Wafer从Fab厂出货到封测厂的依据,测试方法是用Probe Card扎在Test Key的Metal Pad上,Probe Card另一端接在WAT测试机台上,由WAT Recipe自动控制测试位置和内容,测完某条Test Key后,Probe Card会自动移到下一条Test Key,直到整片Wafer测试完成。 WAT测试有问题,超过SPEC,一般对应Fab各个Module制程工艺或者机台Shift,例如Litho OVL异常,ETCH CD 偏小,PVD TK偏大等等。WAT有严重问题的Wafer会直接报废。

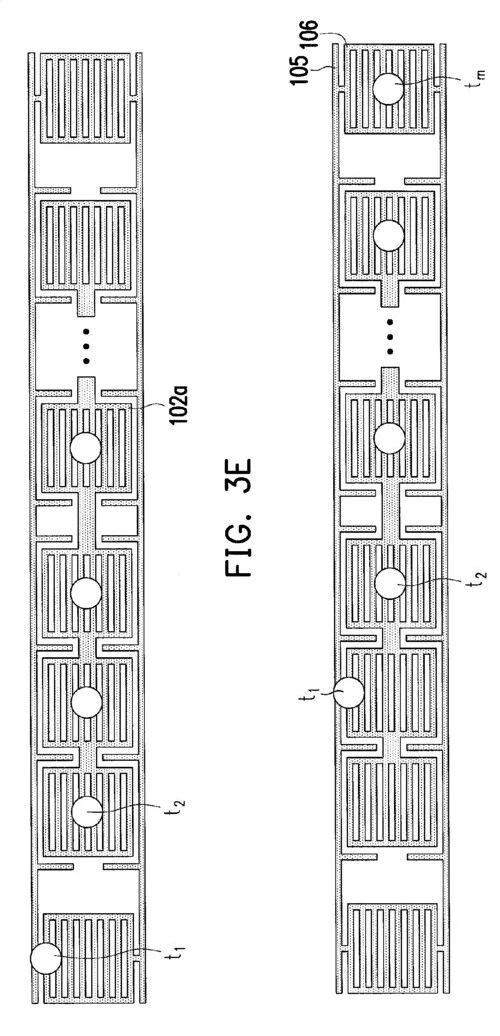

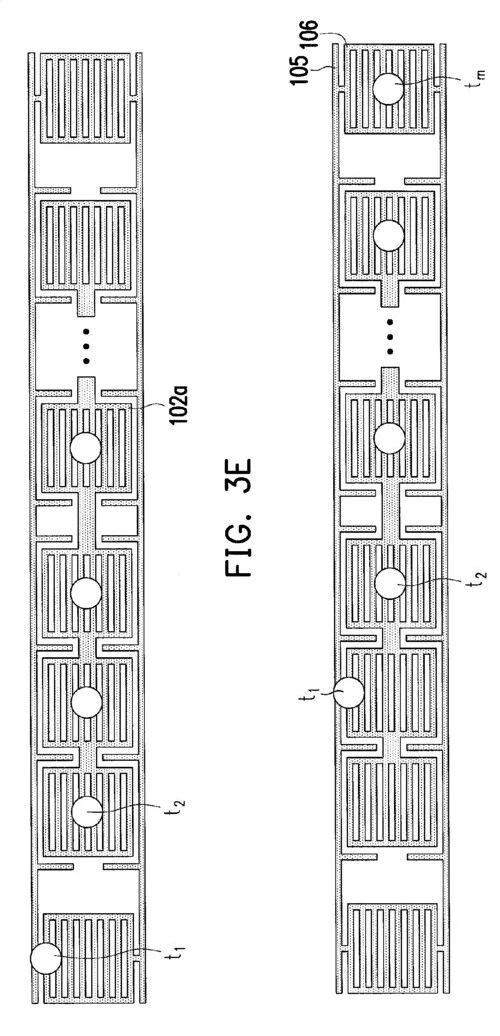

图 Test Key示意图

图 WAT Probe Card 示意图

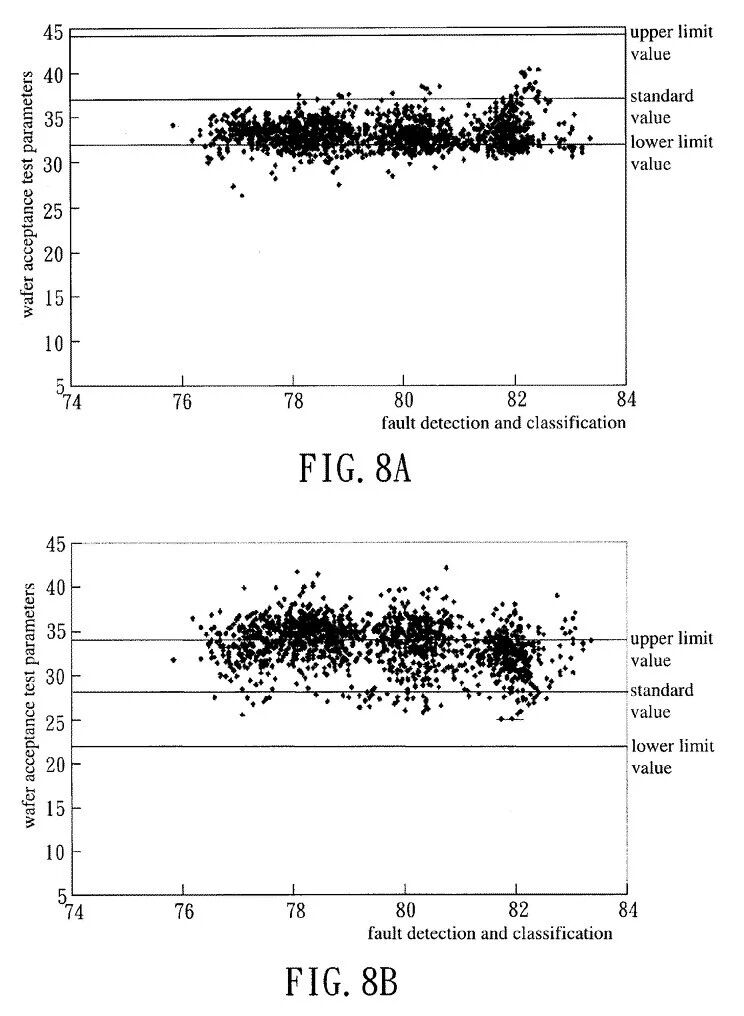

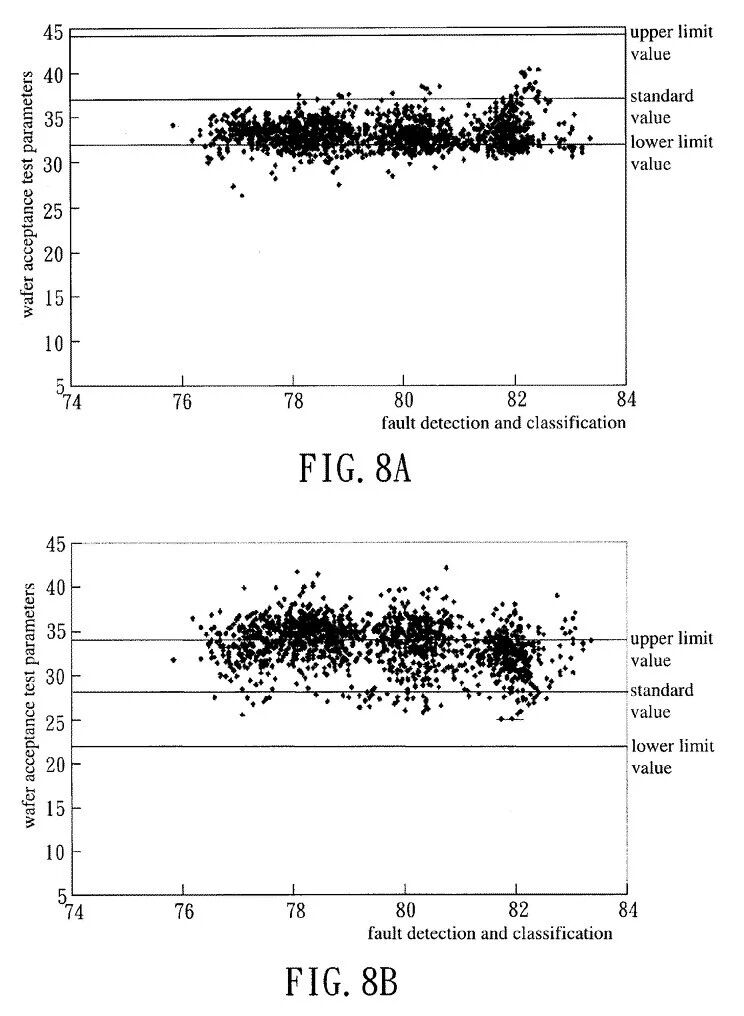

图 WAT data chart

CP 测试:

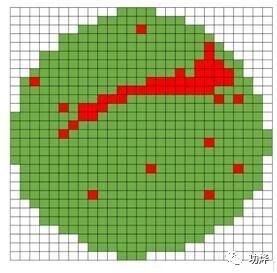

CP(Circuit Probing)也叫“Wafer Probe”或者“Die Sort”,是对整片Wafer的每个Die的基本器件参数进行测试,例如Vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,把坏的Die挑出来,会用墨点(Ink)标记,可以减少封装和测试的成本,CP pass才会封装,一般测试机台的电压和功率不高,CP是对Wafer的Die进行测试,检查Fab厂制造的工艺水平。

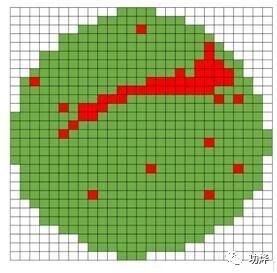

图 黑点为ink

CP测试主要测以下几方面的内容:

Boundary SCAN:

Boundary SCAN用于检测芯片管脚功能是否正确。

SCAN Test:

SCAN用于检测芯片逻辑功能是否正确。

存储器测试:

芯片往往集成着各种类型的存储器(例如ROM/RAM/Flash),为了测试存储器读写和存储功能,通常在设计时提前加入BIST(Built-In SelfTest)逻辑,用于存储器自测。芯片通过特殊的管脚配置进入各类BIST功能,完成自测试后BIST模块将测试结果反馈给Tester。

DC/AC Test:

DC测试包括芯片Signal PIN的Open/Short测试,电源PIN的PowerShort测试,以及检测芯片直流电流和电压参数是否符合设计规格

RF Test:

对于无线通信芯片,RF的功能和性能至关重要。CP中对RF测试来检测RF模块逻辑功能是否正确。FT时还要对RF进行更进一步的性能测试。

其他Function Test。芯片其他功能测试,用于检测芯片其他重要的功能和性能是否符合设计规格。

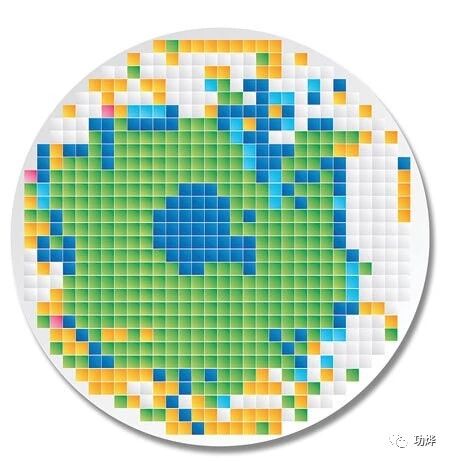

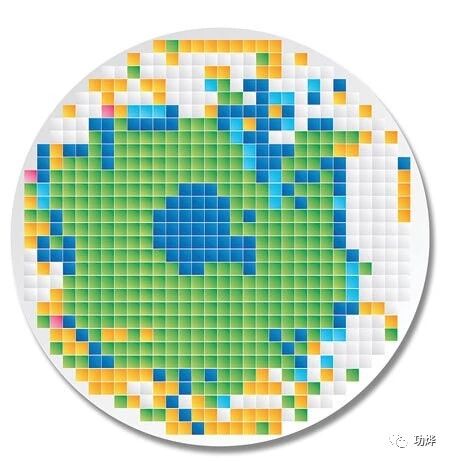

图 CP Bin Map示意图

CP测试程序和测试方法优化是Test Engineer努力的方向,下面介绍几种降低CP测试成本的方法。

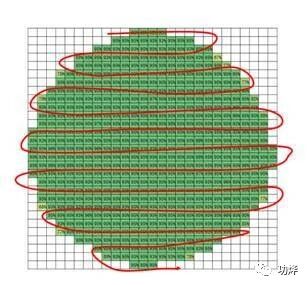

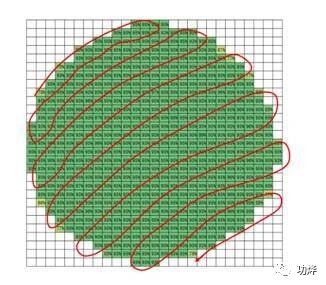

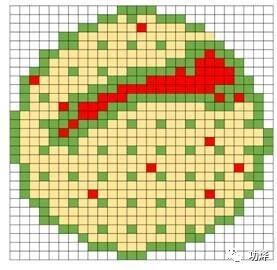

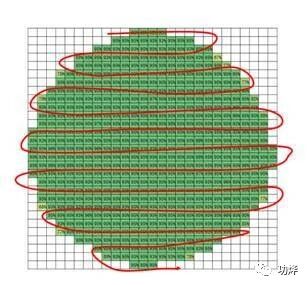

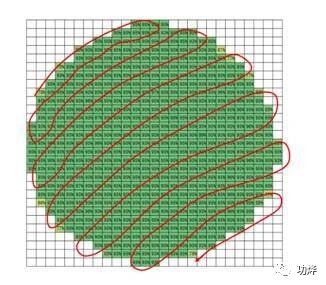

1.同一个Probe Card可以同时测多个Die,如何排列可以减少测试时间?假设Probe Card可以同时测6个Die,那么是2×3排列还是3×2,或者1×6,都会对扎针次数产生影响,不同的走针方向,也会产生Test时间问题。

图 不同走向示意图

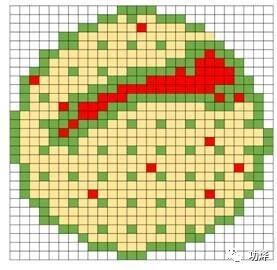

2.随着晶圆尺寸越来越大,晶圆上的Die越来越多,很多公司CP Test会采用抽样检查(Sampling Test)的方式来减少测试时间,至于如何抽样,涉及不同的Test Recipe,一些大数据实时监控软件可以在测试的同时按照一定算法控制走针方向,例如抽测到一个Die失效后,Probe Card会自动围绕这个Die周围一圈测试,直到测试没有问题,再进行下一个Die的抽测,这种方法可以明显缩短测试时间。

图 full map 与 sample test示意图

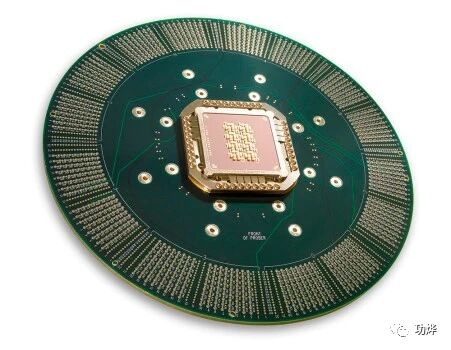

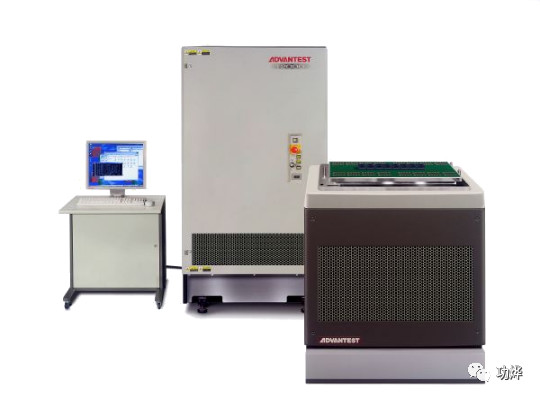

FT 测试:

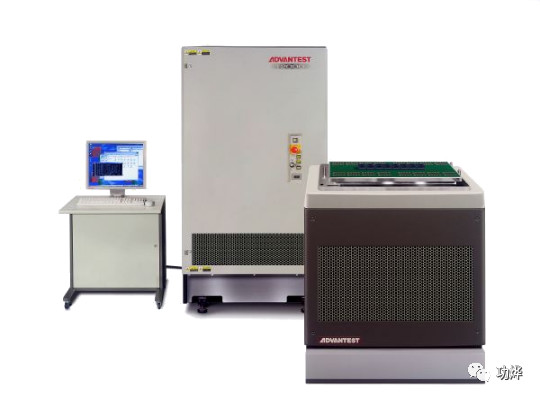

FT(final test)是对封装好的Chip进行Device应用方面的测试,把坏的chip挑出来,FT pass后还会进行process qual和product qual,FT是对package进行测试,检查封装造厂的工艺水平。FT的良率一般都不错,但由于FT测试比CP包含更多的项目,也会遇到Low Yield问题,而且这种情况比较复杂,一般很难找到root cause。广义上的FT也称为ATE(Automatic Test Equipment),一般情况下,ATE通过后可以出货给客户,但对于要求比较高的公司或产品,FT测试通过之后,还有SLT(System Level Test)测试,也称为Bench Test。SLT测试比ATE测试更严格,一般是Function的Test,测试具体模块的功能是否正常,当然SLT更耗时间,一般采取抽样的方式测试。FT测试项目也是根据芯片的功能和特性决定的。

常见的FT测试项一般有:

Open/short test,也就是检查芯片引脚是否有开路或者短路,

DC test也就是检查器件直流的电流和电压的参数。

Eflash test也就是检查内嵌的flash功能和性能,包含读写参数动作功耗和速度等各种参数。

Function test就是测试芯片的逻辑功能。

AC test就是验证交流的规格,包括交流输出信号的质量和信号的实际参数。

RF test这个就是针对有射频模块的芯片,主要验证射频模块的功能和性能参数。

还有就是DFT test,DFT(Design forTest) test主要包括scan扫描设计和内件的自测,也就是BIST(Build In Self Test)和Boundry scan 测试。

图 FT tester 示意图

SLT测试:

SLT是System Level Test的缩写。SLT一种是在其他测试覆盖率无法满足时使用。还有一种就是为了控制成本,因为ATE的测试成本比较高。SLT的测试把芯片放在测试板上,测试板可以用于验证芯片的各个功能。因为他们控制多台测试机,这样可以实现批量的测试。

SLT测试需要的硬件设备包括测试板、测试插座、Handler、Change Kit以及测试主机与连接线等。SLT测试属于定制化测试,软件部分灵活度比较高,不需要基于自动化测试平台开发,完全由测试工程师自主开发。SLT测试内容通常包括芯片功能测试、高速接口测试以及DDR内存相关的测试等。与FT测试相同,程序会根据测试结果Pass或者Fail对芯片进行物理分Bin。

WAT是在晶圆制造过程中进行的测试,通过对Die与Die之间Scribe Line的Test Key电学性能的测试,来监控Fab制程的稳定性;CP测试是制造完成后,封测之前进行的电学测试,把坏的Die标记出来,减少封装的成本;FT是Die切割,打磨,封装后进行器件功能性的测试,可以评价封测厂的封装水平,只有所有的测试都通过后,才可以应用到产品上。

以上四种主要测试之外 ,有的芯片可能还要进行一些可靠性测试,包括以下内容:

ESD,也就是静电抗扰度测试

Lateh up就是闩锁测试

HTOL就是高温工作寿命测试

LTOL就是低温工作寿命测试

TCT温度循环测试

HAST高加速温度温湿度应力测试

其他特殊要求的测试

总结:

集成电路芯片测试是连接芯片设计与制造、确保产品质量和可靠性的关键桥梁。它是一个融合了电子工程、计算机科学、材料科学和统计学等多学科知识的复杂领域。从设计阶段的DFT,到晶圆上的探针测试,再到封装后的最终验证,每一个环节都至关重要。随着半导体技术的持续进步,芯片测试面临着前所未有的挑战,但也孕育着巨大的创新机遇。未来,更智能、更高效、更全面的测试技术将成为推动整个半导体产业向前发展的核心动力之一。深入理解和掌握芯片测试的原理、方法和趋势,对于半导体行业的从业者、研究人员乃至关注科技发展的公众都具有重要意义。

|