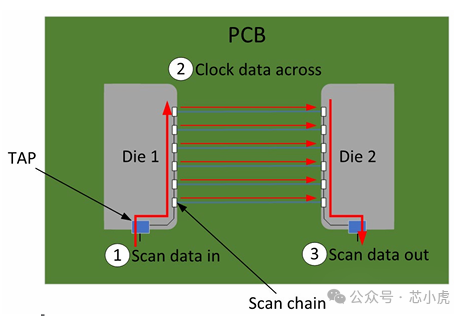

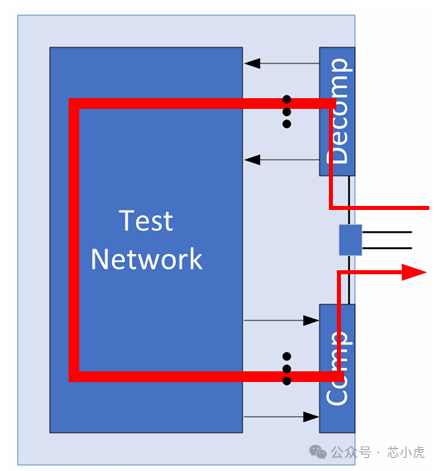

Hello,大家好,今天我们来聊一聊先进封装中的芯片测试。先进封装中的芯片测试,其本质与封装中单个裸片的测试相同,但流程更为复杂。测试电路与测试标准的核心目标一致 —— 使电路中潜在的缺陷处于可控与可观测状态。若无法控制某些节点,就无法对其进行全面测试;若无法观测结果,即便成功执行了测试,也无法得知结果,测试也就失去了意义。而在一个封装中集成多个裸片,会进一步增加可控性与可观测性的实现难度。多年来,半导体行业主要采用两种互补的测试方法。第一种是 IEEE 1149.1 标准,也称为 JTAG(即联合测试行动组,最初制定该标准的委员会);第二种是所谓的 “可测试性设计”(design-for-test)。 JTAG 支持扫描测试,即能够将数据串行扫描输入测试架构、执行测试,然后将结果扫描输出。用于扫描输入数据的寄存器是专门为测试设计的,这些寄存器串联形成的序列被称为 “扫描链”。这种串行方式至关重要,尤其是在该标准诞生之初,可用于测试的引脚数量极为有限。实际上,JTAG 测试访问端口(TAP)仅包含 4 个引脚(可选配第 5 个复位引脚)。 JTAG 最初旨在测试印刷电路板(PC board)的连接。通过向一个芯片的每个引脚加载数据,可在与之相连的芯片上检测结果,从而验证 PCB 连接的完整性。这一方法同样适用于测试封装中基板上的芯粒(chiplets)。 但由于需要在封装完成后测试芯片内部,企业也在芯片内部部署了扫描链。事实上,在当时,内部测试可能比外部测试更为普遍。  早期测试中,通过封装引脚驱动扫描链进行内部测试是可行的,因为当时的目标缺陷多为简单的 “固定型故障”(stuck-at faults)。但随着集成度的提高和新故障模型的出现,更高效的测试方法成为必需。这一时期催生了 “可测试性设计”(DFT),其中包括自动测试图形生成(ATPG)和压缩技术。EDA 公司开发的技术能够在设计阶段生成测试图形时,对大量测试输入数据进行压缩,以加快测试时的加载速度。芯片上的电路会对测试输入进行解压缩,并通过专用测试网络传输。测试结果并非逐位扫描输出,而是被压缩成一个小得多的 “特征码”,随后可将其扫描输出并与预期结果对比。这类测试技术的广泛应用,催生了对一种通用机制的需求 —— 该机制需能以类似 JTAG 的方式设置、配置和控制测试电路。由此,一项新标准应运而生,即 IEEE 1687,俗称 “内部 JTAG”(internal JTAG,简称 IJTAG)。  |