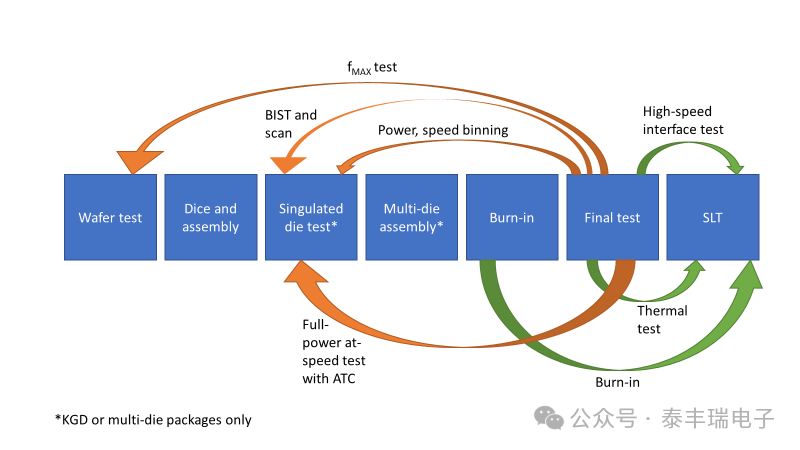

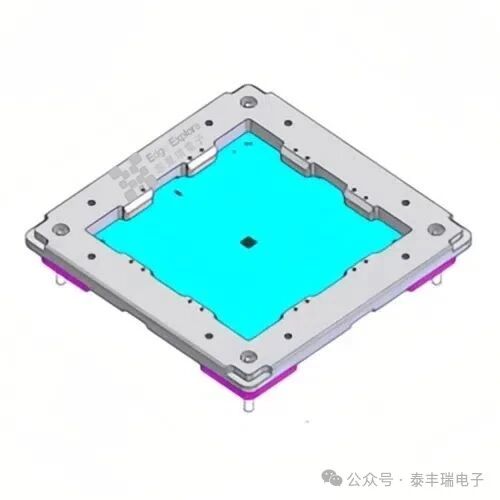

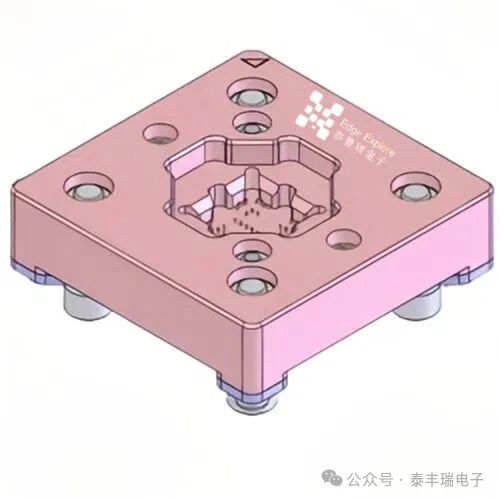

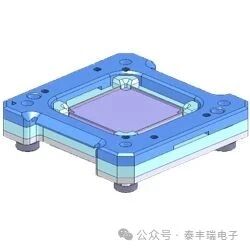

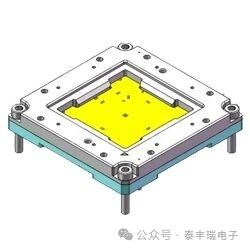

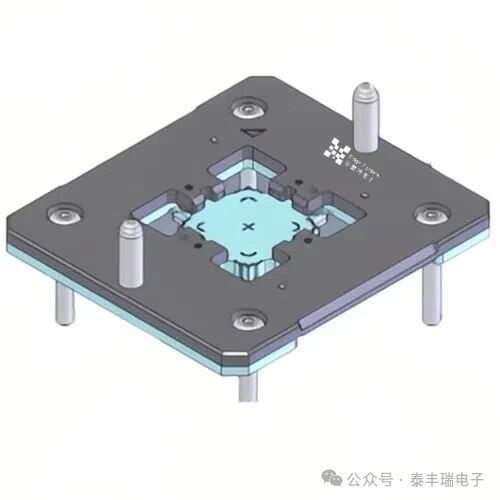

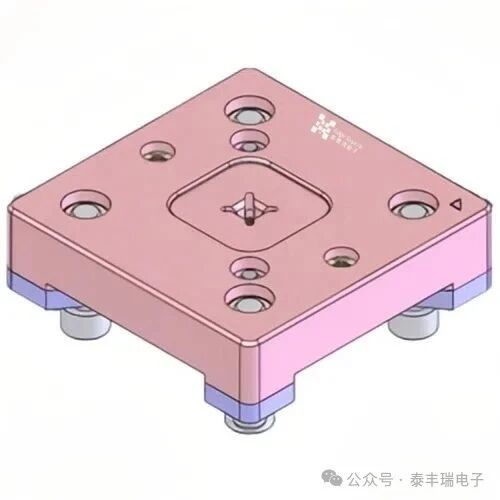

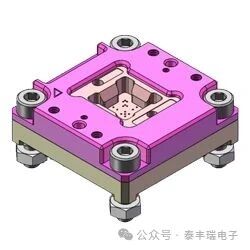

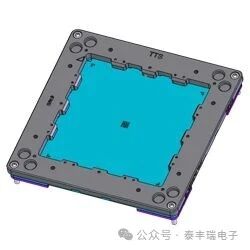

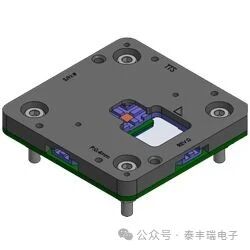

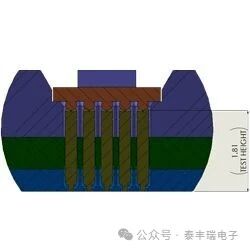

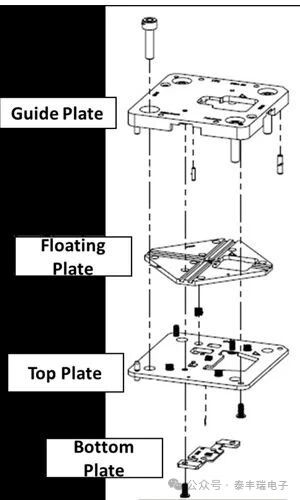

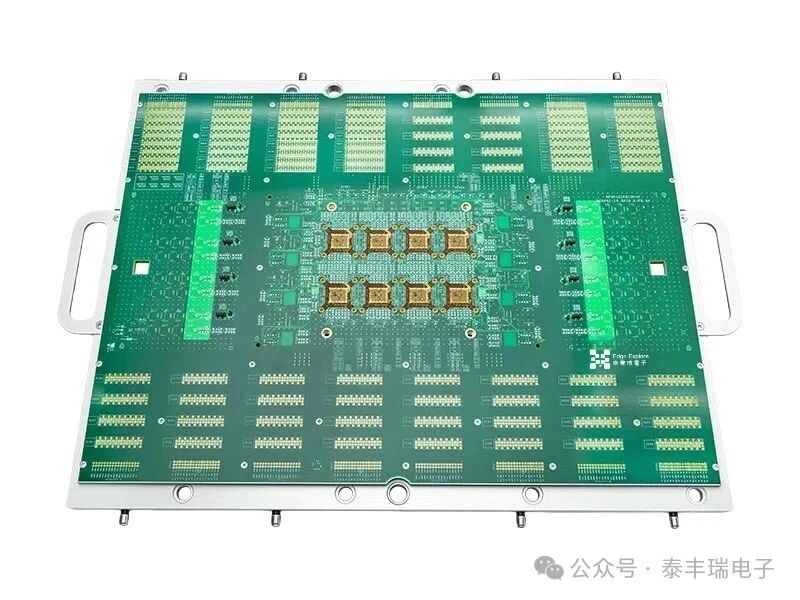

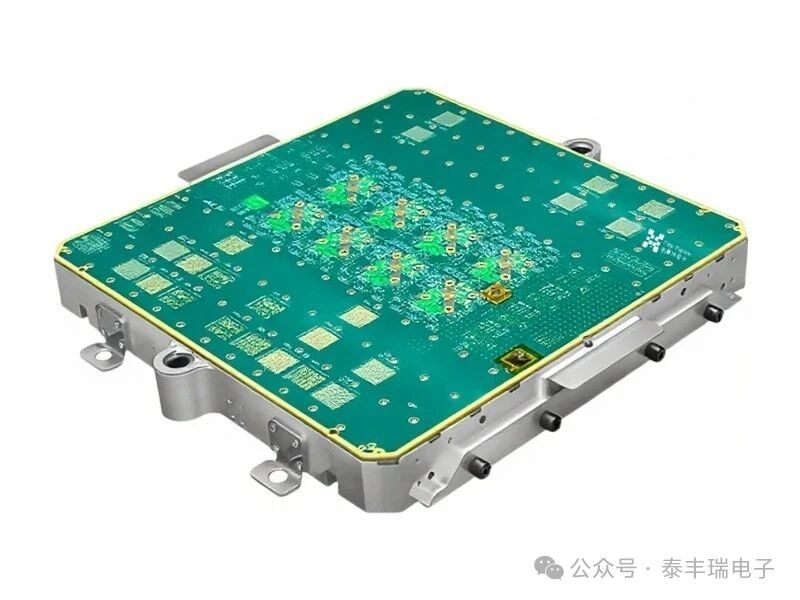

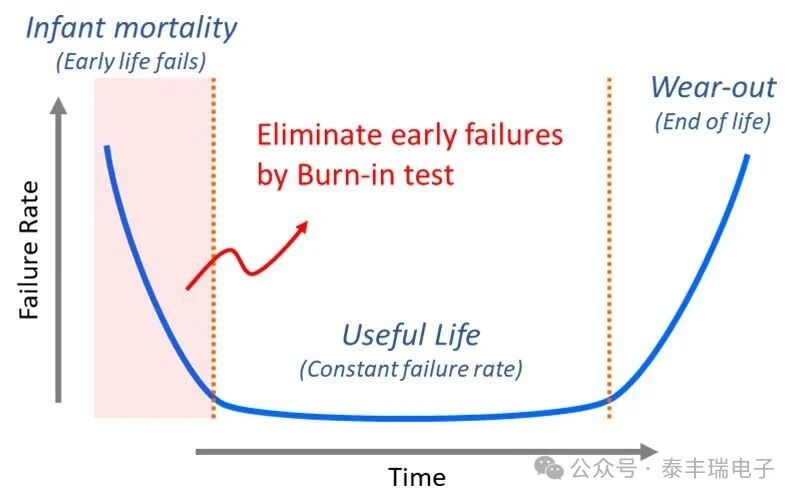

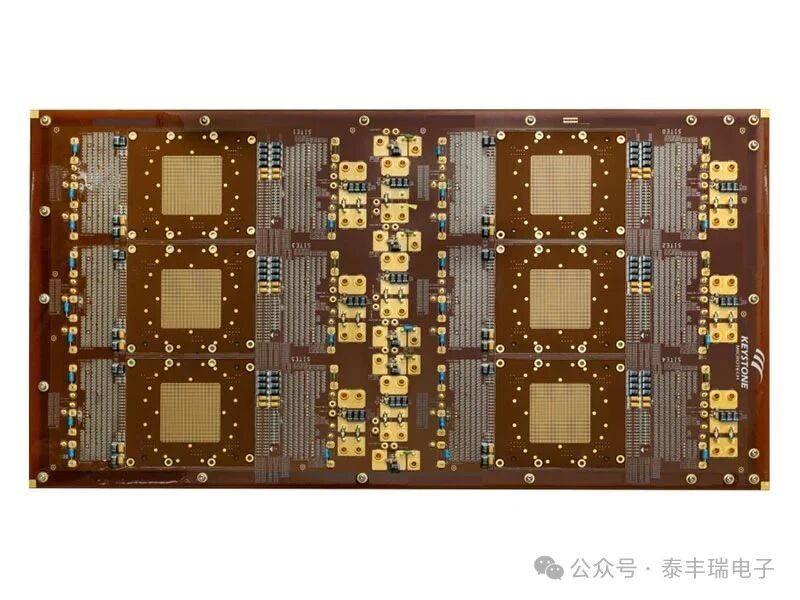

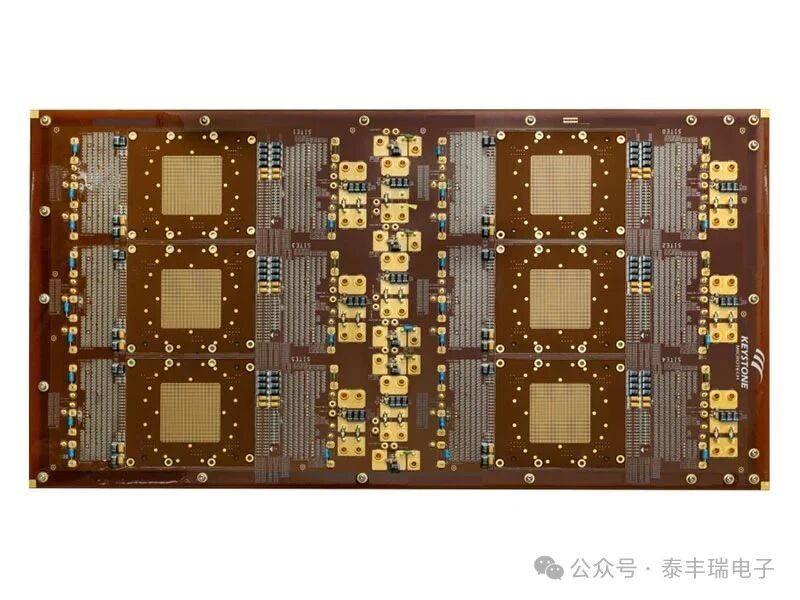

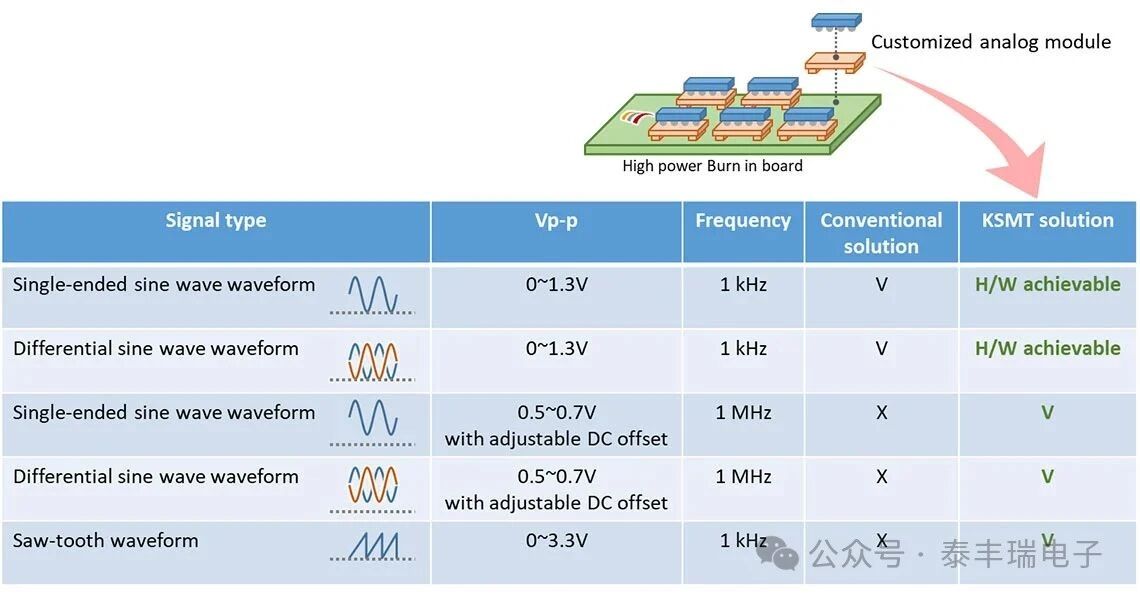

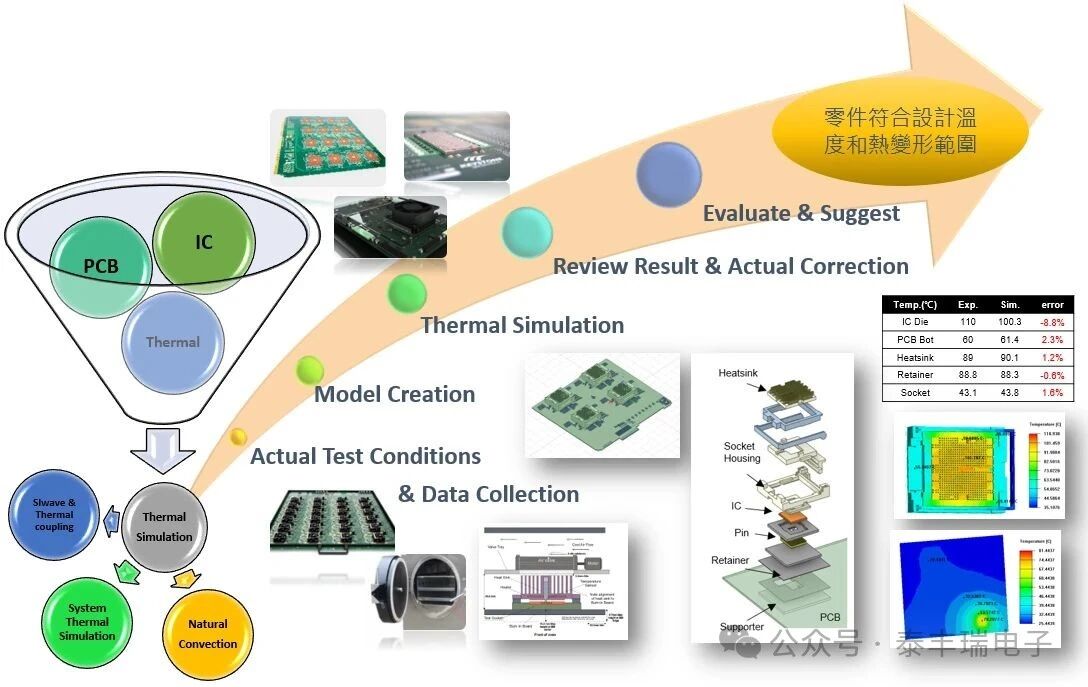

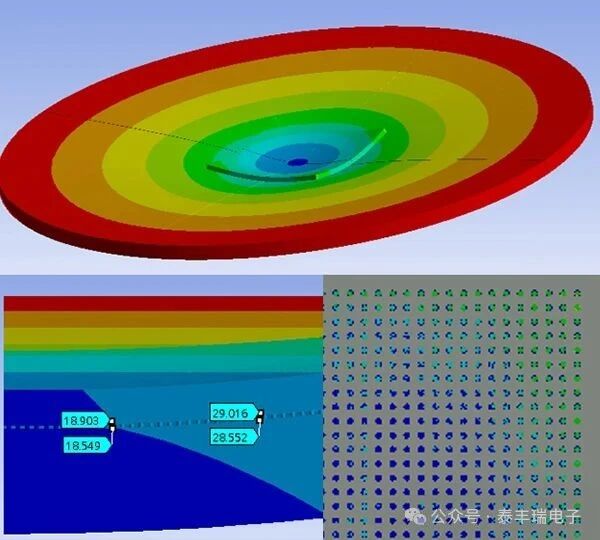

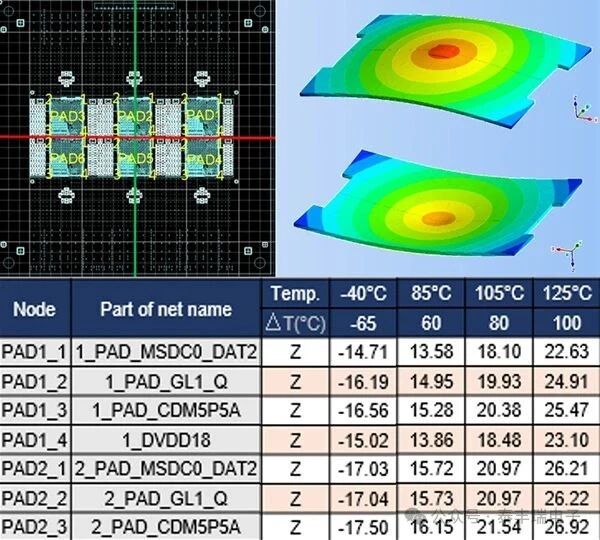

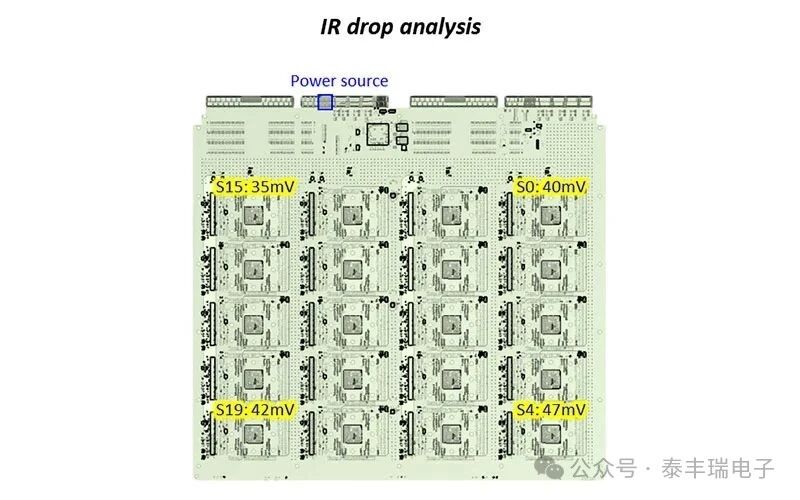

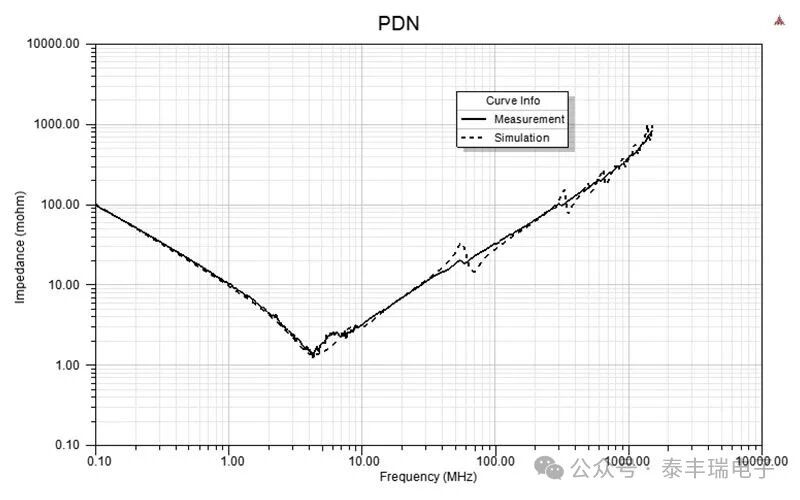

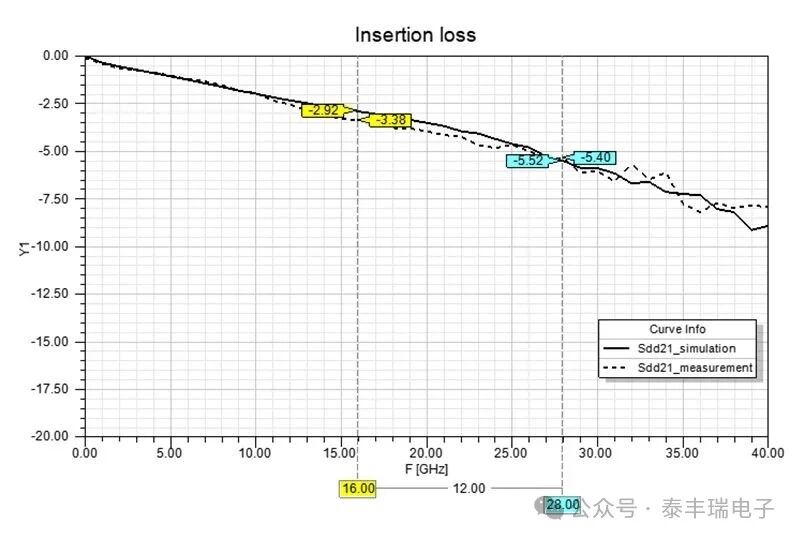

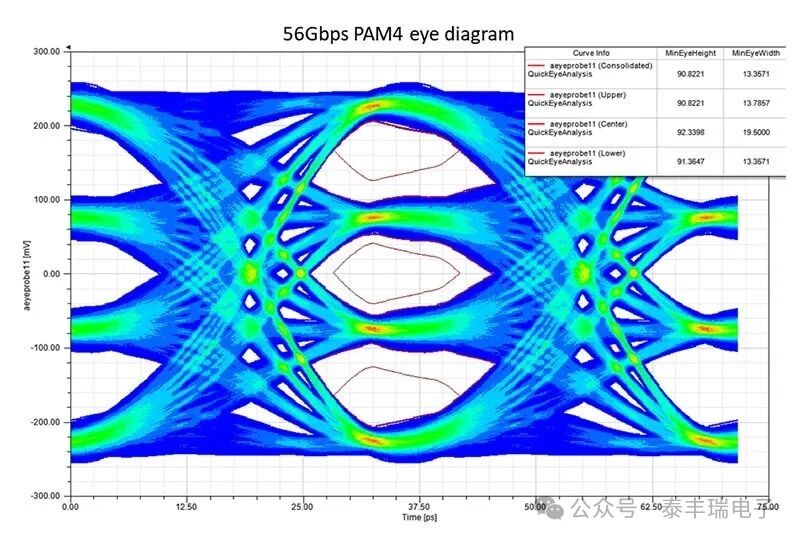

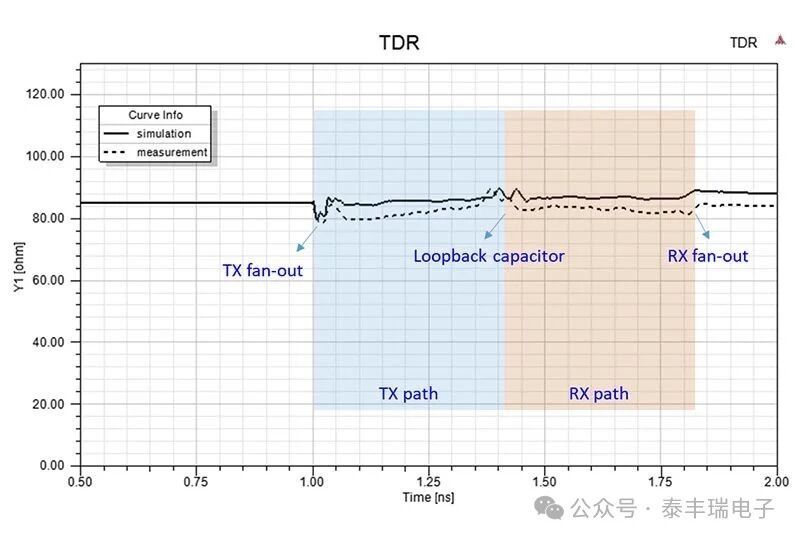

芯片制造后端测试解决方案半导体有两大测试,一般分为 2 个阶段:CP(芯片探测或电路探测)和 FT(最终测试),旨在测试封装的 IC。IC 封装后,需要进行另一轮检查,以控制芯片的良率和质量,以确保芯片的功能和速度符合设计要求。这也是分拣不合格芯片以节省后期生产成本的阶段.  ATE Semiconductor Test Socket Socket  1.产品说明 用于BGA/LGA/QFN/DFN/QFP/PGA/CMOS 图像传感器封装等的解决方案。 提供 2 (TP + BP) 至 4 (GP + TP + FP + BP) 片式插座设计。 适用于工程/SLT/ATE 测试。 2.规格 最小间距为 0.25 毫米及以上。 最多可提供 5000 引脚数。 插座工作温度为 -50°C 至 200°C。 ATE/SLT Socket 封装类型 LGA/BGA 间距:1.0 毫米 引脚数 4077 特性:高引脚数。用于高功率 SLT  封装类型 QFN 间距:0.35 毫米 引脚数 105 特性:标准 2(TP + BP)个插座设计  封装类型 QFP 间距:0.4 毫米 引脚数 120 特性:QFP 标准 4 (GP+FP +TP+BP) 件设计  封装类型 BGA/LGA 间距:0.8 毫米 引脚数 787 特性:带浮动板。工程/ATE 测试  封装类型 BGA/LGA 间距:0.35 毫米 引脚数 1609 特性 用于Handler/ATE 测试  封装类型 WLBGA 间距:0.4 毫米 引脚数 16 特性 适用于 Min SQ1.69mm 封装。工程测试  封装类型 LGA/BGA 间距:0.5 毫米 引脚数 86 特性:带浮动板工程测试  封装类型 BGA 间距:1.0 毫米 引脚数 4344 特性:高引脚数用于高功率 SLT  封装类型 BGA 间距:0.4 毫米 引脚数 22 测试高度:1.90 毫米 特性:高带宽插座。4 个Socket 设计,无屏蔽技术。用于传感器设备测试  ATE TEST Socket   ATE Semiconductor Test Load bord 负载板  3.负载板 Load Board 是一块高度定制的PCB,作为IC 与自动测试设备ATE(Automatic Test Equipment)之间的传输媒介。 随着集成电路设计日渐复杂,在测试及验证IC所花费的工夫也越来越多,对于Load Board 的设计及质量要求也日益渐高。 泰丰瑞电子在测试载板的设计上,利用信号完整性SI(Signal Integrity)、电源完整性PI(Power Integrity)的模拟,来优化及改善测试载板的设计。 针对客户不同的需求模拟数据来调整测试载板Layout,以满足客户的标准。 雍智科技在提供设计载板领域深耕数十年,对于不同自动测试设备(ATE)的平台有相当多的经验,并且也针对不同的测试平台建立了数据库(Data Base)、设计的准则(Guide Line),来增加客户新产品导入NPI (New Product Introduction)以及缩短设计的时间 4.System Level Test 系统级测试载板(SLT) 半导体制程节点的演进加上现今芯片为堆叠算力、增强运算速度,驱使芯片的设计越趋复杂,晶体管密度大幅提升,对于如何抓出缺陷、管控良率,以及避免交出不良品到客户手上成为现今芯片设计公司的重点。 为此,以更全面、系统级的方式去验证芯片的设计成为业界测试芯片的一种方式。 系统级测试能模拟实际终端应用的场景,透过运行程序来检验芯片的良率,此方式亦能补足以往CP、FT测试覆盖率(Coverage Rate)不足的问题。 为满足客户的需求,开始便与客户着手进行SLT 载板的研究及开发,具有丰富的量产经验。  5.可靠度测试(Reliability Test)目的 以质量的角度,电子零件在生产之初尚不成熟时,得经过 “Burn In” 的步骤让一些瑕疵的电子产品提早筛出,并以统计数据来看,可得到浴缸曲线(Bath-Tube Curve),也就是说在使用初期及末期会有较多的电子零件不良,但使用一段时间后电子零件的不良率就会稳定下来。 此目的是为了筛选出在产品开发初期,因为制程不良,设计缺陷等因素,造成产品有潜在性失效或故障的风险,经由此项测试来筛选,避免顾客在使用中造成故障失效。  而BIB (Burn In Board)就是作为半导体IC产品载具,将欲测试之IC透过SOCKET或是直接将IC mount方式与BIB连结,放入测试机台(Oven)内进行不同温度、电压、信号等等之条件反复测试(HTOL, LTOL,HAST & THB等... ) 求取出Bathtub Curve 浴缸曲线,以筛选出前、后期不良产品。 6.定制老化板Burn In Board公板和专版设计 Burn In Board – HTOL ( High Temperature Operation Life )HTOL主要是模拟产品在高温的环境下,连续通电(加入电压或是电流)的寿命试验,以检测产品本身功能性与特性是否会因环境条件而有所改变,以评估IC产品的长时间的作寿命。   7.Burn In Board - HAST ( High Accelerated Stress Test ) 模拟当产品在极高的温度湿气下,将加速水气透过外部保护材料与金属导线间介面渗透至内部,以评估IC构装,抵抗湿气能力。 HAST   Burn In Board-Socket Card 8.外供电路 根据客户需求(H/W或测试机硬件限制)设计额外的应用电路>>成本降低,增加硬件/机台利用率。  9.热模拟分析流程 由热模拟进行从零件到系统级结构和机械性能的分析,实现在复杂的系统中或实验条件中的热分析,有效率的提升散热性能。  1.热模拟分析项目  2.热模拟分析  10.电源完整性(Power Integrity) 1.稳定供电:电源完整性关注于电源系统的稳定性,确保芯片、封装和整个系统得到稳定而干净的电源供应。 这对于防止电压噪声、电流波动等问题至关重要。 2.降低功耗损耗:良好的电源完整性有助于降低功耗损耗,确保电能有效供应到各个组件,提高整体系统的效率。   ATE TEST 11.信号完整性(Signal Integrity) 1.信号传输质量:信号完整性关注信号在电路板、连接器、传输线等传输媒介中的传播质量。 良好的信号完整性确保信号以预期的方式传输,减少信号失真和时序问题,从而提高数据传输的质量。 2.抗干扰能力:信号完整性也涉及到抗干扰能力,包括对串音(crosstalk)的抵抗力。 这对于保持信号稳定性和防止不必要的干扰影响非常关键。 3.传输匹配: PCB 上传输线的阻抗匹配特性对于信号完整性至关重要。阻抗匹配不当或中断效果会导致信号反射或耗散,进而影响整个系统的性能。    |