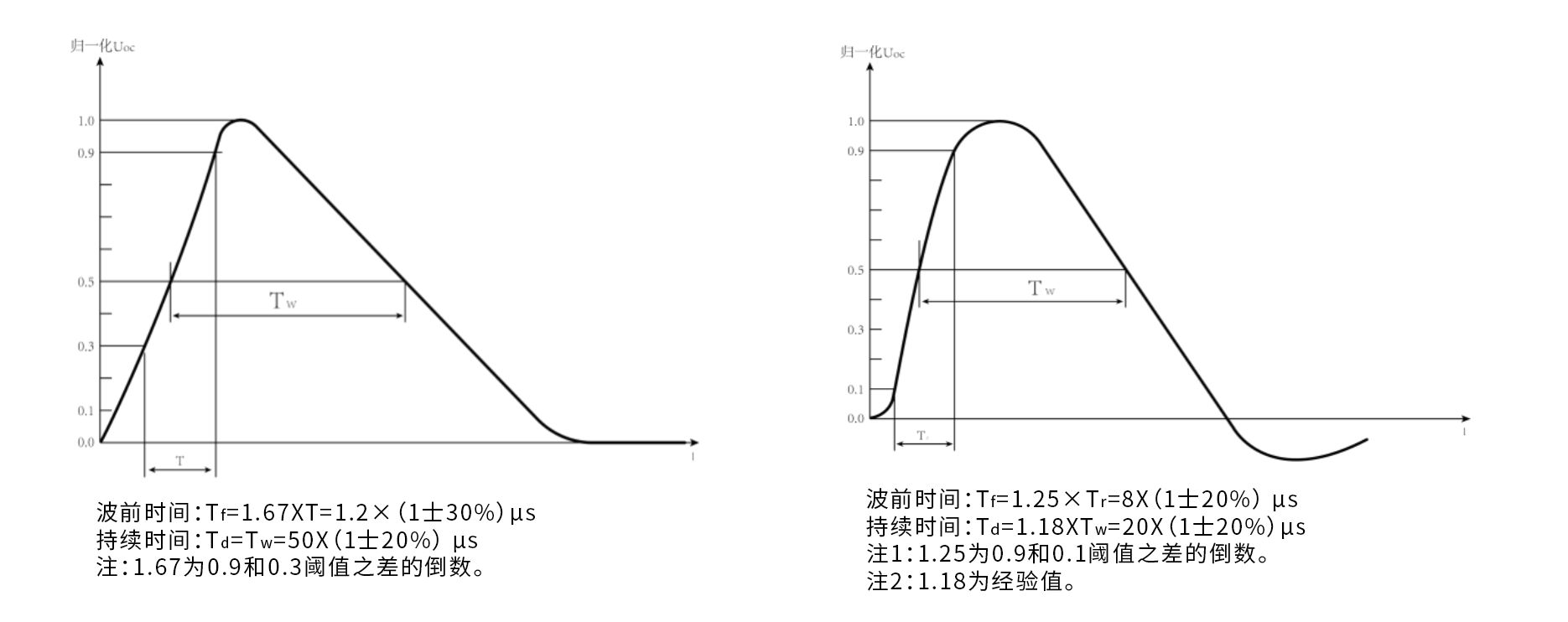

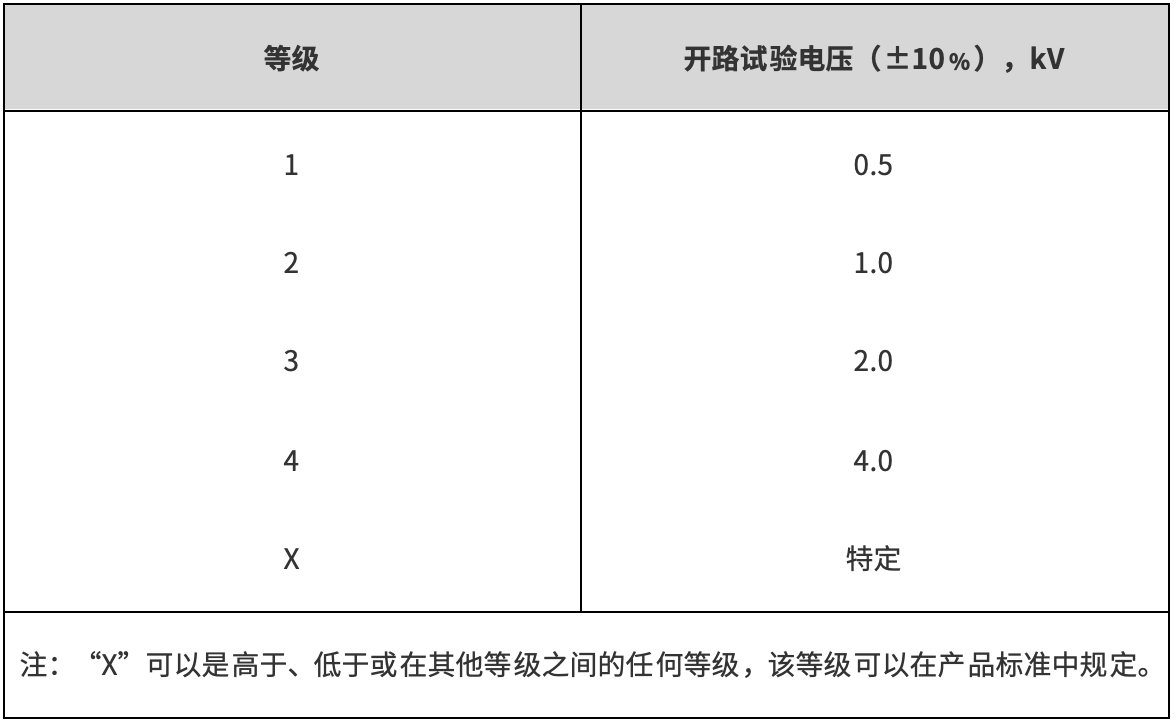

一文详解雷击浪涌测试雷击浪涌试验,又称为瞬态过电压测试或雷电冲击测试,是模拟设备在正常工作过程中可能遭受的雷电或其他瞬态过电压冲击,以评估设备对此类冲击的耐受能力。 其目的在于确保设备在遭遇恶劣电磁环境时仍能保持正常运行,保障系统安全稳定。浪涌试验的重要性不言而喻,尤其在电子、通信、电力系统等领域,其测试结果直接关系到设备的安全性和可靠性。 芯片浪涌测试,通常指的是“系统级ESD”“电气过应力”测试的一种,主要模拟的是在真实应用场景中,当外部有大的瞬态干扰(如雷击、大功率设备开关)通过电源线、通信线缆耦合到系统内部时,芯片引脚需要承受的高压、大电流应力的能力。  测试特点 浪涌测试这与我们常见的“人体模型ESD”有很大区别: HBM 模拟人体带电触摸芯片,特点是高压(kV级)、低能量、瞬时(纳秒级)。 浪涌 模拟系统级干扰,特点是“高能量”(焦耳级)、持续时间长(微秒级),对芯片的破坏力远大于HBM。 测试目的 评估可靠性 检验芯片在恶劣电磁环境下的生存能力,是衡量其robustness的关键指标。 定义安全操作区 确定芯片各个引脚(尤其是电源和I/O口)能够承受的最大浪涌应力水平,为系统电路设计(如保护器件的选型)提供依据。 避免现场失效 通过严格的芯片级筛选,可以极大降低整机设备因雷击、感应开关等事件导致的故障率,提升产品口碑和寿命。 满足行业标准 通信、汽车、工业控制等领域对芯片的抗浪涌能力有强制性标准要求。 测试标准 IEC 61000-4-5 这是最著名的系统级电磁兼容标准,定义了浪涌波形(1.2/50μs 开路电压波,8/20μs 短路电流波)和测试方法。 虽然主要针对整机设备,但其波形和测试理念被广泛借鉴到芯片级评估中。 测试波形与等级 芯片浪涌测试的核心波形是1.2/50μs (电压波) 和 8/20μs (电流波) 的组合波。 1.2/50μs 电压从峰值10%上升到90%的时间为1.2μs,下降到50%的时间为50μs。 8/20μs 电流从峰值10%上升到90%的时间为8μs,下降到50%的时间为20μs。 测试等级通常以电压峰值(如 0.5kV, 1kV, 2kV, 4kV)和源阻抗(如 2Ω, 12Ω, 42Ω)来定义。源阻抗越低,意味着在相同电压下能提供的电流越大,对芯片的考验越严峻。  开路电压标准波形 短路电流标准波形  浪涌抗扰度试验等级 芯片设计中的浪涌防护措施 为了通过浪涌测试,芯片设计阶段必须集成有效的片上防护电路: 大尺寸ESD保护器件 使用基于二极管、GGNMOS、SCR等结构的大尺寸保护器件,能够泄放高达数十安培的瞬态电流。 电源钳位电路 在VDD和VSS之间设计一个在正常工作时高阻、在浪涌来临时迅速变为低阻的电路,为电流提供一条低阻抗的泄放路径。 RC触发电路 用于控制保护器件的开启速度,确保其能及时响应微秒级的浪涌脉冲。 布局优化 使用宽而短的电源环和地环,减少寄生电阻,确保浪涌电流能均匀分布,避免局部热点。 需要强调的是,完全依靠芯片自身的防护来应对高等级浪涌是不经济且困难的。 一个稳健的系统设计是“分级防护”的理念: 第一级:在设备入口处(如电源接口、通信接口)使用气体放电管、压敏电阻、TVS二极管等粗保护器件,吸收绝大部分能量。 第二级:使用磁珠、电感、电阻等进行退耦和限流。 第三级:芯片自身的片上防护电路作为最后一道防线,处理残存的应力。 芯片浪涌测试的目的,就是确保当系统前级防护未能完全奏效时,核心芯片依然能够“扛住一击”,保证系统不出现永久性损坏。 芯片浪涌测试是连接芯片设计与系统应用可靠性的关键桥梁。 它不再是仅仅关心静电,而是直面真实世界中高能量瞬态干扰的挑战。 通过标准化的测试、精准的失效分析和精心的防护设计,可以显著提升芯片在恶劣电磁环境下的稳健性,最终为整个电子设备的稳定运行奠定坚实的基础。 CTI华测检测为满足驱动芯片客户产品开发及异常分析等需求,建置COF/COG/SWAP制程技术服务,提供高效、专业技术、垂直整合的一站式驱动芯片验证分析需求方案。 |