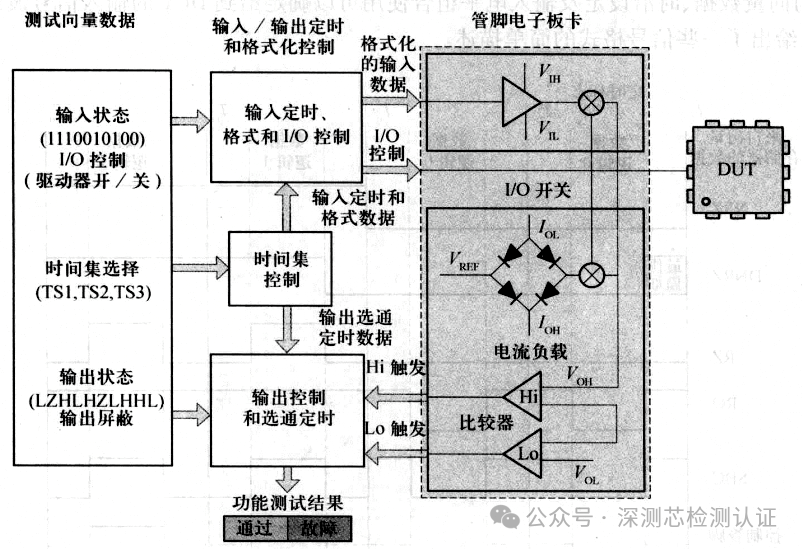

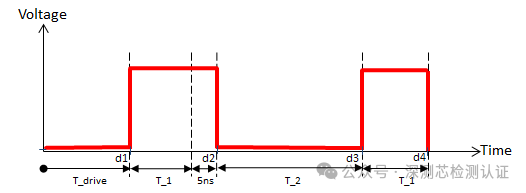

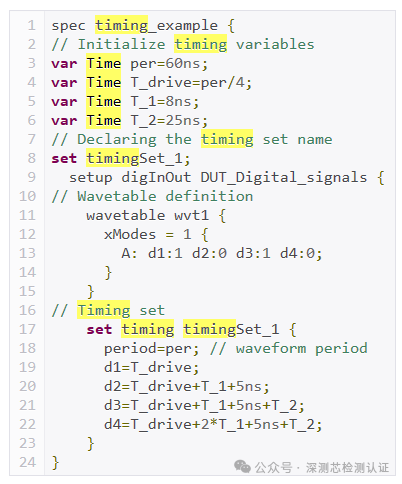

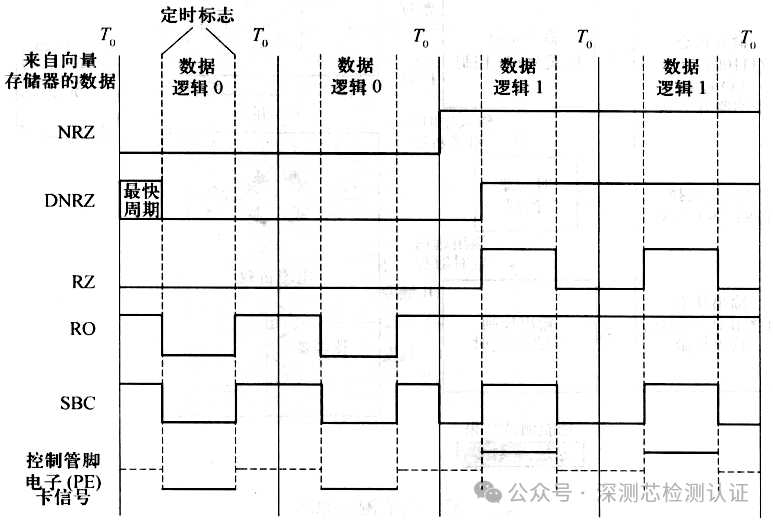

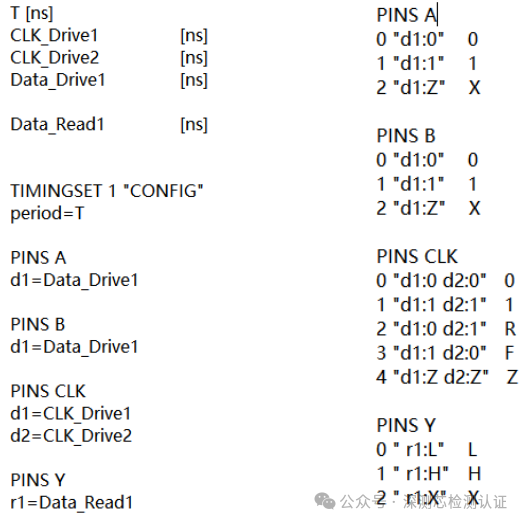

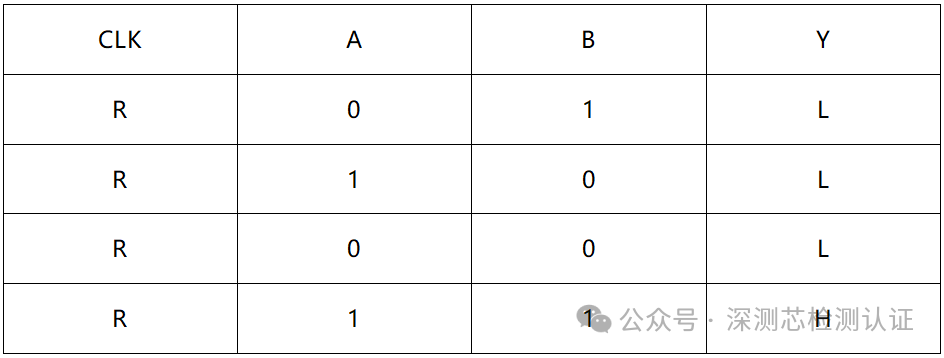

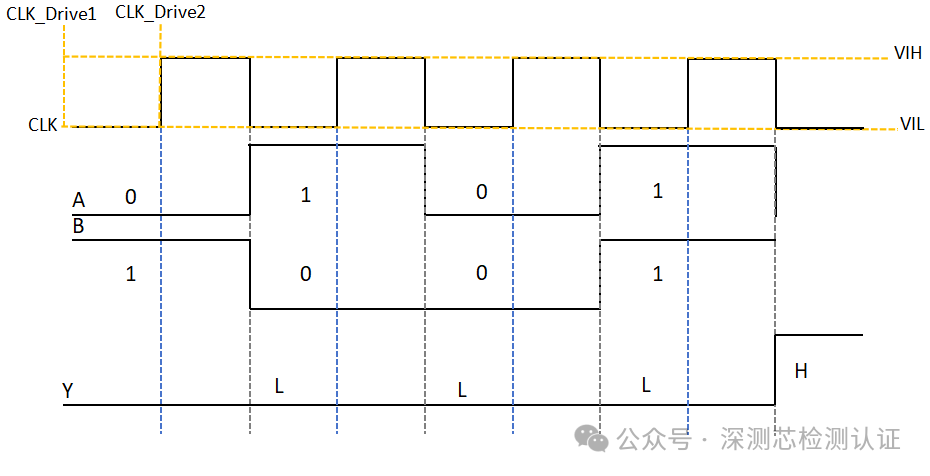

测试概功能测试用于验证IC是否能完成设计所预期的工作或功能。功能测试的基本过程是应用一有序或随机组合的测试图形,以电路规定的速率作用于被测器件,并通过观察被测器件输出与预期数据图形是否相符,以此判别电路功能是否正常。 功能测试核心是测试向量和测试时序。测试向量文件包含待测器件的输入输出逻辑状态,测试时序包含控制测试硬件产生的波形、频率、周期等。如下图为功能测试原理图:  二、功能测试参数定义 1、测试周期:在功能测试中,测试周期表示每单元测试向量所持续的时间,等于输入时钟的频率的倒数。 2、测试向量数据:测试向量表示输入和输出逻辑状态,输入和输出数据通常由以下一组字符组成: 0——驱动输入低电平(逻辑0) 1——驱动输入高电平(逻辑1) L——输出比较低电平 H——输出比较高电平 Z——输出高阻态比较电平 X——不关心状态(忽略电平) 测试向量如下图所示:  3、输入信号电平(VIH\VIL):VIH代表逻辑1的电平值,VIL代表逻辑0的电平值。 4、输入信号时序(drive):波形表中定义的波形的定时设置被指定为一组定时方程,或简称为“定时集”。在时序集合中,时序方程定义了驱动边发生的时间点,这定义了输入波形的确切形状。 Eg.在下面的波形中,定义了四个驱动沿,并定义了四个驱动沿发生的时间点及逻辑电平,其中d1=T_drive=15ns表示波形在第15ns时发生第一个驱动,驱动电平为逻辑1电平;d2=T_drive+T_1+5ns=28ns表示波形在第28ns时发生第二个驱动,驱动电平为逻辑0电平,依次类推。   5、采样时序( receive):周期内何时对输出进行采样 6、期望逻辑电平(VOH\VOL):VOH表示期望的逻辑高电平,VOL表示期望的逻辑低电平 三、码型格式 在ATE中,将输入激励和预期输出响应结合起来形成ATE的测试图形,这些图形在ATE中是通过系统时钟上升和下降沿、器件管脚对建立时间和保持时间的要求和一定的格式化方式来表示的。格式化方式一般有NRZ(非归零)、NRZI(非归零反)、DNRZ(延迟非归零)、RZ(归零)、RO(归1)、SBC(补码环绕)。  1.NRZ(非归零):不归零不归一,表示存储在矢量存储器中的实际数据,不包含边沿定时。NRZ数据仅在每个周期(TO)开始时更改,即若图形文件存储数据为“1”,那么在相应时钟边沿,波形则变化为“1”。NRZI波形是NRZ波形的反相。 2.DNRZ(延迟非归零)与NRZ一样代表存储于向量存储器的数据,只是周期中的数据的转变点不在T0,而会在预先定义的延时点发生跳变。 3.RZ(归零):在系统时钟的起始时间T0,RZ测试波形保持为“0”,如果在该时钟周期图形存储器输出图形数据为“1”,则在该周期的时钟周期期间,RZ测试波形由“0”变换到“1”,时钟结束时,RZ 测试波形回到“0”。若该时钟周期图形存储器输出图形数据为“0”,则RZ测试波形一直保持为“0”,在时钟信号周期内不再发生变化。归“1”格式(RO)与RZ相反。 4.SBC(反码环绕):也称为异或(XOR)格式,它在一个周期内提供3个跳变沿,即先在T0翻转电平,等待预定的延迟后,显示指定脉冲宽度的实际矢量数据,然后在周期的剩余时间内再次反转数据。 四、测试案例 以一个简单的逻辑器件为例,来说明功能测试内容。时钟控制逻辑与门器件有三个输入端:数据输入(A和B)、时钟输入(CLK);一个输出端(Y)。它有如下功能特征:(1)时钟是数据由输入到输出经过器件进行传输的同步控制信号;(2)输入数据在时钟的上升沿由器件读入;(3)输出数据在时钟的下降沿由器件输出;(4)数据传输仅在时钟有效时进行;(5)输出数据与输入数据逻辑相与。 1、设置控制电平及时序参数 根据器件设计规范,设置该器件电源电压VDD为5.0V,VIH=5.0V,VIL=0V,VOH=2.5V,VOL=2.5V;工作频率=10MHz,设置输入引脚CLK有两个驱动分别为CLK_Drive1、CLK_Drive2,输入引脚A、B有一个驱动沿Data_Drive1,输出引脚Y有一个采样沿Data_Read1,如下图  2、器件真值表  3、时序 (1)NRZ(非归零)码 设置CLK_Drive1=0ns, CLK_Drive2=50ns Data_Drive1=0ns,Data_Read1=90ns  (2)RZ(归零)码 设置CLK_Drive1=0ns, CLK_Drive2=50ns Data_Drive1=10ns,Data_Read1=90ns  |