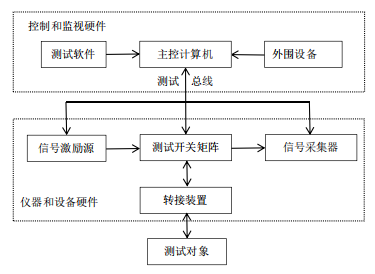

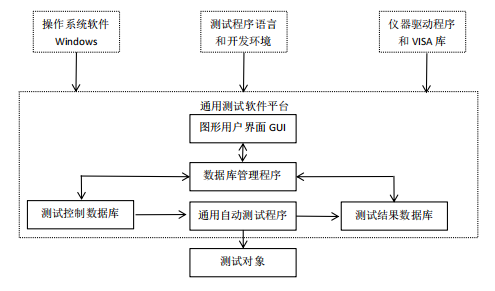

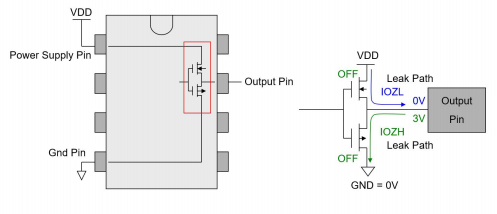

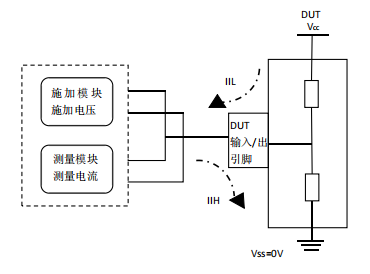

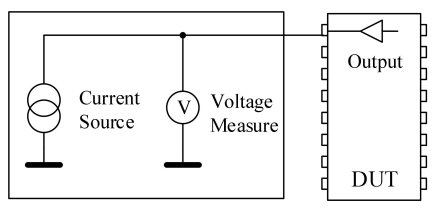

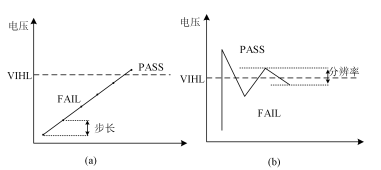

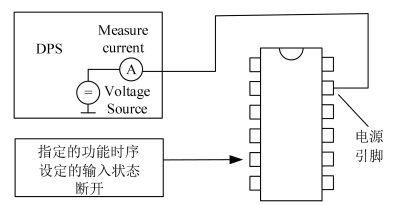

ATS内部结构 数字集成电路直流参数测试原理集成电路测试(一) 01.ATS内部结构 1、第三代自动测试系统的构成 ATS:自动测试系统,表示在计算机控制下,能自动进行量测、处理数据,并以适当方式显示或输出测试结果的系统。在自动测试系统中,整个测试工作都是在测试人员预先编制好的测试程序统一指挥下完成的,系统中的各种仪器和设备是智能化的,都可进行程序控制。目前自动测试系统已升级到第三代,主要由微型计算机、通用硬件系统和软件系统三部分组成。第三代自动测试系统主要体现在自动化用例集(一组能够自动运行的测试用例)的构建,实现了分层的自动化用例体系,将驱动部分、执行部分等单独抽象出来,上层的自动化用例通过调用底层的相关“API”来实现相关的测试用例功能。总的来说,第三代自动测试系统的使用更加灵活、体系结构与接口设计更加开放。 2、通用硬件系统结构 通用硬件系统设计的关键在于 UUT(Unit Under Test)接口的标准化设计,UUT 接口标准化的目的在于提供一种能够在多个 UUT 之间方便转换的硬件连接结构。这种结构通过对机械连接结构、接口插件和连接器的标准化规定提供了可工作于宽频带信号范围内的接口连接方式。开关矩阵(SWM)接口和 ATS 转接装置(RFX)接口是 ATS 的重要组成部分,ATS 仪器和 UUT 是通过 SWM 来连接的,大多数的激励和测量信号是通过 RFX 作用到 UUT 上的。标准 RFX 接口限制了不同类型信号在接收器的不同位置上出现,SWM 可实现多种仪器与由标准RFX 接口所确定的多功能终端的连接。  图 1 通用硬件系统结构图 3、软件系统结构 第三代自动测试系统的软件设计主要根据国际标准IEEE1226 ABBET,IEEE 1226 ABBET 标准是一种软件体系结构规范,使按照该体系结构搭建起来的软件平台之间进行标准化的数据交换和相互操作。由于标准没有定义模块的实现,开发者可以根据需求选择用C/C++或 ATLAS等语言进行测试系统的搭建。  图 2 软件系统结构图 02.数字集成电路测试基本原理 根据器件类型,IC测试可以分为数字电路测试、模拟电路测试、混合信号电路测试、存储器测试、SOC测试等。数字电路测试是IC测试的基础,除少数纯模拟IC如运算放大器、电压比较器、模拟开关等之外,现代电子系统中使用的大部分 IC都包含有数字信号。数字IC测试一般有直流参数测试(DC Test)、交流参数测试(AC Test)和功能测试(Functional Test)。 (1)连接性测试(OPEN/SHORT 测试、Continuity Test 或 OS 测试) ①测试目的 验证被测器件管脚的电气连接是否正常,保证被测器件的管脚正确连接,以及管脚与管脚之间,管脚与地、电源之间没有存在开路、短路的情况,方便生产人员区分芯片缺陷和测试硬件的连接缺陷。连接性测试是后面的功能测试和其它参数测试的基础。 ②测试原理 借助DUT引脚的保护电路完成,保护电路的原理是利用二极管的单项导电性(即允许电流在一个方向上通过,而在另一个方向上阻止电流流动)来实现的,当电路中的电压或电流超过一定值时,二极管会导通,并将电流引导到地线或其它安全区域,从而保护电路中的元件不被过压、过流等不良情况损坏。一般在集成电路设计中,为了保护输入、输出引脚,避免受到 ESD 或其他瞬间过大电压情况导致的损坏,设计人员会在引脚与地之间加入一个保护二极管(下二极管),有些电路也会同时在引脚与电源间加入保护二极管(上二极管)。这些保护二极管在电路正常工作时是反向截止的,不会对电路的正常工作有任何影响。通常在量产测试中,为了减少测试时间,降低测试成本,管脚对电源和对地的测试只做其中的一个。  图 3 连接性测试原理图 ③测试方法(测试管脚到VCC的连接性) Step1: 将所有管脚设为 0V。 Step2: 待测管脚上施加施加正向偏置电流 100uA。 Step3: 测量待测管脚的电压。 Step4: 如果该电压小于 0.2V,说明管脚短路。 Step5: 如果电压大于 0.8V,说明该管脚开路。 Step6: 如果电压在 0.2V 和 0.8V 之间,说明该管脚正常连接。 (2)漏电流测试:(IIH/IIL、IOH/IOL、IOZL/IOZH) ①测试目的 漏电流测试的目的是检测 DUT 的输入负载特性,确保输入阻抗满足设计需求、输入电流不会超标,也是验证和发现 COMS 工艺制程中是否存在问题的好方法。漏电流一般是由于器件内部和输入管脚之间的绝缘氧化膜在生产过程中太薄引起的,形成一种类似于短路的情形,导致电流通过。IIL 指的是输入引脚逻辑为低电平(L)时,允许的最大拉电流(I,source,从外部经引脚往 DUT 的 VSS 漏,如图 1(右)),用来看引脚对电源的漏电流会不会超标,也是看隔离的程度,IIH 指的是输入引脚逻辑为高电平(H)时,允许的最大灌电流(I, sink,从 DUT 的 VDD 经引脚往外漏,如图 1(左)),IOZ:指的是当一个低电平(或高电平)施加在一个处于高阻态(Z)的输出管脚(O)上,管脚上产生的漏电流(I),如图 2,用来看引脚关断时漏电流会不会超标,此参数是确保双向或高阻输出引脚能正常关断(输出高阻态)。输出高低电流(IOH/IOL)的测试原理与之类似,只是在施加的电压大小方面会有所不同。  图 4 IIH/IIL 原理图  图 5 IOZH原理图 ②测试原理 漏电流测试是通过施加电压测电流的方式进行测试的,在 V93000 测试平台中我们主要通过调用 PPMU 进行测试,在管脚端施加规定的直流电压测量流入的电流,对数字输入管脚是在输入阈值 VIH 和 VIL 下分两次检测,比较测得的结果是否符合数据手册定义的范围。如下图分别为漏电流测试的原理图:  图 6 漏电流测试原理图 ③测试方法 Step1:在规定的测试温度下,芯片放入测试平台,将所有 IO 置为输入状态。 Step2:电源电压设置为在 VDDmax。 Step3:根据 datasheet 对 IO 脚施加规定的电压。 Step4:根据 datasheet 设定 limit,超过 limit 表示灌进/ 流出 DUT 的电流超标。 (3)输出高低电平测试(VOH/VOL) ①测试目的 VOH/VOL 测试目的是检测待测器件输出端在指定的电源电压和输入电平条件下,输出端口的电流驱动能力,同时也反应了输出端的阻抗是否符合要求。VOH 是指在器件的输出管脚为逻辑 1 并且负载电流为 IOH 时的电压值,VOL 是指 在器件的输出管脚为逻辑 0 并且负载电流为 IOL 。 ②测试原理 VOH/VOL 的测试需要相应的初始化向量(Pattern),把要测试的输出管脚配置到指定的电平,然后用 PPMU 加电流测电压,再根据测量的实际值和限定值确定器件该参数失效与否。  图 7 VOH/VOL 测试原理图 ③测试方法 Step1:运行功能测试期间,输出端灌入或拉出适当的 IOL/IOH 电流。 Step2:输出比较电路确定输出端是否仍能保持相应的 VOL/VOH 电平。 Step3:根据 datasheet 设定 limit,超过 limit 测试结果为 fail。 (4)输入高低电平测试(VIH\VIL) ①测试目的 输入高低电平参数是衡量芯片输入管脚逻辑输入的极限值状态。VIH 是器件输入管脚从低到高状态时所需的最小电压值,VIL 是器件输入管脚从高到低状态时所需的最大电压值。输入高电平 VIH 越小,输入低电平 VIL 值越大,电路的输入抗干扰能力越强。 ②测试原理 针对 VIHL 的测试,主要有基于搜值法的二分法和线性扫描法、基于极限值的功能测试法。下图为基于搜值方式的二分法和线性扫描法,通过运行功能码的方式,寻找功能失效时的临界变量值,来测试 VIHL 参数值。  图 8 基于搜值方式的二分法和线性扫描法 下图为基于极限值的功能测试法,通过运行功能码的方式,判定数据手册的 VIHL 指标是否达到设计规格的要求。  图 9 基于极限值的功能测试法 ③测试方法(基于极限值的功能测试法) Step1:电源引脚设置 VDDmax。 Step2:设置 VIL 和 VIH 到极限值(使输入电压符合逻辑“0”的最大电压 VIL,使输入电压符合逻辑“1”的最小电压为 VIH)。 Step3:执行相应的功能测试码。 Step4:通过功能测试码是否 pass 来判断 VIL 和 VIH 是否符合要求。 (5)电源电流测试 ①测试目的 电源电流测试主要分为静态电源电流测试(IDDQ 测试)和动态电源电流测试(ICC/IDD 测试)。静态电流测试目的是在确保待测器件处于低功耗状态下电 源电流符合测试规范。在实际测试时,可以按照测试规范要求通过运行测试向量的方法将待测电路运行到指定状态,测试电源引脚的电流大小。动态电流测试目的在于检测待测电路实际工作时的电流大小,实际测试时会将待测电路在指定的功能状态下进行运行并检测电源电流大小情况。当为静态时阻抗较大因而测到的电流较小,为动态时阻抗较小,测得的电流较大。IDD 表示的是 CMOS 电路中从漏极(D)到漏极(D)的电流(I), 如果是 TTL 电路则称为 ICC(从集电极到集电极的电流)。Gross IDD 指的是流入 VDD 管脚的总电流(在 Wafer Probe 或成品阶段都可测试)。IDD 是看芯片总电流会不会超标,一般要看最低功耗和最大工频下的电流。一般先进行电源引脚的短路测试,再进行静态和动态功耗测试,通常这个测试紧接 OS 测试,是 DUT 通电后的第一个测试。 ②测试原理 将所有输入引脚设低 / 高电平,通常 VIL 设置为 0V、VIH 设置为 VDD,所有输出引脚空载(防止悬空产生漏电流,使 IDD 变大),测试时,通常需要在上电与采样之间加延时,让寄生电容充满电,避免造成干扰。需要注意的是:需要设置的是电流钳,防止电流过大损坏测试设备。  图 10 电源电流测试原理图 ③测试方法 电源引脚的短路测试: Step1:给 VDD 上最高电压,并且 tester 的电压源设定一个钳制电流。 Step2:所有的输入 pin 置高,所有的输出 pin 置0,等待5~10ms。Step3:量测流过 VDD 上的电流,正向或者反向电流过高都说明电源到地短路了。 静态功耗测试: Step1:给 VDD 上最高电压,并且 tester 的电压源设定一个钳制电流,防止电流过大损测试机。 Step2:跑 pre-condition pattern,把芯片设置到低功耗状态。 等待 5~10ms。 Step3:量测流过 VDD 上的电流,根据 datasheet 设定 limit,超过 limit 即表示该测试项 Fail。 动态功耗测试: Step1:给 VDD 上最高电压,并且 tester 的电压源设定一个钳制电流。Step2:让芯片持续不断的运行特定的 pattern,等待 5~10ms。 Step3:量测流过 VDD 上的电流,根据 datasheet 设定 limit,超过 limit 即表示该测试项Fail。 |