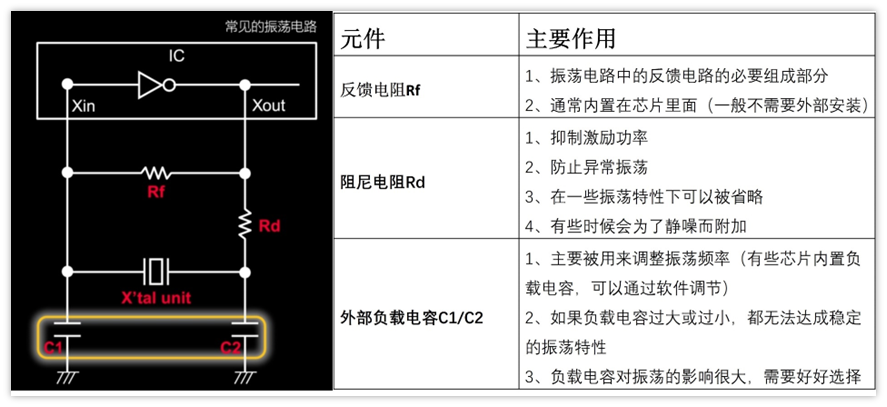

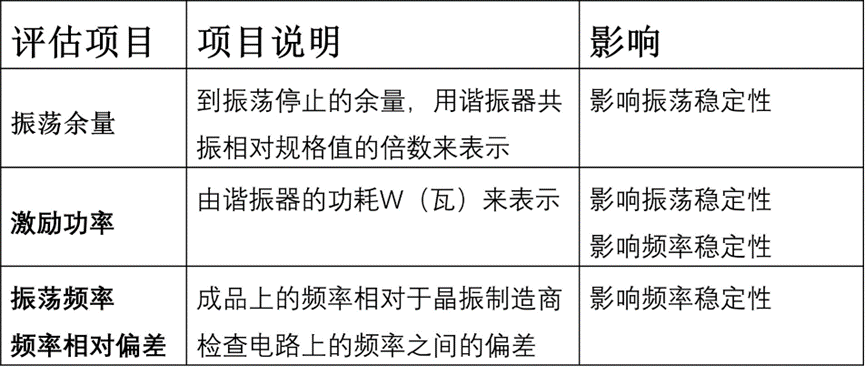

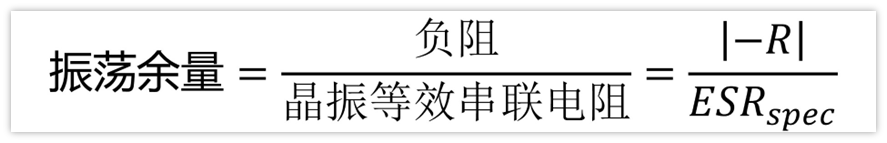

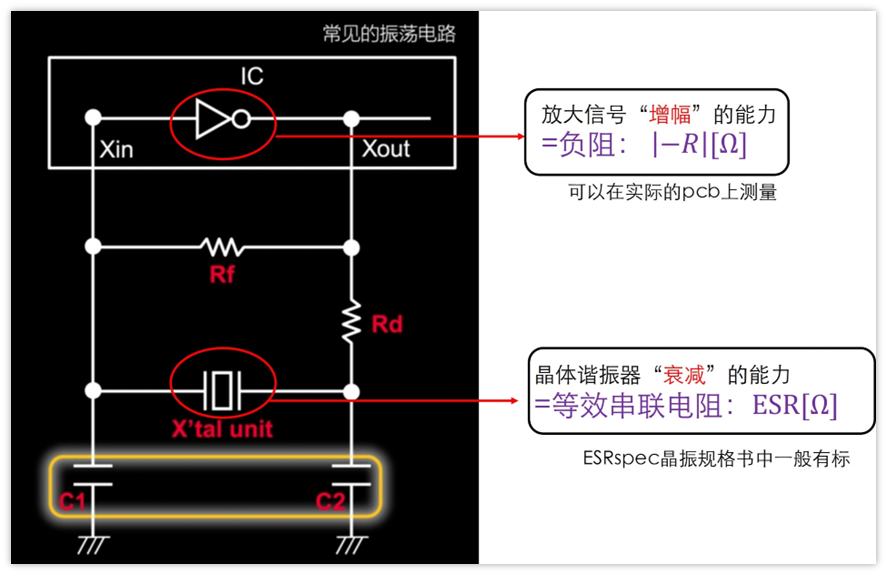

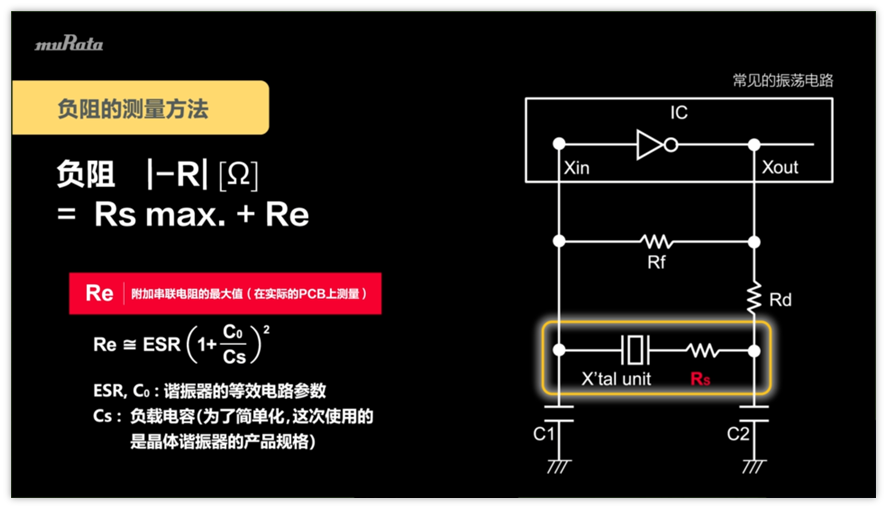

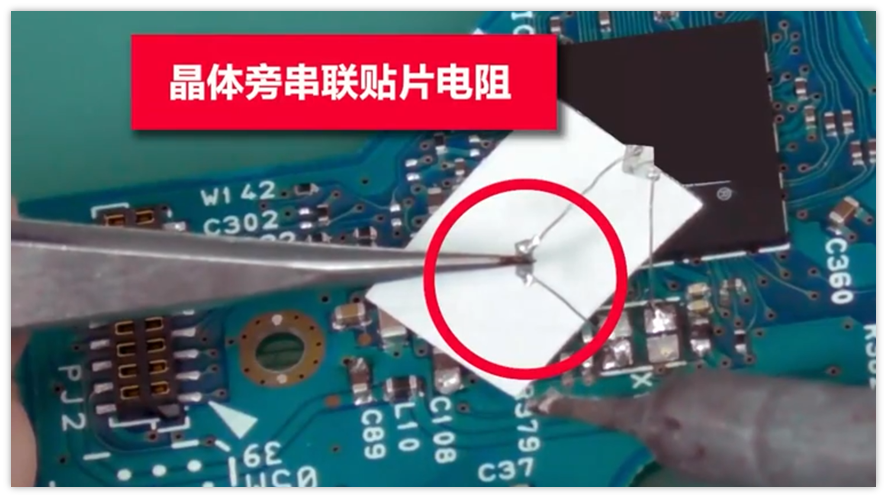

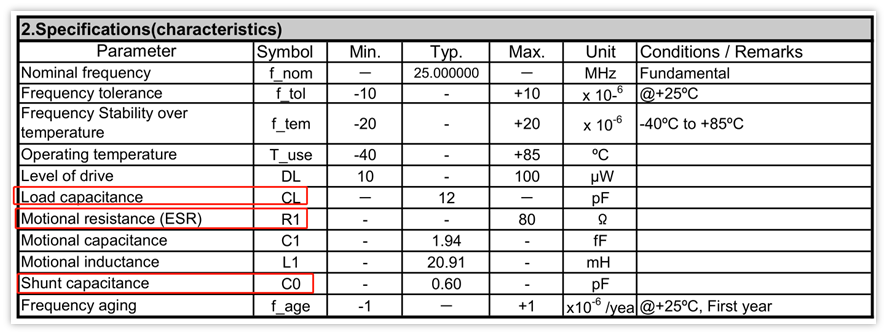

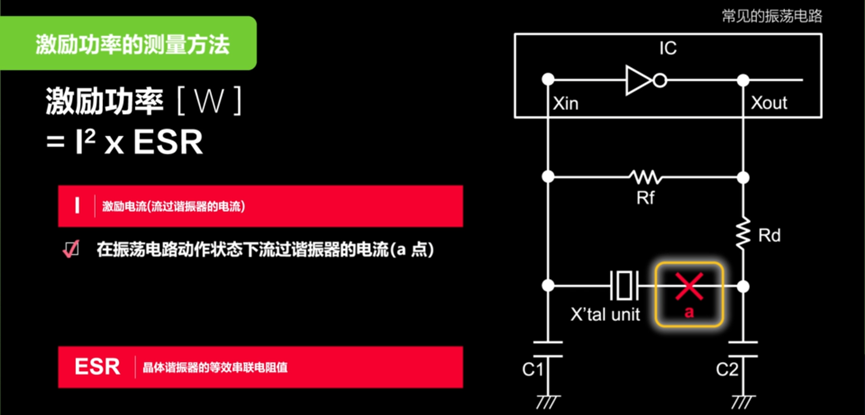

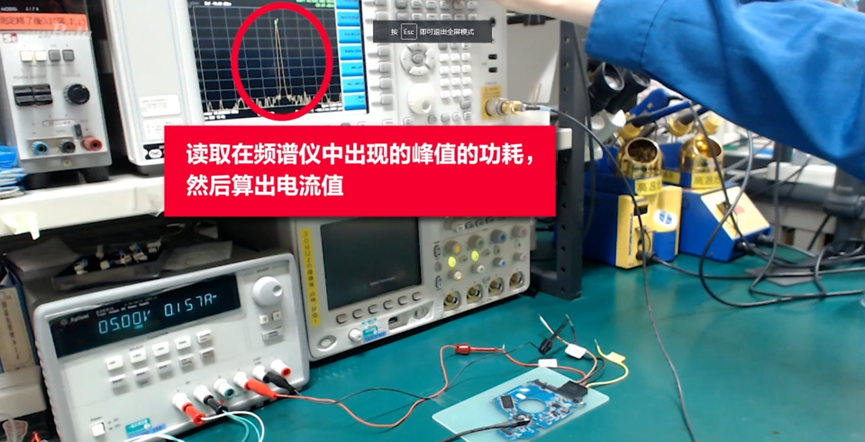

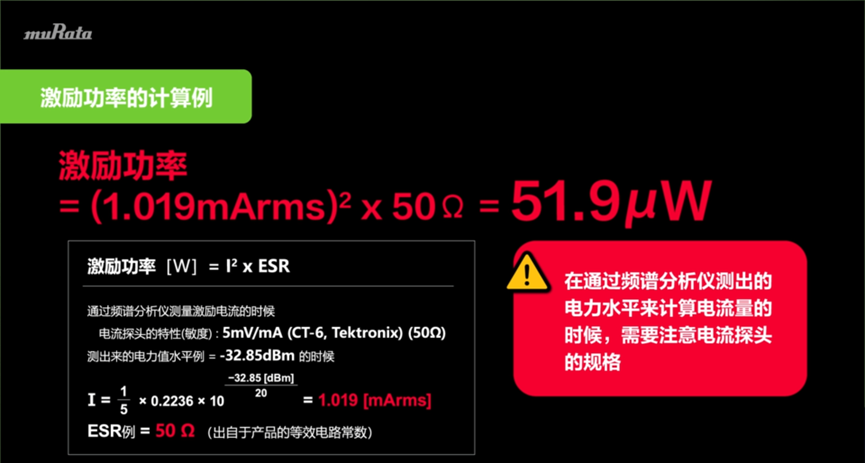

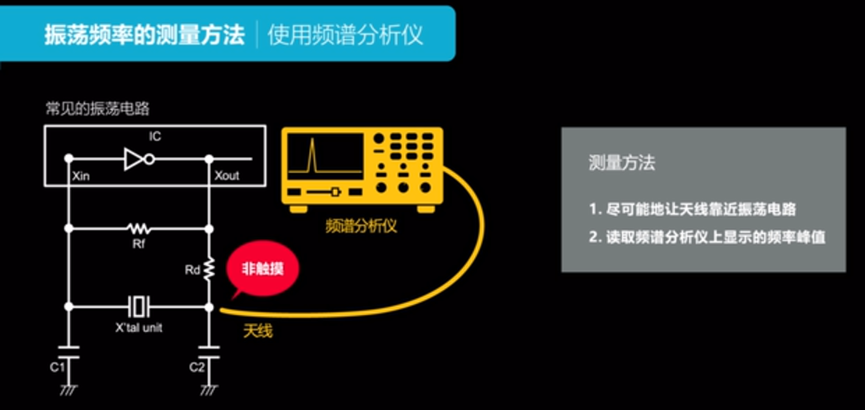

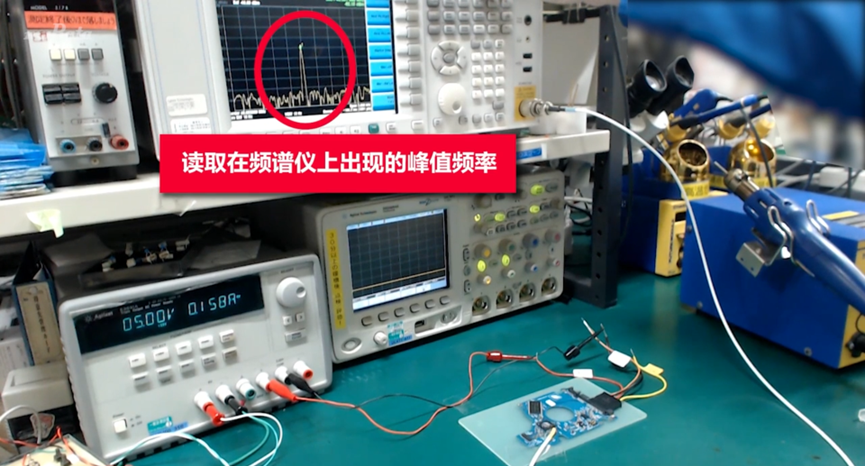

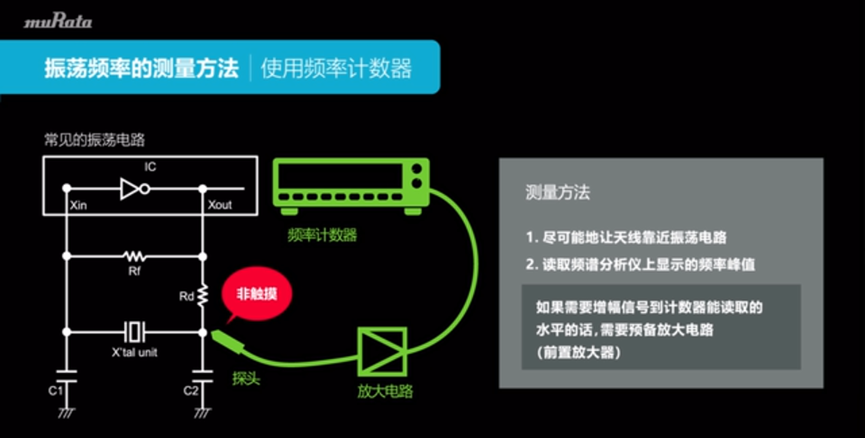

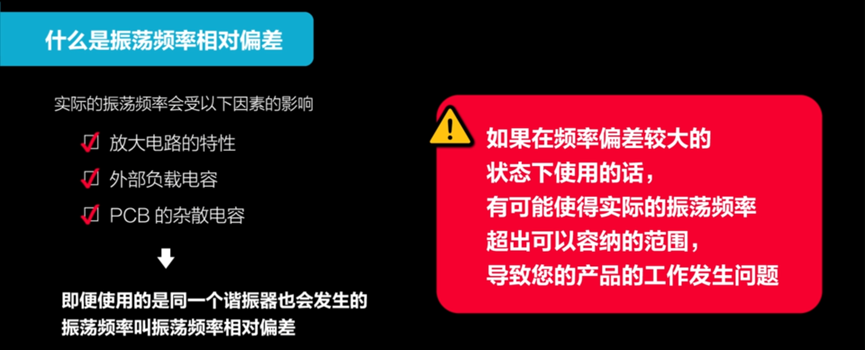

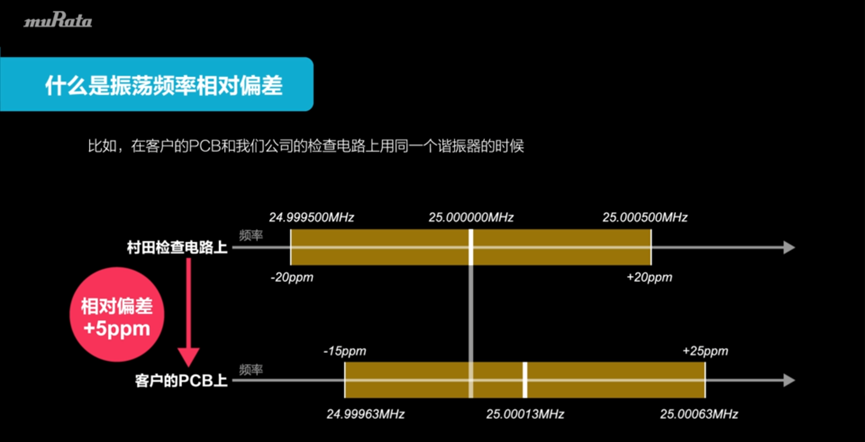

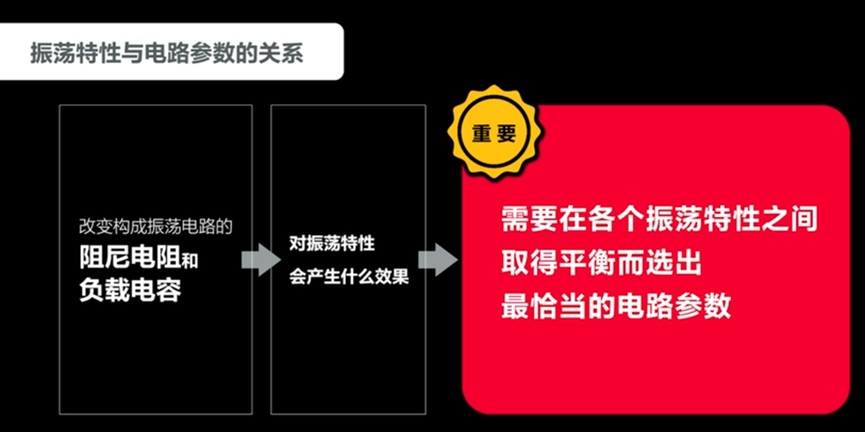

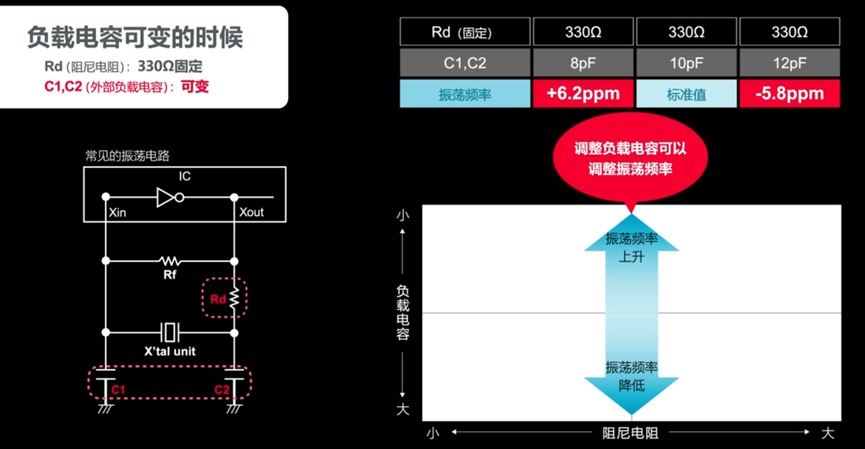

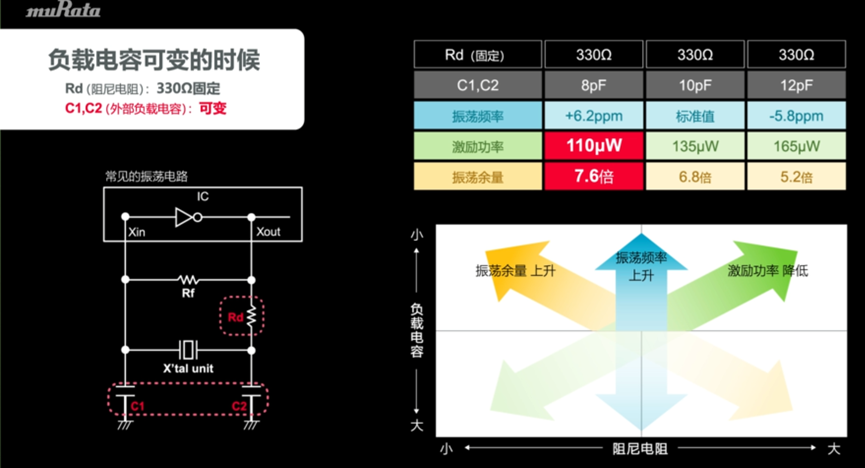

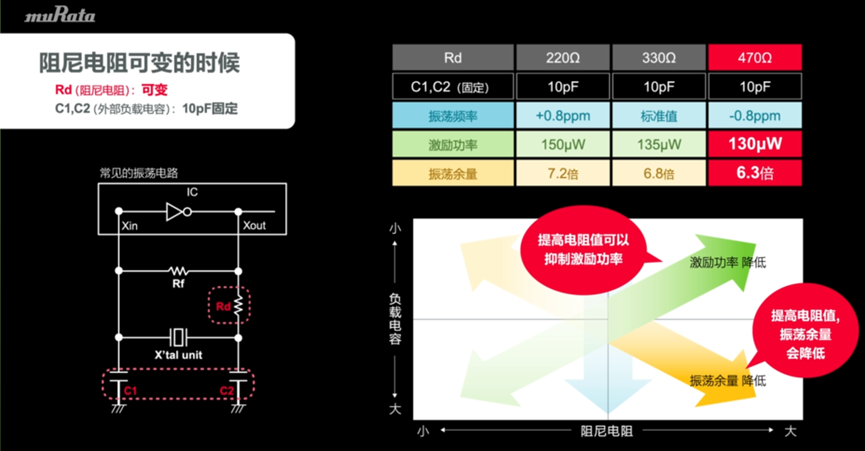

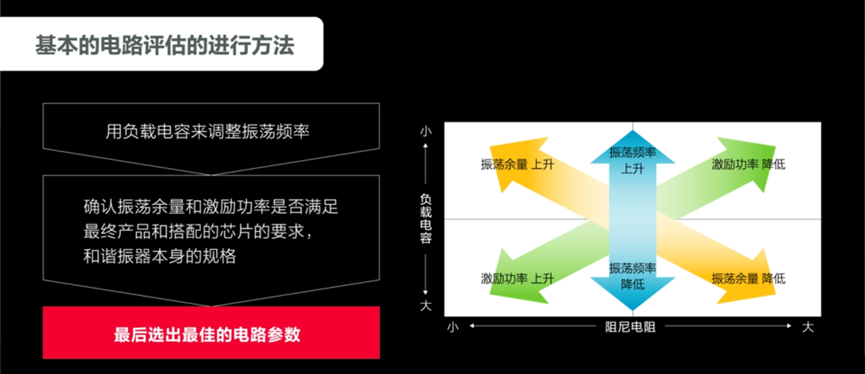

以下文章来源于硬件工程师炼成之路 ,作者炼成之路电路设计好之后,如何测试晶振电路是否满足设计要求呢? 关于晶振的测试,我在某元器件官网上面看到一个比较好的视频,有5节内容,内容简介如下:  视频不长,每节大概3-4分钟,不过该说的也都说了,还有实操部分。 按道理说我告诉兄弟们有这个视频就可以了,可以自己去看,不过我还是把视频的观点作为笔记写下来了。因为我也需要学习,相当于再巩固一遍,加深理解吧。另外一方面,我个人不是喜欢视频,因为视频不好不断暂停,而通常一些观点需要停下来思索一下,结合自己已经知道的知识,两者相互印证。如果不暂停,就像没经过大脑,看完就完了,难以真正变成自己的知识。 下面就来看看我的文字笔记吧。 第1节、电路元件的作用 首先,我们需要评估一个晶振电路到底OK不OK,因为如果设计不合理,就会造成电路工作异常。 异常现象一般有下面两种: 1、晶振电路停振 2、频率偏差过大 电路元件功能再次介绍:  为了选择最佳的电路参数,需要对下面三项内容进行测量评估: 1、振荡余量 2、激励功率 3、振荡频率相对偏差  第2节、振荡余量的测量 什么是振荡余量? 振荡余量是一个倍数,它等于晶体谐振器的负阻除以晶体谐振器的等效串联电阻。理论上,振荡余量有1倍以上就可以起振,但是当振荡余量接近1倍时,偶尔可能发生不振荡的情况。  为了稳定起振,一般要求振荡余量大于5倍。 负阻可以看成是放大器放大信号的放大能力,负阻的大小需要在实际电路中测量得到。负性阻抗不是晶振的内置参数,而是振荡电路的一项重要参数。 而等效串联电阻ESRspec会消耗能量,可以理解为阻碍信号放大的阻力。ESRspc一般在晶振规格书手册中有标注大小。  测量负阻方法:   1、将电阻Rs串联到晶体谐振器上面,逐步增大这个电阻,直到晶振还可以振荡的极限为止,此时的阻值大小为Rsmax。 2、根据晶振手册中的参数计算Re,Re≈ESR*(1+C0/Cs)^2。其中ESR为谐振器的等效串联电阻,C0为晶体谐振器的shunt capacitance,Cs为晶振的负载电容,这三个参数一般都在晶体谐振器规格书手册中有标注。  振荡余量计算举例 原视频举了一个例子,过程如下图:  但是吧,我发现有个bug,实例里面Re=50Ω,ESR=100Ω,可以得到:ESR>Re。而从前面的计算公式Re≈ESR*(1+C0/Cs)^2,那么肯定有ESR<Re,两者矛盾了。 那么哪里出错了呢?我觉得公式是没错的,所以应该是举的实例算错了,兄弟们怎么看呢? 第3节、激励功率的测量 激励功率指的是晶体谐振器的功耗。 晶振厂家一般都会在手册中标注这个参数DL,如果实际电路中,晶振的实际功耗大于手册中标准的DL,那么就过驱动了,存在风险,可能会引起频率和等效串联电阻的意外变化。 测量方法  使用电流探头,并使用示波器或频谱分析仪等仪器,测量数据来计算上图中a点的电流值。 下面图片是村田使用频谱仪测量的过程: 1、接入电流探头  2、读取频谱仪中的功耗,然后计算电流值  3、计算  问题来了,里面那个0.2236是个什么鬼?我也没搞懂。。。 第4节、振荡频率的测量方法 振荡频率是指晶振在电路中实际工作的频率,决定振荡频率的主要因素是晶振的特性,但是,实际的振荡频率也受下面因素的影响: 1、芯片的特性 2、外部匹配电容的容量 3、PCB的杂散电容 面临的一个比较大的问题就是:如果用探头直接接触振荡电路进行测量,是无法精确测量频率的,因为会引入电容,所以,一定要通过非接触式的方式来进行测量。 测量仪器: 1、频谱分析仪 2、频率计数器 用频谱分析仪时,使用非接触式的天线来接收信号,读取频谱分析仪显示的峰值处的频率。   使用频率计数器时,也需要用非接触模式来测量,但是通常需要增幅信号到计数器能读取的水平,所以需要预备放大电路。  振荡频率相对偏差 实际的振荡频率受下面因素的影响: 1、芯片的特性 2、外部电容的容量 3、PCB的杂散电容 所以实际在PCB上测量频率的时候,即使使用同一个晶振,也可能跟晶振厂家的PCB上测量的频率不一样,这个偏差就是振荡频率相对偏差(并非相对晶振标称值频率的频偏)。 如果在频率偏差较大的状态下使用,有可能使得实际的振荡频率超出可以容纳的范围,进而导致产品工作有问题。  如果需要较高的频率精度,就需要格外注意频率偏差!必须把这个相对偏差加上谐振器的规格偏差(手册中的频偏),来判断是否能把频率调整在希望的范围内。 如下图:相对偏差为+5ppm,晶振规格偏差为±20ppm,所以,最终实际的频偏应该是:-15ppm~+25ppm。  实际工作中,可以跟厂家要带频率数据的样品,然后将样品装在自己的PCB板上实测,测得的频率与厂家给的频率之间的偏差就是相对偏差。 第5节、振荡电路与电路测试的关系 前面介绍了3个测试,分别是振荡余量、激励功率、振荡频率相对偏差。既然是测试,那么就有可能不合格,那么不合格怎么办呢? 自然是要调整电路,能调整的器件不多,主要是2个: 1、阻尼电阻Rd(串联电阻) 2、负载电容C1/C2(匹配电容)  那调整的目标是什么呢? 目标:振荡余量较大好,一般大于5倍;激励功率较低好;振荡频率偏差小好; 问题是这几个参数之间是矛盾的,因此需要进行平衡。 变动负载电容(匹配电容)时 如果减小负载电容,那么振荡频率会上升;反之如果增大负载电容,那么振荡频率会下降。  但是,另一方面,增大了负载电容,会导致激励功率增加,同时振荡余量减小,这都是不好的影响。  如果为了降低激励功率,减小振荡余量去调小电容,首先会造成频率升高。其次,如果电容太小,那么电容值本身的偏差,PCB板杂散电容的影响就会增大,造成振荡频率变化大。 变动阻尼电阻Rd(串联电阻) 首先,增大电阻,可以降低激励功率,但是会引起振荡余量降低,这两个影响一好一坏,需要平衡。 另外,从下图可以看出, Rd的变化对振荡频率的影响很小,从330Ω到470Ω,频率变化0.8ppm。  电路调整测量 结合前面的分析,电阻对振荡频率影响较小,振荡频率主要由匹配电容决定,而同时匹配电容又跟振荡余量和激励功率相关。 因此策略如下: 1、首先通过调整负载电容C1/C2(匹配电容)来调整振荡频率到合适值 2、再通过调整Rd来将振荡余量和激励功率调到合适的值。  小结 以上就是视频的主要内容,这样写下来,自我感觉确实比看一遍视频了解更多。 另外,关于晶振电路的测量,我个人其实并没有太多的经验,以前实际测试也只是拿示波器直接接触量的,并非像视频说的那样使用频谱仪来测量。不过从道理上来说,使用频谱仪测量确实应该更接近真实的情况。如果我们遇到晶振偶尔坏掉的问题,个人觉得上面这一套测试方法还是比较科学的分析手段。 晶振电路,兄弟们都是怎么测试的呢?测试了哪些内容呢 作者:炼成之路, 来源:硬件工程师炼成之路声明:本文经授权转载自“炼成之路”公众号。转载仅为学习参考,不代表本号认同其观点,本号亦不对其内容、文字、图片承担任何侵、电子技术干货、设计实例与应用方案 |