10. 低测试覆盖率的分析方法

时间:2024-07-25 21:06来源:功烨 芯爵ChipLord 作者:ictest8_edit 点击:

次

在半导体行业中,芯片测试覆盖率是衡量产品质量和可靠性的重要指标。然而,低测试覆盖率问题常常困扰着工程师和开发团队。本文将介绍几种分析和解决低测试覆盖率问题的方法,帮助提升测试效率和产品质量。

1. 什么是测试覆盖率?

测试覆盖率是指工具生成的测试向量可以检测到的故障与总的可测故障的百分比。高测试覆盖率意味着更多的潜在故障被检测到,从而提高产品的可靠性。

故障覆盖率则是工具生成的测试向量可以检测到的故障和总故障的百分比。

2. 低覆盖率问题的常见原因

高测试覆盖率的要求:

o 可观测性

o 可控制性

低测试覆盖率的问题主要源于以下几种情况:

· UC(UnControlled)故障:故障无法被设置成0或者1。

· UO(UnObserved)故障:故障无法向后传播到下游观测点。

· AU(ATPG Untestable)故障:通常由于constraint、nonscan cell、black box blocking。

· AAB(Aborted Faults)故障:工具在生成测试向量时多次尝试覆盖所有故障,但仍有部分故障无法覆盖,可以尝试增加abort limit来覆盖某些故障。

3. 解决低测试覆盖率问题的方法

i. 检查DRC报告,明确所有的warning:首先应检查设计规则检查(DRC)报告中的警告信息,解决所有可能影响测试覆盖率的问题。

ii. 设置合理的测试参数:在产生测试向量时,设置合理的参数可以有效提升测试覆盖率。例如,调整abort limit等参数可以尝试覆盖更多的故障。

iii.定位低覆盖率的模块:利用工具命令行或DFTVisualizer等工具,分析具体故障和电路,定位导致低覆盖率的模块。

vi. 定位低覆盖率的模块:利用工具命令行或DFTVisualizer等工具,分析具体故障和电路,定位导致低覆盖率的模块。

v利用DFTVisualizer分析具体故障和电路:DFTVisualizer是一个强大的工具,可以帮助工程师详细查看测试和故障覆盖率数据,分析具体的故障情况。

4. 案例分析

i. Clock Gating处理:对于Clock gating的enable pin,应推荐将Test Enable Pin接到scan enable信号,而非test enable信号。

v. BlackBox处理:Blackbox问题通常由于Memory model或Soft Module定义的缺失导致。应告知工具blackbox的端口,最终signoff时的ATPG不应该存在Blackbox。

vii. 约束检查:检查约束是否合理,例如使用add_input_constraints、report_input_constraints等命令检查输入约束。检查所有时钟是否定义,使用analyze_control_signals、report_clocks等命令。

x. 利用命令分析低覆盖率问题

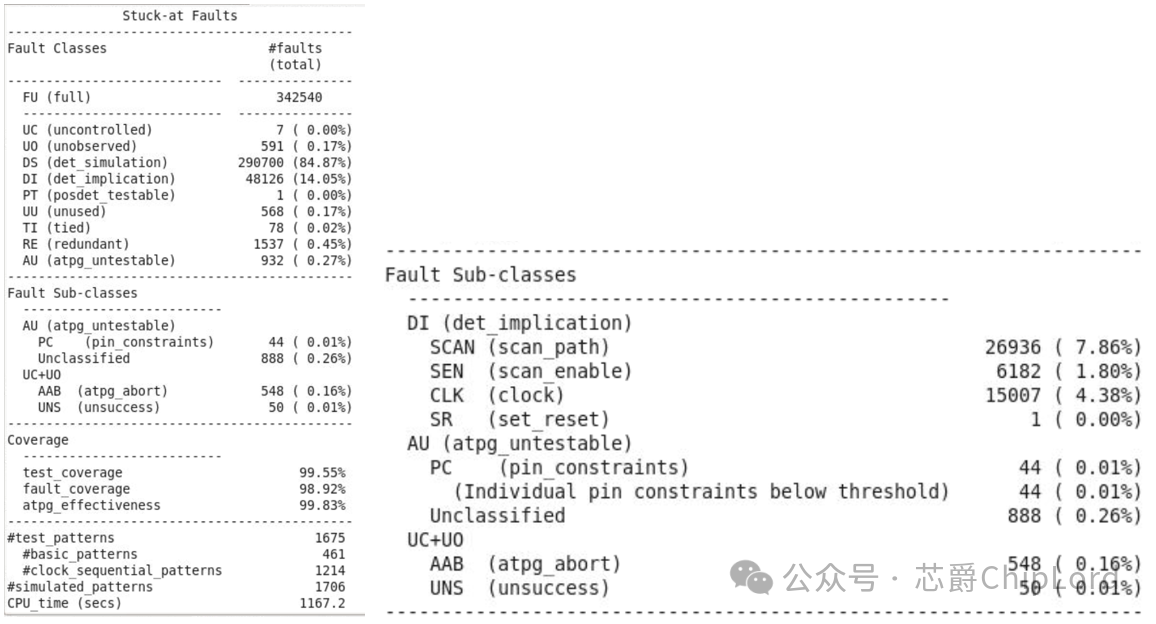

§ 报告统计数据:report_statistics命令可以生成测试覆盖率的统计数据,帮助分析测试效果。

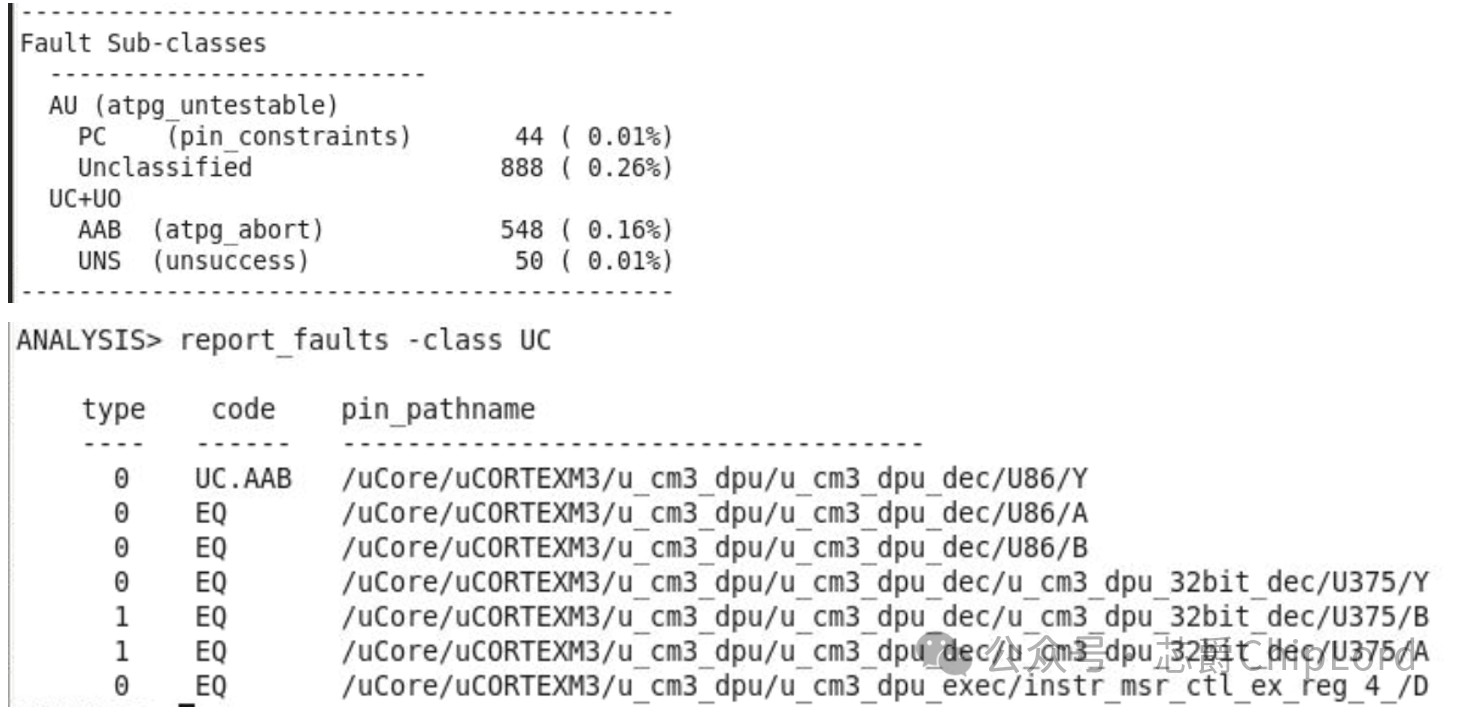

§ 报告故障信息:使用report_faults –class <fault_class>等命令,可以生成具体的故障报告。

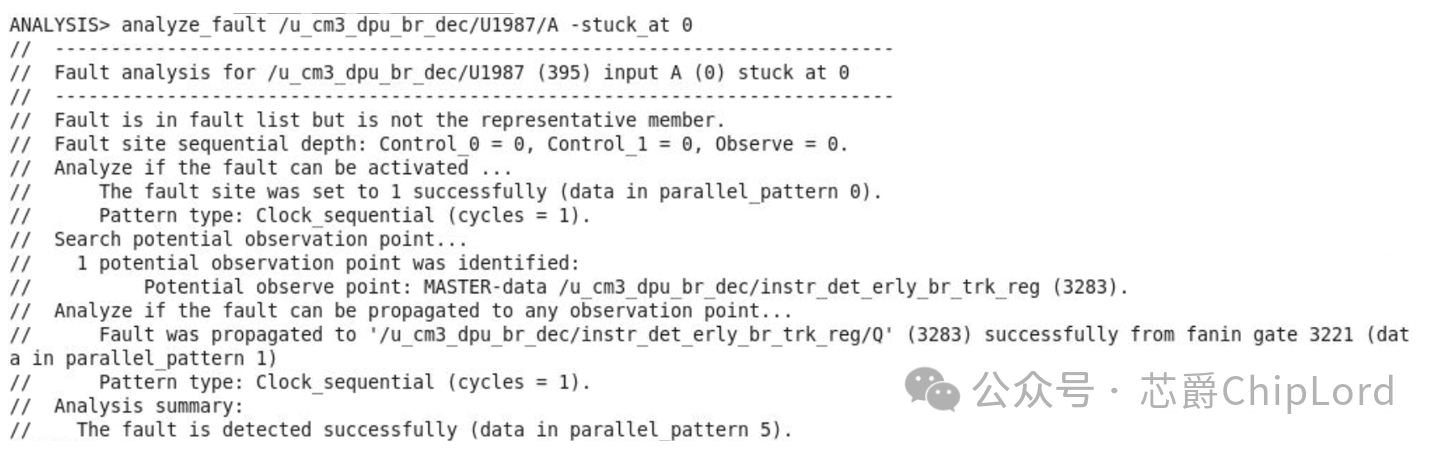

§ 分析故障:通过analyze_fault命令,详细分析特定的故障情况,找出问题根源。

§ 生成测试刺激:使用report_test_stimulus命令,生成相应的测试向量,提升测试覆盖率。

总结

低测试覆盖率的问题虽然复杂,但通过系统的分析和优化,可以显著提升测试效果和产品质量。利用DFTVisualizer和各种命令行工具,工程师可以精准定位问题,制定有效的解决方案。希望本文的方法和案例分析能为您的工作提供帮助,助力半导体行业的发展。

|

------分隔线----------------------------