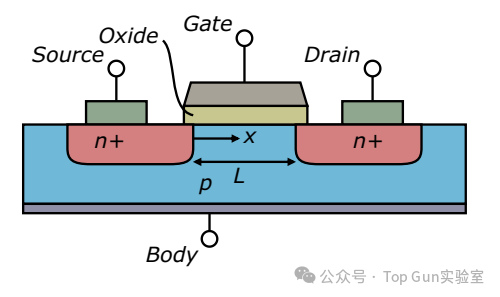

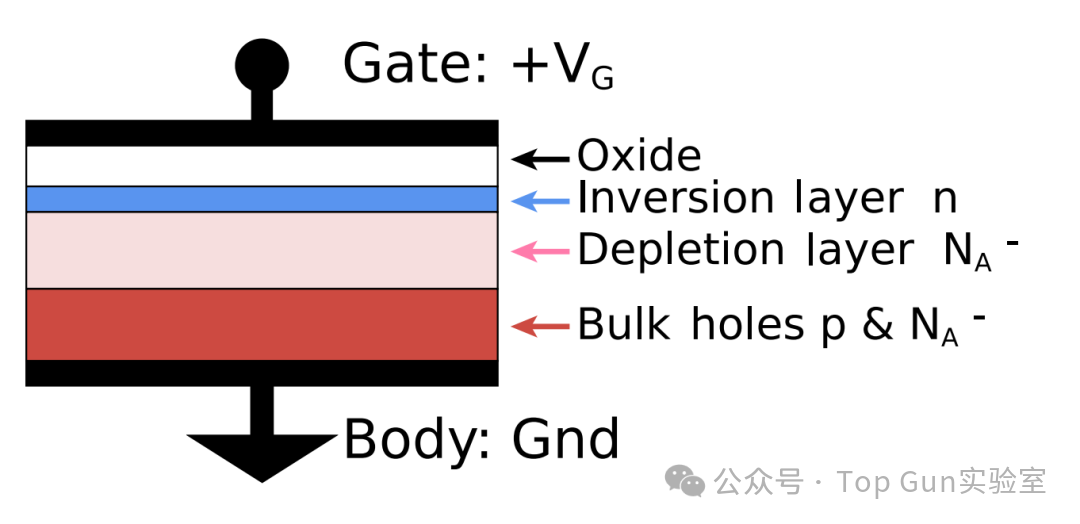

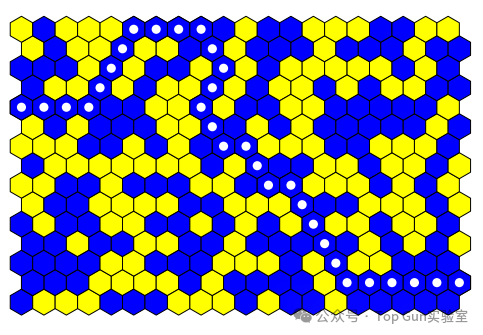

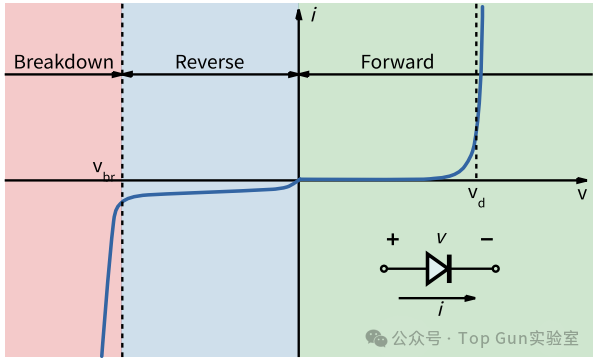

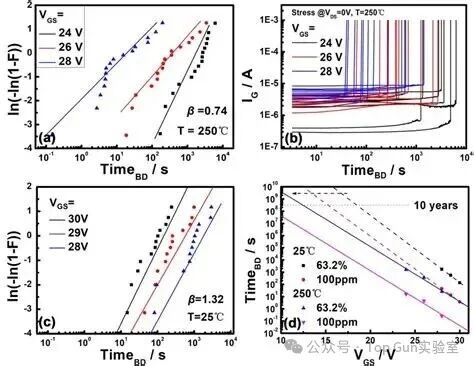

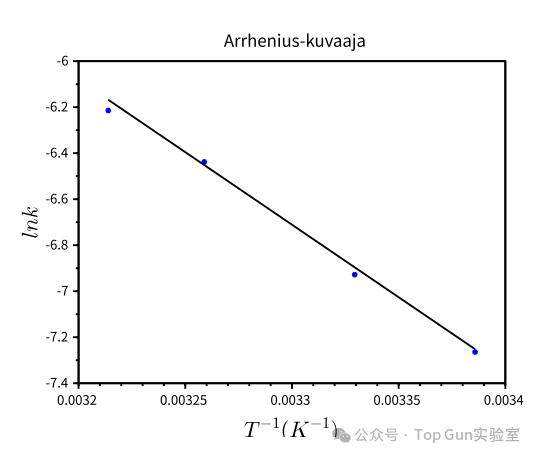

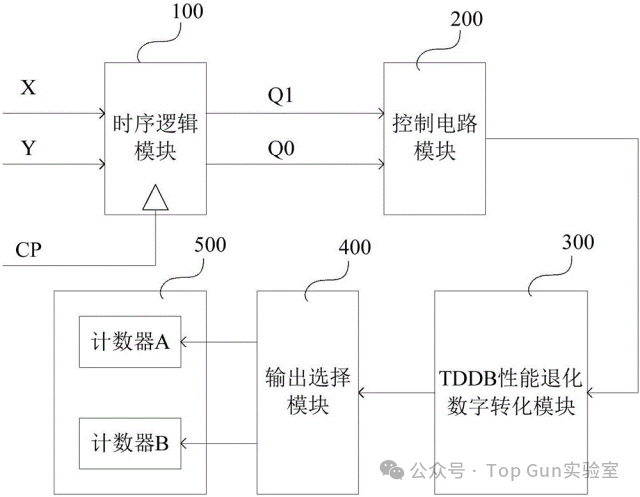

芯域前沿聚焦半导体行业最新动态、技术解析与深度科普,覆盖芯片设计、制造、封测全产业链。 无论您是工程师、投资者还是科技爱好者,在这里都能读懂“中国芯”的崛起逻辑与未来机遇。 硬核内容,深入浅出——与您共赴半导体黄金时代! 265篇原创内容 公众号 一层“薄玻璃”毁掉一颗芯片:TDDB(Time-Dependent Dielectric Breakdown,时间相关介质击穿)到底怎么来的?你可以把现代芯片里最关键的一层绝缘材料,想象成一片“纳米级的玻璃”。它薄到接近原子尺度,却要在高电场、反复开关、热胀冷缩、杂质与辐照(特定场景)等长期“折磨”下,依然保持绝 缘。 TDDB讲的就是: 在看起来并不“暴力”的工作条件下,介质(尤其是晶体管栅介质)会随时间逐步劣化,最终形成导电通路并发生击穿 。它不是“瞬间天降灾难”,更像一场 慢性退化→临界点崩盘 的连续剧情。 本文用“从物理到工程”的方式,把TDDB失效为什么会发生、怎么测、怎么用统计与模型外推、以及如何在材料/工艺/设计/使用环节降低风险,完整讲透。 01TDDB发生在芯片哪里?先认识那层“最薄、最要命”的栅介质 在MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor,金属-氧化物-半导体场效应晶体管)里,栅极与硅沟道之间隔着一层极薄的栅介质,早期以SiO2为主,后来广泛采用HKMG(High-k Metal Gate,高k金属栅)结构:高k介质+金属栅+界面层。栅介质必须做到两件看似矛盾的事: · 电学上要“绝缘”:阻止直流电流穿透,否则静态功耗暴涨、器件参数漂移甚至直接失效; · 电容上要“足够耦合 :让栅压能有效控制沟道。 越先进的制程,等效氧化层厚度(常用EOT,Equivalent Oxide Thickness概念衡量)越小,栅介质承受的 局部电场、缺陷敏感性、统计波动 越强,TDDB也就越重要。这里容易产生一个误解: “只要电压不超规格,就不会击穿。” 现实是:即便电场低于“瞬时击穿”阈值,长时间应力也会让缺陷逐步累积,最终在某个随机时刻跨过临界点。 这就是“时间相关”。  02TDDB的“第一性原理”:缺陷/陷阱是怎么被一点点“养大”的? TDDB的核心物理过程,通常围绕两个关键词: 缺陷生成与导电通路形成 。很多研究将介质劣化描述为随机的“陷阱(trap)/缺陷”逐步产生、累积的过程;当这些缺陷数量与空间分布达到某种临界状态,就会形成贯通介质的导电路径,导致击穿。常见的“缺陷来源/增长机制”包括(不同材料体系占主导的机制可能不同): 1. 电场驱动的键断裂与结构重排介质内部的化学键(例如Si–O键或高k材料中的金属-氧键)在强电场与载流子注入下会逐步弱化。部分模型把它视为热化学过程:电场降低反应势垒,使键更容易断裂。 2. 载流子注入与陷阱辅助隧穿(TAT) 超薄介质中即便未击穿,也可能存在可测的隧穿电流。电流本身并非“无害”,它可能通过能量交换、局部发热、以及对缺陷态的占据/电荷转换,加速新的陷阱产生;同时,陷阱又会进一步增强陷阱辅助隧穿(TAT,Trap-Assisted Tunneling,陷阱辅助隧穿),形成“正反馈”。 3. 界面与氢相关效应在很多栅介质体系里,氢相关键(如Si–H)与界面状态对可靠性很关键。有研究用反应-扩散(reaction–diffusion)思想解释某些应力与恢复现象,强调氢或相关物种在界面/介质中的迁移与反应可能控制缺陷生成速率。 你可以把整个过程理解成: 介质不是“完美玻璃”,它里面有潜在的“微小空洞/弱键/杂质”。 长期电场与载流子注入让这些弱点逐步增多、扩大、连接,直到出现一条能让电子(或空穴)更容易通过的“高速路”。  03从“散点缺陷”到“一条通路”:渗流模型解释了为什么击穿是随机且突然的 为什么TDDB看起来像“突然发生”?因为最后一步常常是渗流通道(percolation path)的贯通: · 前期:缺陷在介质中离散分布,漏电流缓慢变化; · 中期:缺陷密度上升,局部区域开始“更容易导电”; · 临界:缺陷连成贯通路径,导电急剧增强; · 后期:可能出现更强的局部热、材料进一步损伤,形成更稳定、更低阻的通道。 渗流理论之所以有说服力,是因为它天然解释了两件事: 1. 统计性 :同一批器件,击穿时间不一样——因为缺陷生成是随机过程; 2. 阈值性 :当缺陷密度达到某个临界水平,连通性会“跃迁式”提升,于是表现为“突然击穿”。 在先进栅堆栈(例如高k+界面层)里,材料分层、缺陷生成速率差异、以及界面附近电场分布,都可能让统计分布呈现更复杂的形态(例如双斜率Weibull现象在一些研究中被讨论)。  04软击穿与硬击穿:你看到的“漏电流曲线”其实在讲故事 在工程测试里,TDDB常用“漏电流随时间”的行为来判定击穿事件。击穿并不总是“一刀毙命”,常见会区分: · SBD(Soft Breakdown,软击穿) :导电通路形成但电阻还不算极低,漏电流跳变后可能仍在可测范围;器件可能还能“凑合工作”,但参数漂移、噪声、功耗、甚至后续失效概率都会上升。 · HBD(Hard Breakdown,硬击穿) :形成更低阻、更稳定的通路,漏电流大幅飙升,往往导致功能失效或引发级联损伤。 为什么会有软/硬之分?一个直觉是: 初次贯通的通路可能“细、弯、断续”,导电增强但不至于立刻短路; 随后局部电流密度上升→局部温升→更多键断裂/缺陷扩展→通路变粗变直,最终走向硬击穿。 对系统而言,软击穿尤其麻烦,因为它可能并不立即暴露为“死机”,而是以 静态功耗增加、阈值漂移、时序裕量减少、偶发错误率上升 等形式出现,表现为“越用越不稳”。  05Weibull(韦布尔)分布是可靠性工程的“通用语言” TDDB不是“某一颗器件一定在X小时击穿”,而是“在某个应力条件下,一群器件的击穿时间呈统计分布”。因此,可靠性工程常用Weibull(Weibull Distribution,韦布尔分布)来描述 失效时间分布 : · 横轴:击穿时间tBD(time-to-breakdown,击穿时间); · 纵轴:累计失效概率F(0~1); · 关键参数之一:β(beta,形状参数/斜率),反映分布形态与一致性。β越大,分布越“陡”,批内一致性越强;β较小则离散更大。 许多TDDB研究与建模都围绕“为什么β会随材料、厚度、工艺、应力模式变化”展开,并用渗流/单元模型等解释β与缺陷生成空间统计之间的关系。这里必须强调一点: 统计不是“玄学拟合”,而是把微观随机过程用宏观可用的方式表达出来。 没有统计分布,谈“寿命”就会变成单点猜测。  06只在高压下测几小时,怎么推算“十年寿命”? 实际使用条件下,芯片希望工作多年;但实验室不可能等十年再出报告。于是必须做 加速应力测试 :在更高电压/电场、更高温度下加速缺陷生成,用模型把结果外推回使用条件。一个典型且被标准化的做法是:对超薄栅介质进行恒压应力(CVS,Constant Voltage Stress,恒压应力)TDDB测试,并提取电压与温度加速参数。JEDEC(JEDEC Solid State Technology Association,固态技术协会)的JESD92(JESD92,超薄栅介质TDDB表征流程)就给出了这种测试与表征的规范框架。在外推模型上,历史上存在多种电场加速形式(不同材料、厚度、应力区间可能更贴近不同模型): · E-model(Electric Field Model,电场模型) :寿命与电场呈指数关系的一种形式; · 1/E-model(Inverse Electric Field Model,反电场模型) :寿命与1/电场呈指数关系; · Power-law(Power Law,幂律模型) :寿命与电场呈幂函数关系。 为什么会“多模型并存”?因为TDDB可能由不同微观机制主导(例如热化学、空穴注入、界面不稳定等),不同机制对电场、温度、频率/波形的敏感性不同。有研究专门回顾并讨论了TDDB模型与观测现象之间的对应关系,提醒工程外推要警惕“单一机制假设”带来的偏差。另外,真实系统里栅压并非总是直流:有开关、有PWM、有高频脉冲。近年来也出现用脉冲电压方式评估TDDB、更贴近工作波形的研究(例如在功率器件场景)。一句话总结外推的正确姿势: 先用规范方法把“加速条件下的统计分布”测准,再用与物理机制相容的模型做外推,并用不同应力点交叉验证。  07追根溯源:TDDB“失效产生原因”到底有哪些? TDDB不是单点原因,而是“材料+工艺+设计+使用环境”共同决定的结果。把它拆开看,原因大致分为四层:7.1 材料与界面:先天体质决定上限介质本体的缺陷密度与类型 :高k材料相较传统SiO2往往更复杂,缺陷态、晶粒边界、相分离等都可能影响陷阱生成与渗流路径形成。界面层稳定性 :高k/Si界面通常需要界面层(IL,Interfacial Layer,界面层)来保证迁移率与可靠性;界面状态、氢相关键、以及界面粗糙度都会改变局部电场与缺陷演化。 7.2 制造工艺:制造缺陷会把“随机失效”变成“早发灾难”TDDB常被区分为:Intrinsic(Intrinsic Breakdown, 本征击穿) :由电应力诱导缺陷逐步生成导致;Extrinsic(Extrinsic Breakdown,外禀击穿) :由制造过程引入的初始缺陷导致提前击穿。外禀缺陷可能来自:颗粒污染、薄膜沉积缺陷、局部厚度非均匀、刻蚀/清洗损伤、金属杂质、等离子体损伤等。它们会让某些点的“初始缺陷密度”更高,导致早期失效概率抬升,可靠性分布出现长尾或双斜率等复杂表现。 7.3 电路与版图设计:你给它怎样的电场,它就怎样老化电压裕量与过冲 :开关瞬态、栅驱过冲、环路寄生引发的尖峰,可能让“名义电压合规”变成“局部电场超标”。占空比与波形频率 :即便峰值相同,不同波形(直流/脉冲/交流)对缺陷生成与恢复的影响可能不同,需要用更贴近工作模式的评估方法校准。局部温度 :自热会提高反应速率、改变载流子能量分布,从而改变TDDB寿命(温度加速是可靠性外推的重要维度)。 7.4 使用与场景:你以为是“偶发”,其实是“长期累积”散热不足/长期高温 :温度是加速因子之一,热管理是可靠性的一部分。ESD(ElectroStatic Discharge,静电放电)或瞬态过压的后遗症 :即使没有当场击穿,也可能在介质里留下潜在损伤点,后续在正常电压下更容易走向TDDB(这属于工程经验与失效分析常见逻辑:一次“近失效”会改变后续寿命分布)。  08工程落地:如何把TDDB风险压下去? 把对策也按链条拆开,你会发现它更像系统工程,而不是“某一个神奇参数”。8.1 工艺侧:把外禀缺陷打下去,收益往往最大 · 强化洁净与颗粒控制,降低局部薄弱点; · 优化沉积/退火窗口,稳定介质与界面; · 对等离子体、清洗、刻蚀等可能引入损伤的步骤做更精细的监控与抽检; · 用统计方法区分早期外禀失效与本征磨损,避免把“工艺缺陷问题”误当成“材料上限问题”。 8.2 设计侧:管理“实际电场”,而不是只看“标称电压” · 控制栅驱过冲/振铃;必要时加阻尼或优化布局走线; · 为关键路径留出合理裕量,但避免盲目保守导致功耗与性能全面牺牲; · 对不同工作模式(直流偏置、脉冲、频繁开关)分别评估可靠性。 8.3 测试与评估侧:按标准做加速,按物理选模型,按数据做验证 · 采用规范化流程(如JESD92(JESD92,超薄栅介质TDDB表征流程))进行恒压应力TDDB,得到可复现的加速参数。 · 在不同电场点、不同温度点进行交叉验证,避免单点外推; · 结合机理回顾型研究对模型适用性做判断,警惕“拟合很好但物理不对”的情况。  09结语:TDDB不是“工程师的锅”,而是先进工艺时代的必修课 当栅介质薄到纳米级,任何“微小缺陷”都有机会被时间放大。TDDB告诉我们: · 可靠性问题往往不是“会不会发生”,而是“以什么分布、在什么条件下、以多大概率发生”; · 解决它也不是“一个旋钮”,而是从材料/工艺/设计/使用/测试的全链条协同; · 最重要的工程思维,是把“微观随机缺陷”用“可验证的统计+物理一致的模型”转化为可决策的寿命预测。 如果你把芯片看作一座城市,那么栅介质就是城市最关键的“绝缘大坝”。 TDDB不是大坝被雷劈坏,而是材料在长期水压与风化中逐渐疲劳 。理解这条失效链条,你就更容易在设计、制造与验证阶段,提前把风险关在笼子里。 |