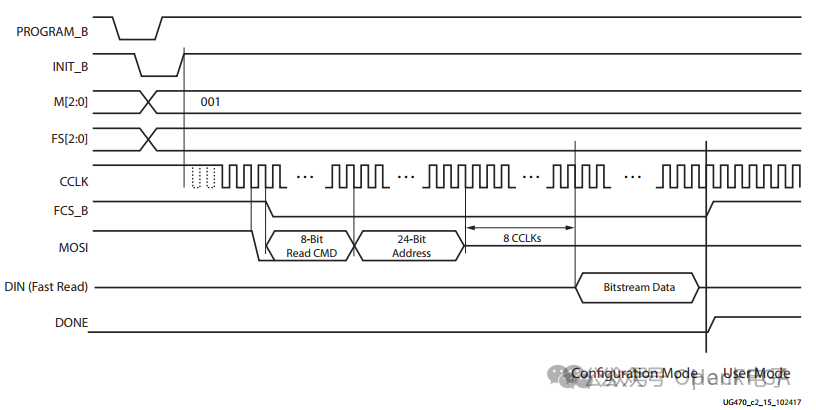

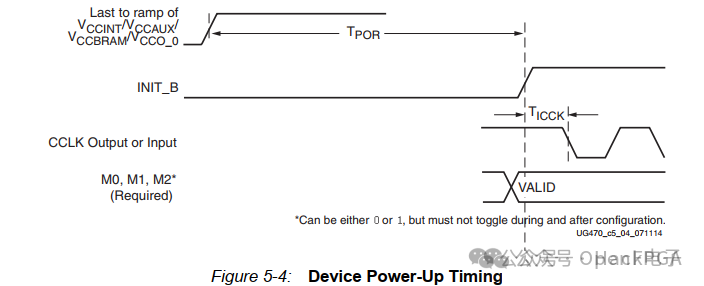

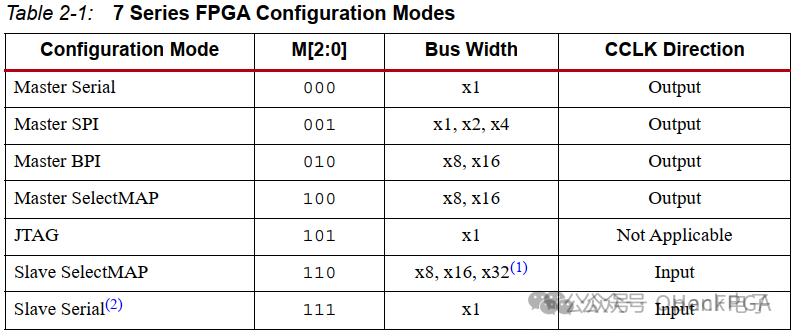

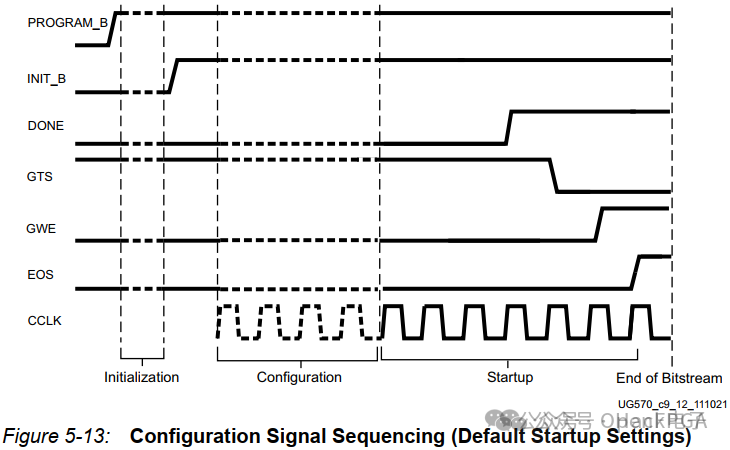

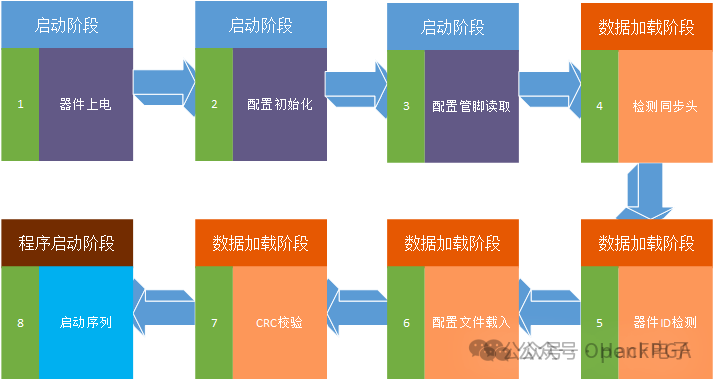

以下文章来源于OpenFPGA ,作者碎碎思这个系列开篇肯定要先了解FPGA的启动流程,试想一下:我想实现MultiBoot,那么我应该在什么时候开始升级,升级失败后FPGA进行了哪些操作,以及怎么回到Golden区? 还有一个问题,就是我硬件打板回来,烧写进FLASH后起不来,这应该怎么排查? 缩略词索引: · K7:Kintex 7 · V7:Vertex 7 · A7:Artix 7 以上所有这些的前提就是理解FPGA启动流程。  图0:7系列FPGA启动步骤-参考:UG470 AMD-Xilinx FPGA启动阶段大概可以分为以上几个步骤(上图参考来源:UG470 Figure 5-3),下面分别讲解每一个步骤中FPGA做哪些工作。

|