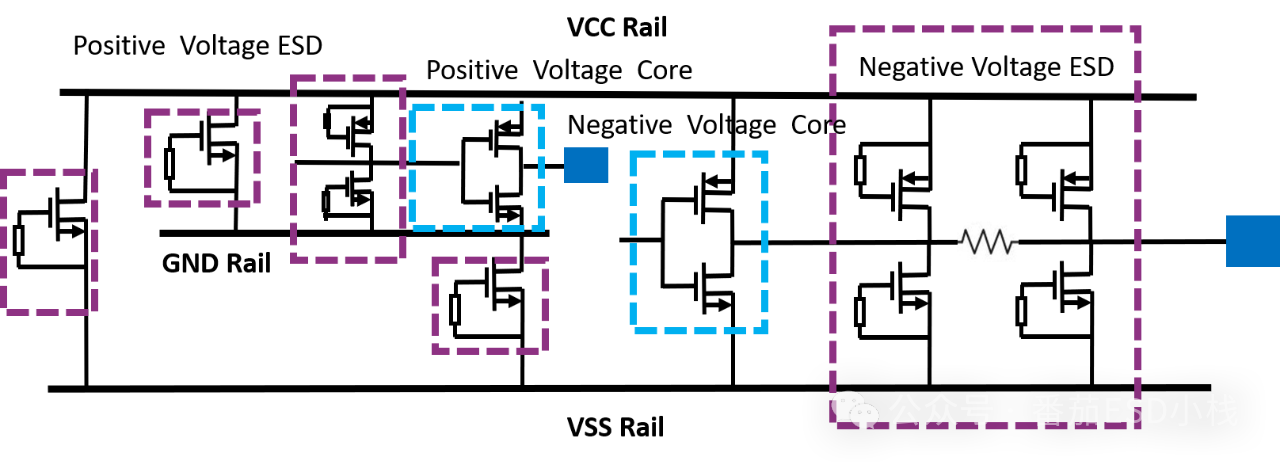

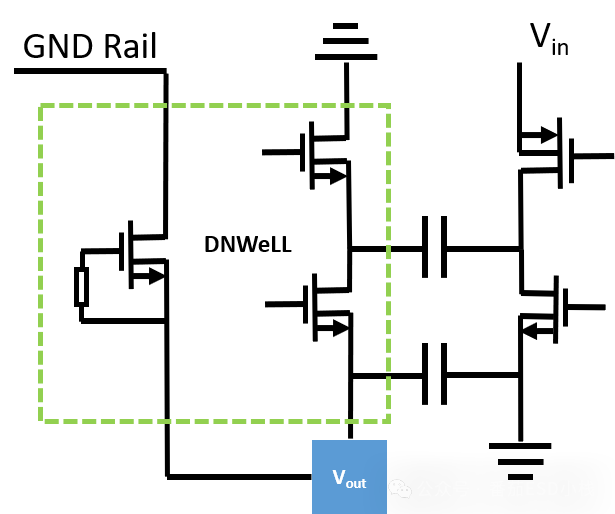

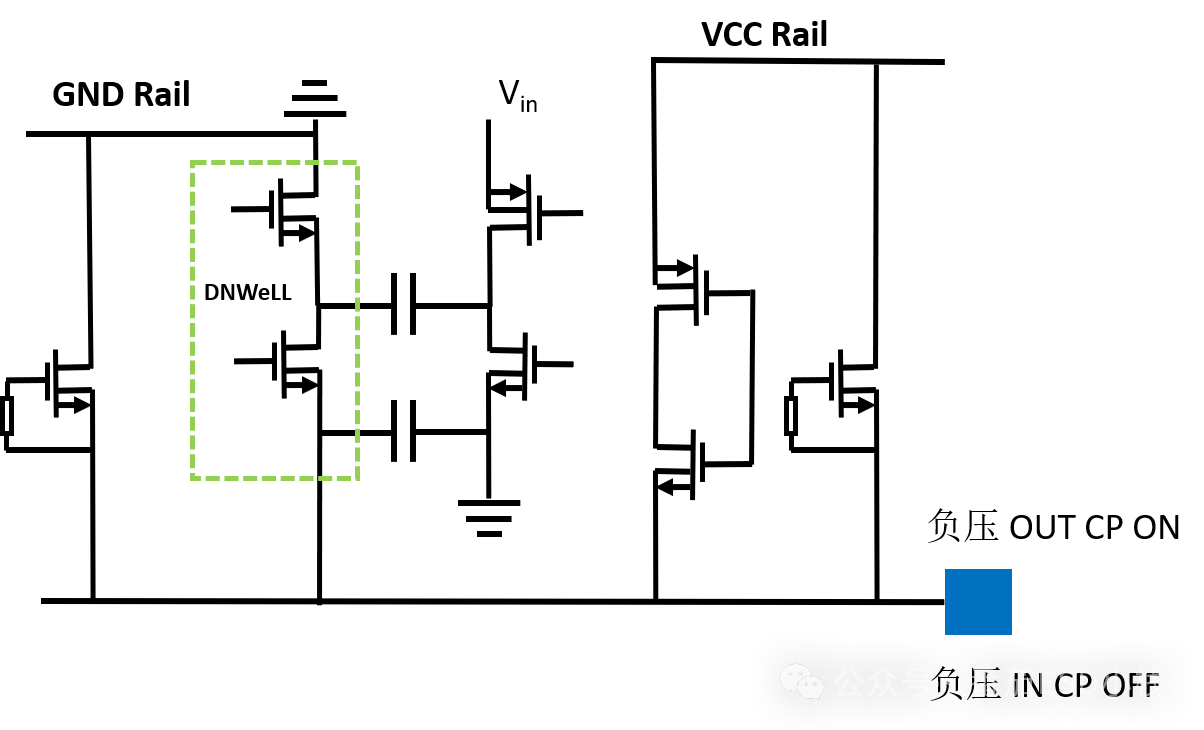

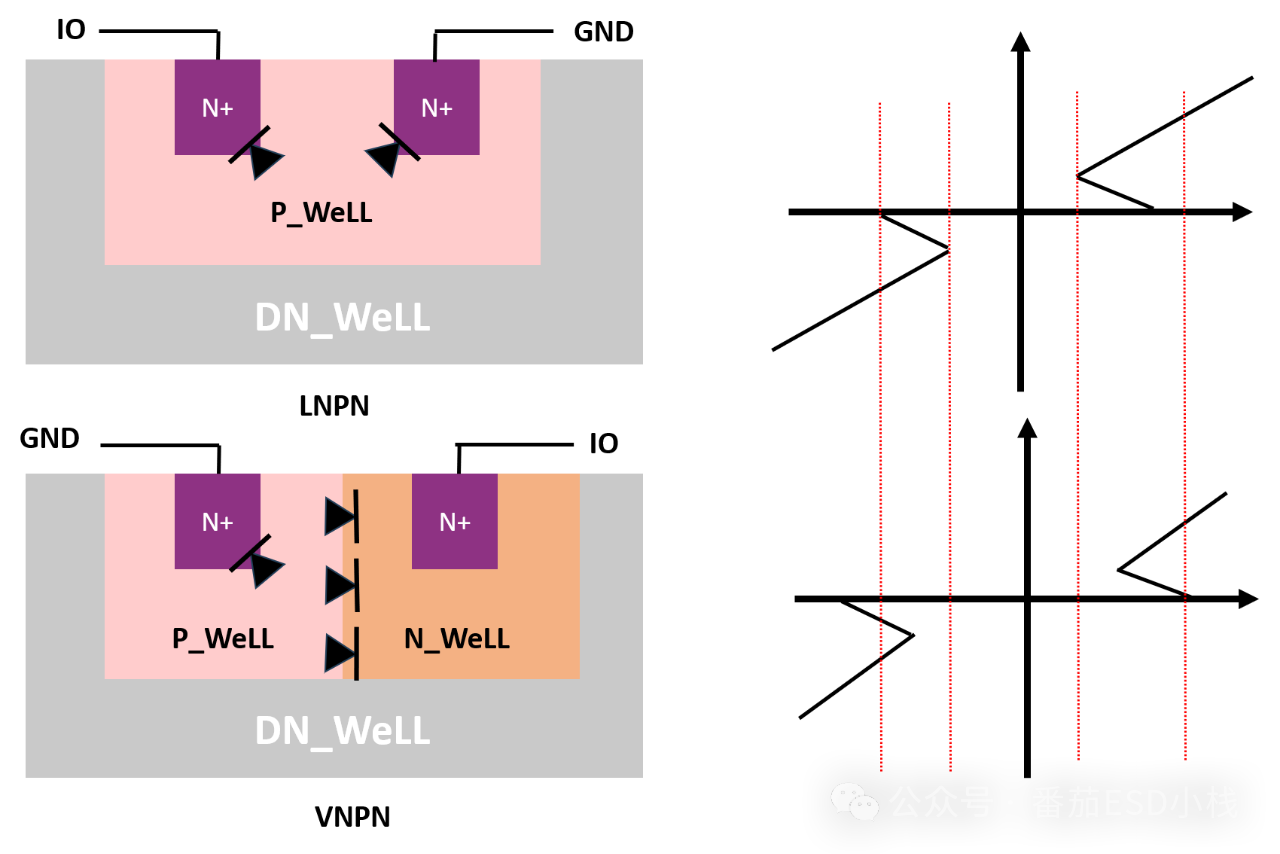

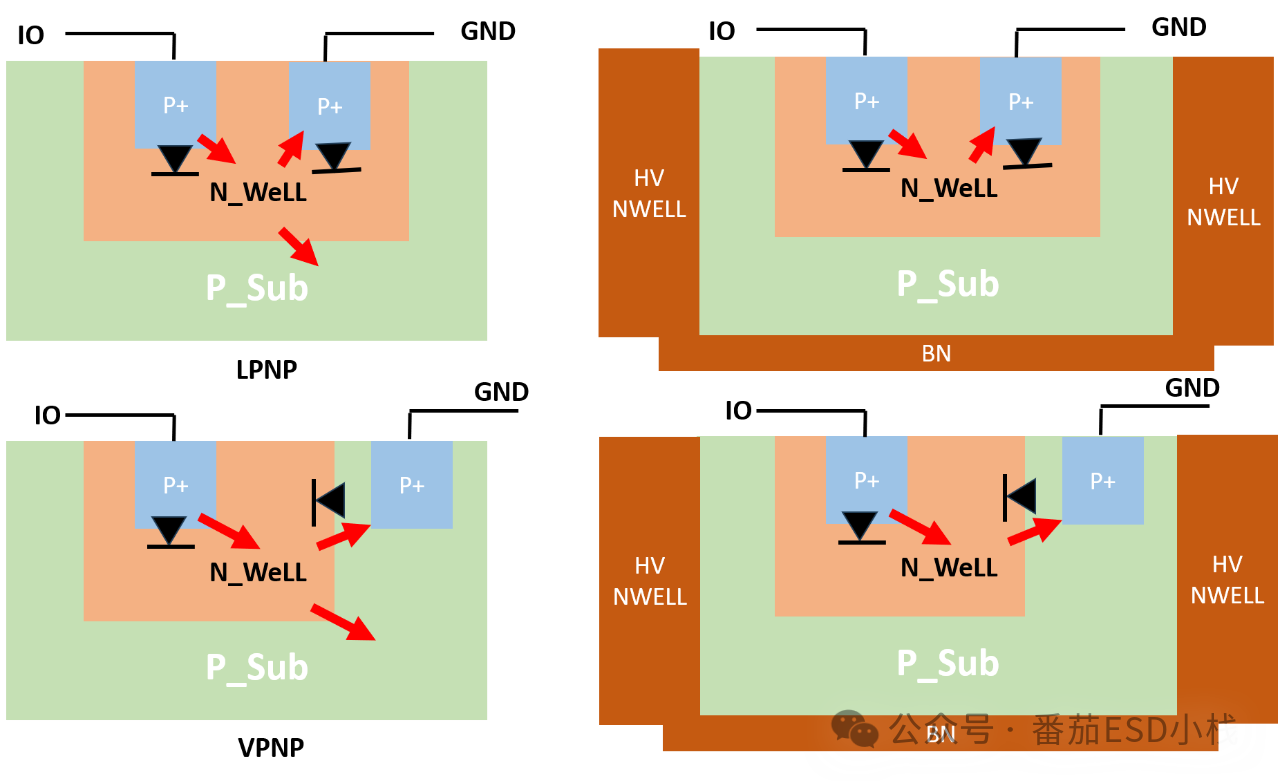

芯片有时会遇到正负电压IO/VSS/VDD的情况,此类端口的ESD设计有一定难度。这一期笔者将对这种情况进行阐述。一.Power负压 1.1.VSS负压供电 这类属于最简单的情况,芯片外部有稳定的负压供电,整个芯片的最低电位VSS是由外部稳定提供,GND是中间电位,芯片的输入输出电压都介于VDD与VSS之间。如图一所示,将VSS作为负压域的ESD Rail,而正压域依然采用GND作为ESD Rail,VSS在GND和VDD之间都需要建立Clamp,NMOS/Bipolar/Diode都可以作为Clamp器件,但是正电压域的IO到VSS之间会经过两个ESD器件,IO—GND—VSS,会降低设计窗口的裕度。因为有稳定的负压,这类芯片可以采用VSS作为隔离电位,但是需要确定P-Sub的电位,如果P-Sub是VSS就需要对GND为衬底的NMOS进行隔离,反之,P-Sub是GND,则需要对VSS为衬底的NMOS进行隔离。  图一.VSS负压供电ESD architecture。 1.2.负压输出电路 这类情景最典型的应用就是Charge Pump,电荷泵通过电容的充放电输出负电压。如图二所示,对于负压输出端口只需要建立对GND的ESD防护单元,该ESD器件最好与驱动管类型保持一致,可以将驱动管的版图调整为更利于ESD的画法,避免一致性风险。但又会引出一个新的问题,如果Vout电压足够低,驱动管采用NLDMOS,负压输出端口就需要参考高压端口的ESD设计思路,Vout与GND间的ESD器件/器件组得耐高压且保证ESD泄放能力。  图二.负压Charge Pump ESD architecture。 随着芯片的集成度越来越高,芯片可能同时出现上述两种情况:芯片自身的Charge Pump生成负压给自己的模块去用。如图三所示,此时需要考虑Charge-Pump的Bypass模式,既能由Charge Pump输出负压,又能由外部提供负压。具有Bypass模式的供电端口,不仅要有内部模块的保护措施,还要有端口处的保护措施。因为电荷泵生成的负压并不会一步到位,部分器件在上电过程中会存在隔离不到位的情况。此类电路的电压域复杂,P/N阱和埋层的嵌套也很繁杂,会存在大量寄生二极管,需要防止ESD通过预想之外的寄生二极管进行泄放。  图三.负压Charge Pump+负压供电 ESD architecture。 二.IO负压 这种情况电路并不存在负压供电,但是IO会有负压。电源总线和部分工业通信类芯片会遇到这类情况:总线上会出现一个负压信号,芯片需要正确采集这个信号,或对该信号保持透明。IO上的负电压不能对GND漏电,且器件的SOA要大于负压,保证负压下器件不会损坏,但IO又要保持ESD防护能力。针对这种情况常采用三种设计思路: 2.1.浮阱器件 浮阱器件就是将三极管的基级浮空,通过PN结的空间电荷区对负压进行阻挡,而发生ESD时,正负极性都需要击穿电荷区使得器件发生Snap Back,从而实现对ESD的泄放。如图四所示为基级浮空的Vertical/Lateral PNP/NPN示意图。NPN的IO接集电极,基级浮空,射电极接GND,基级的P-Well需要用DNWeLL或者HVNweLL与P-Sub隔离。IO出现负压时,因为基级浮空,集电极与基级导通,此时射电极相当于高电位,集电极与基级构成反偏结。只有射电极与基级发生雪崩击穿,该器件才会构成射电级到集电级的电流通路。  图四.基级浮空NPN示意图与TLP曲线。 当IO存在正压时,集电极与基级反偏,基级与射电极正偏,该器件也不会存在电流通路。所以该器件保持了对IO正负电压的透明性。当IO/GND发生ESD时,因为正反方向都存在空间电荷区,所以该器件拥有Dual Snap back特性。 Horizontal NPN集电极和射电级都是N+,C/B Break Down Voltage等于E/B Break Down Voltage。而Verical NPN存在浓度梯度,C/B Break Down Voltage远大于E/B Break Down Voltage,Snap Back程度弱。对耐压没有要求的情况下,从理论上说Horizontal NPN的性能会更加优异,但是实际情况却比较复杂,Horizontal NPN可能会面临鲁棒性风险,因为基级浮空,所以基区宽度调制效应和基区展宽效应的相互作用更加复杂。具体选择哪种构型,需要根据工艺与需求进行斟酌。PNP的工作原理与NPN类似,不过如图五所示,需要额外对P-Sub进行一次隔离,不然ESD进入衬底会带来预想之外的风险。  图五.基级浮空PNP示意图。 浮阱三极管会存在如下弊端:一.稳定性较差,基级浮空造成基级电位一直处于不定态,尤其在进行ESD Loop时,第一次和之后的结果可能存在差异。二.设计窗口窄,因为该器件正反方向都存在Snap Back,从别的端口过来的ESD电流也要发生雪崩击穿才能泄放出去,所以会把ESD泄放路径沿途的压降抬的很高,对内部其它器件会带来风险。三.隔离繁琐,要保证负压下IO不与衬底短路的同时,还要尽力保证ESD不能窜入衬底,所以需要对器件的隔离进行review,而SOI+DTI的工艺会避免很多麻烦。 这一期先到这里,下期讲解浮轨和单向防护对IO负压防护的应用。以及如何针对Power/Gnd反接的情况进行ESD防护设计。 |