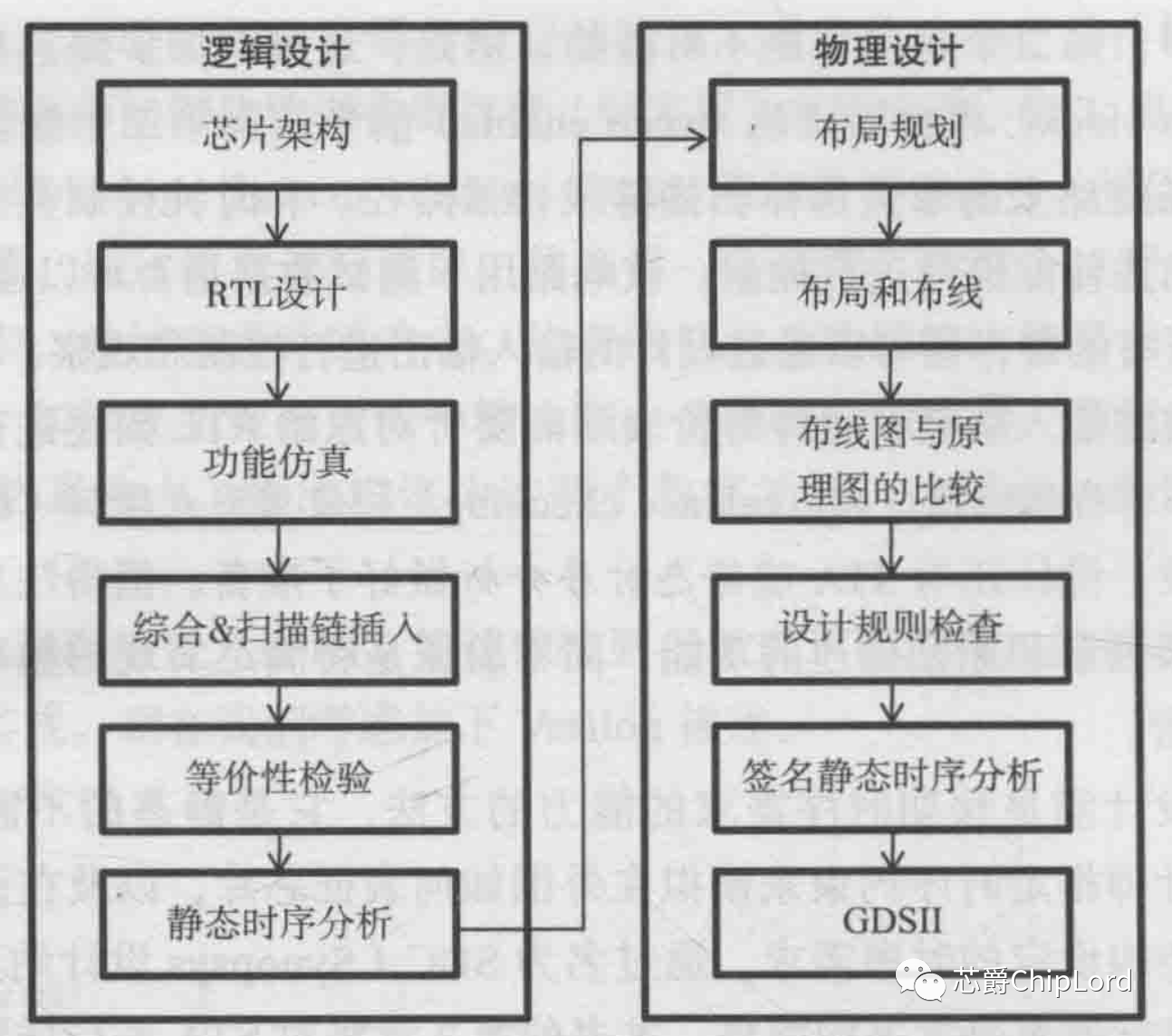

典型的ASIC设计流程可分为逻辑设计和物理设计两个部分。逻辑设计开始于高层次设计规范和芯片架构。芯片架构描述高层次功能、功耗和时序(设计运行的速度)需求。紧接着对设计进行寄存器传输层的描述,通常称为RTL(register transfer level),按照设计中信号的逻辑操作如何使数据在寄存器之间流动,RTL提供了电路功能行为的抽象描述。RTL通常用Verilog、System Verilog、VHDL等硬件描述语言(HDL)进行描述。编程设计功能以后,通过仿真进行验证。仿真是一个过程,在这个过程中各种激励加载到设计中,并捕获设计的响应。仿真的目的是验证输出结果与电路预期的功能是否相匹配。例如要验证两个输入和一个输出的加法器,测试向量把相加的两个数字作为仿真输入,输出应该为两个数字之和,验证通过,设计就做好了综合的准备。 综合(又称为逻辑综合 logic synthesis)是RTL描述传输到门级表示的步骤,门级表示是用HDL描述功能硬件的等价实现。 举例如下verilog描述:

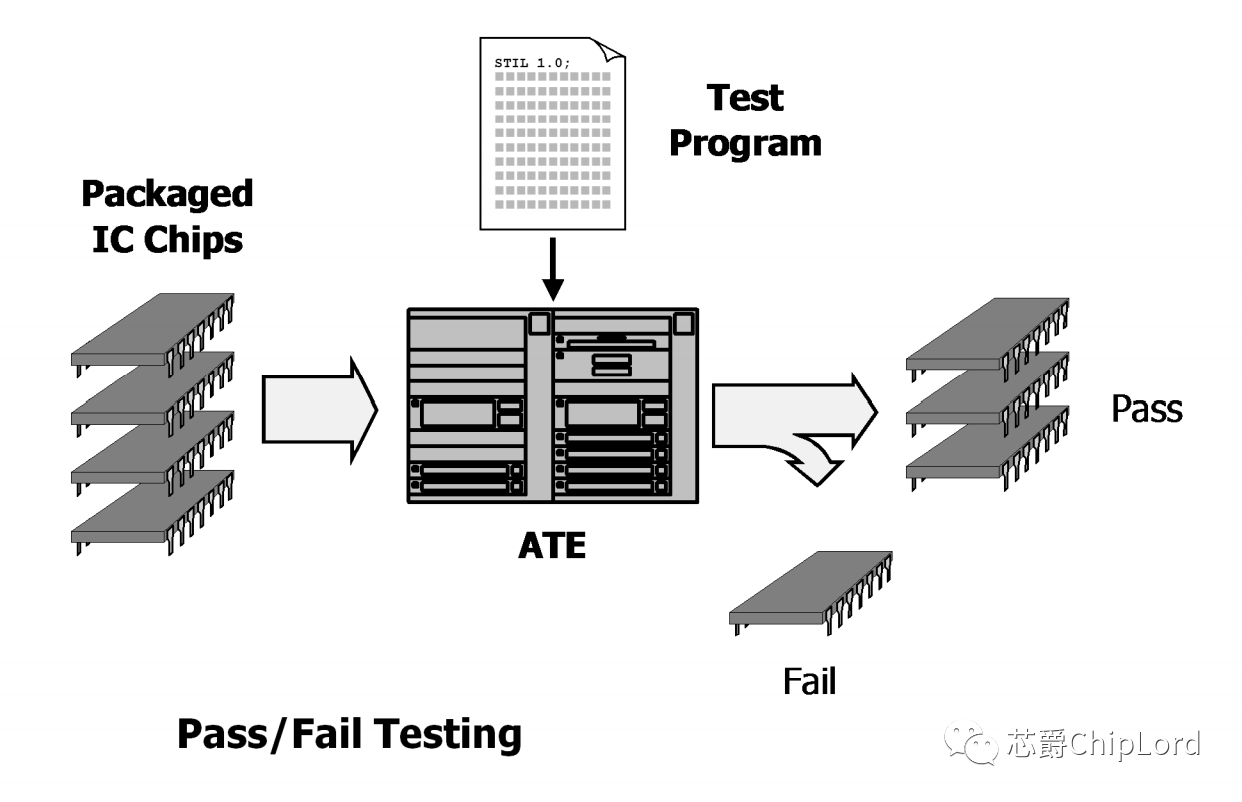

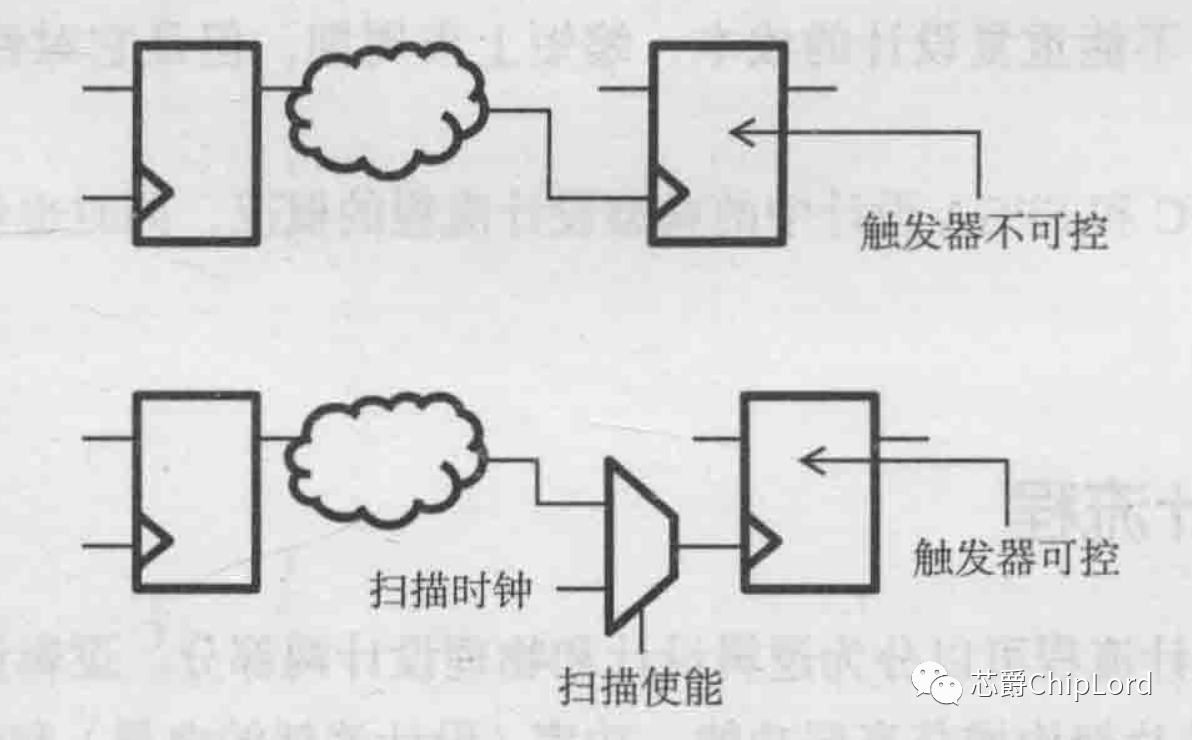

定义一个正沿触发的同步复位D触发器,有三个input,一个output,当时钟正沿的时候,如果rst信号为1,输出0,否则输出d端值。 综合工具可以把上述RTL描述映射到由上升沿触发的同步复位触发器上。如果此HDL描述能够使用行业标准综合工具映射到一个唯一并且明确的实现上,则可称为可综合的RTL。在综合步骤中,设计者还需要采集某些设计和时序特征,它们代表了芯片架构阐述的高层目标,如时钟频率、基本单元可用延迟、目标库等,以便综合工具能够优化设计从而满足需求。 完成综合之后,设计开始为DFT做准备,DFT,可测性设计指在芯片设计阶段即插入各种用于提高芯片可测性(包括可控制性和可观测性)的硬件逻辑,通过这部分逻辑,生成测试向量,达到测试大规模芯片的目的。  考虑下图的电路,第二个触发器是不可控的,但是通过增加多路选择器(mux),用户能够使用扫描时钟(scan clock)和扫描使能(scan enable)信号控制第二个触发器。这种将所有寄存器都连到一条链路上的形式称作为扫描链或扫描路径。和时钟控制类似,进入触发器的数据也可以通过scan enable信号进行控制。  在综合和扫描链插入以后,硬件等价表示需要针对原始RTL进行验证,以便保存设计目的。这称作等价性检验(equivalence checking)和形式验证(forml verification)技术。在这个阶段,设计还为STA或静态时序分析做好了准备。值得注意的是,等价性检验只验证实现的门级表示和原始描述的功能,而不验证是是否满足频率目标,验证频率目标是STA的职责。 STA是检查设计是否满足时序要求,它是静态的,不需要模拟。大多数STA引擎要求设计师指定时序约束来模拟在外围如何表征芯片,以及在设计内部做何种假定来满足芯片架构设定的时序需求。通过SDC的行业标准格式来做出规定,STA完成了逻辑设计步骤,充当逻辑设计和物理设计之间的桥梁。 物理设计开始于布局规划。经过初步的时序分析之后,设计的逻辑块以优化区域、长宽比、基本单元之间的通信等目标进行布局。目标是保证没有太多的内部交换,从而避免布线上的拥堵和困扰。这些因素直接影响功耗、面积、时序和性能。一旦达到了优化的布局规划,基本单元之间的连接就开始布线。 在综合阶段,许多假设都是关于时钟网络的,这是因为层次设计信息是不可用的,只有在完成布局规划后才可用。布局规划之后紧接着是时钟树综合,时钟树综合会尽量均匀分配时钟,从而减少设计中不同部分间的时钟偏斜。布局规划、布局、布线等步骤称为设计布局。在物理设计阶段,由于在初步实现阶段做出的假设逐渐固化,所以可能需要执行多次STA来完成一个更加精确的时序分析。 在这个阶段需要对IC布局进行验证,以确保满足以下条件: 1. 遵守代工厂制造芯片的所有规则,称为DRC,设计规则检查; 2. 布局匹配综合之后生成的网表,这称为LVS,布线图与原理图的比较,形式上电路布局对后综合网表进行验证。 一旦设计完成了DRC和LVS,sign off 静态时序分析就完成了。布局以后,不能保证设计满足时序要求,需要进行调整以满足时序和频率需求,sign off 静态时序分析完成后,生成设计的GDSII,GDSII是一个多边形的几何图形,它描述设计的实际布局,包括所有连线,fab厂根据相关的GDSII来生产芯片。 从逻辑综合到物理设计的全部流程称为RTL2GDSII流程,释放GDSII来生产芯片的过程称作Tapeout。 综上所述,ASIC设计流程如下:  |