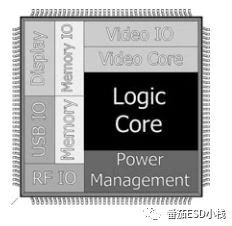

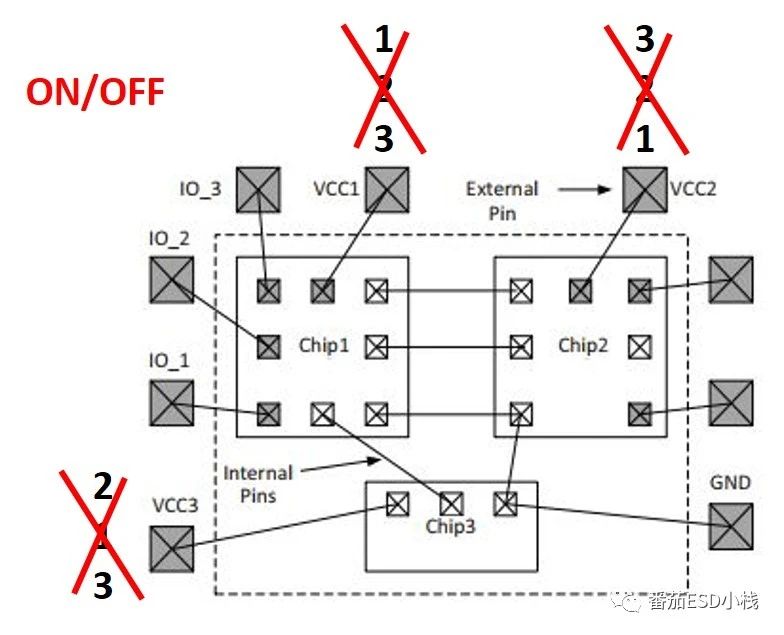

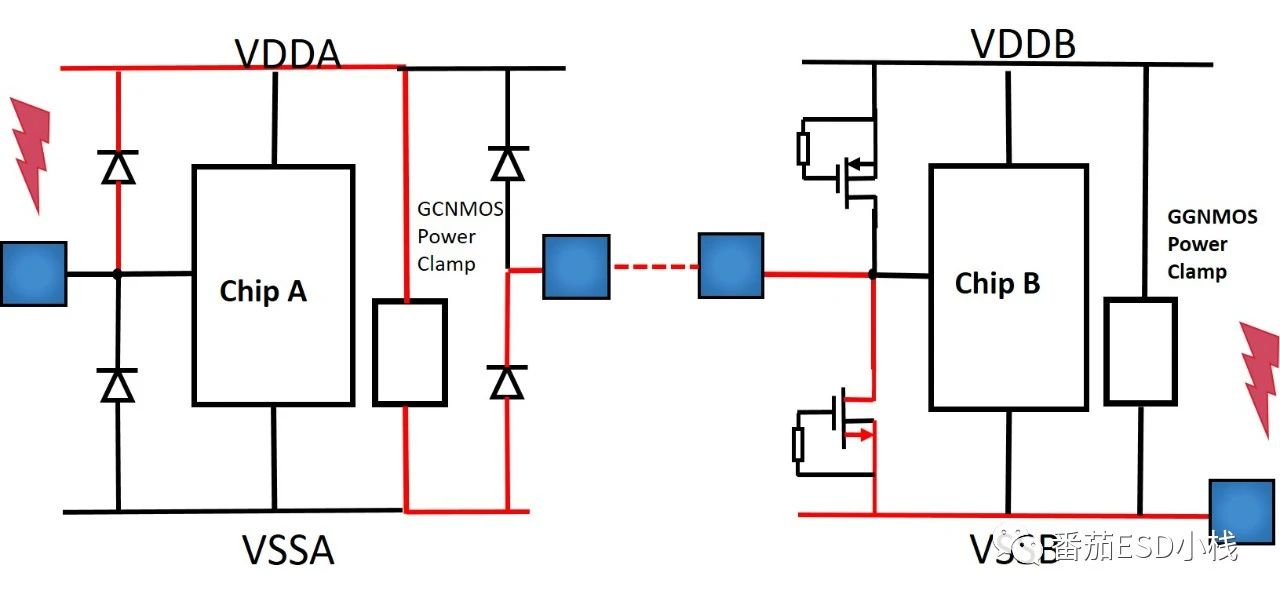

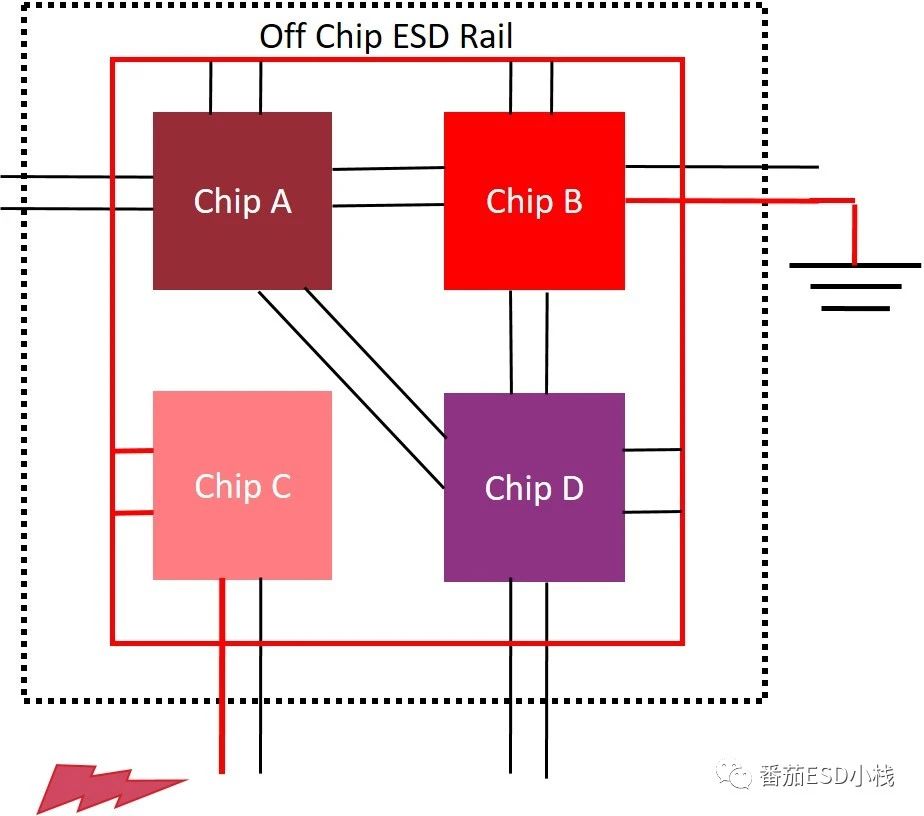

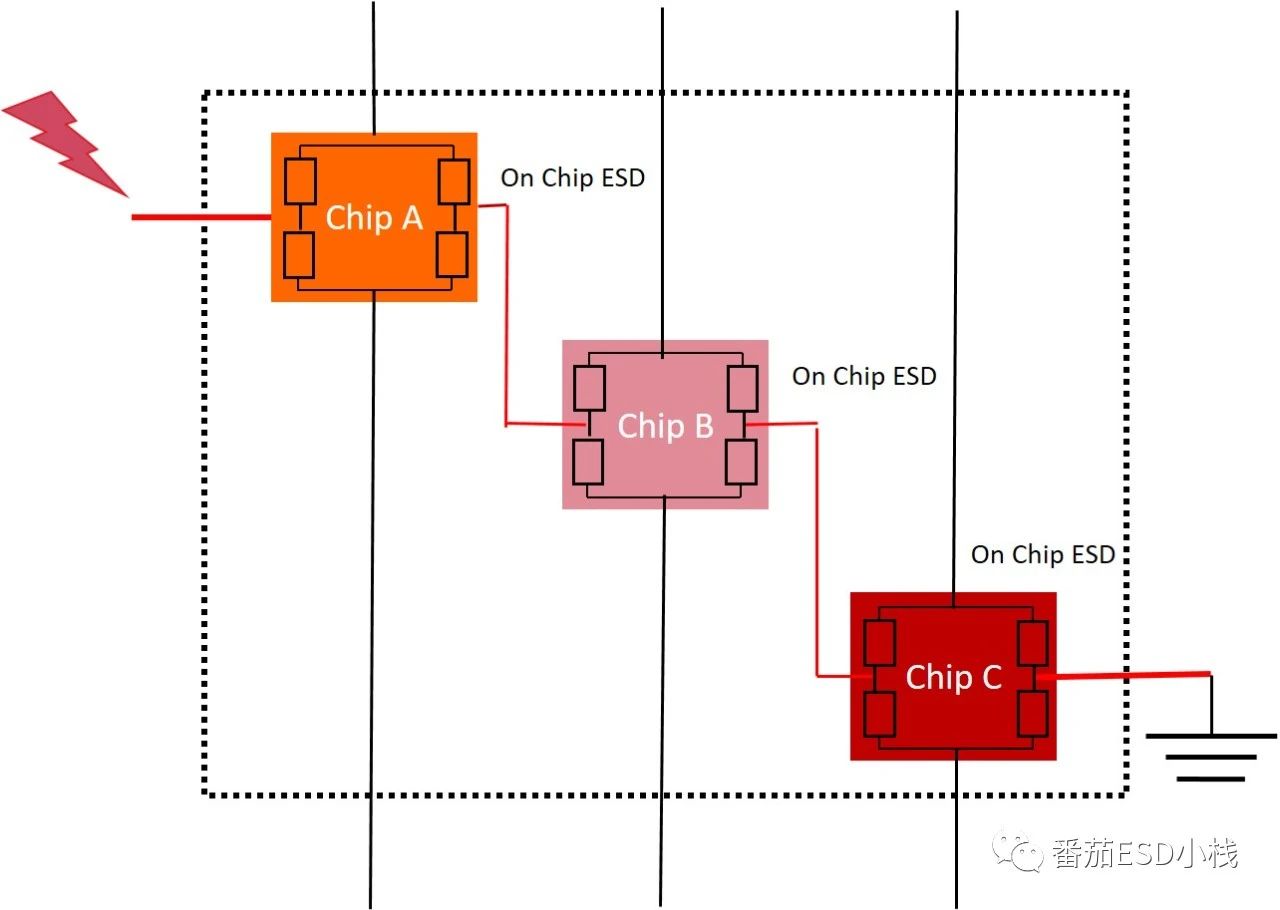

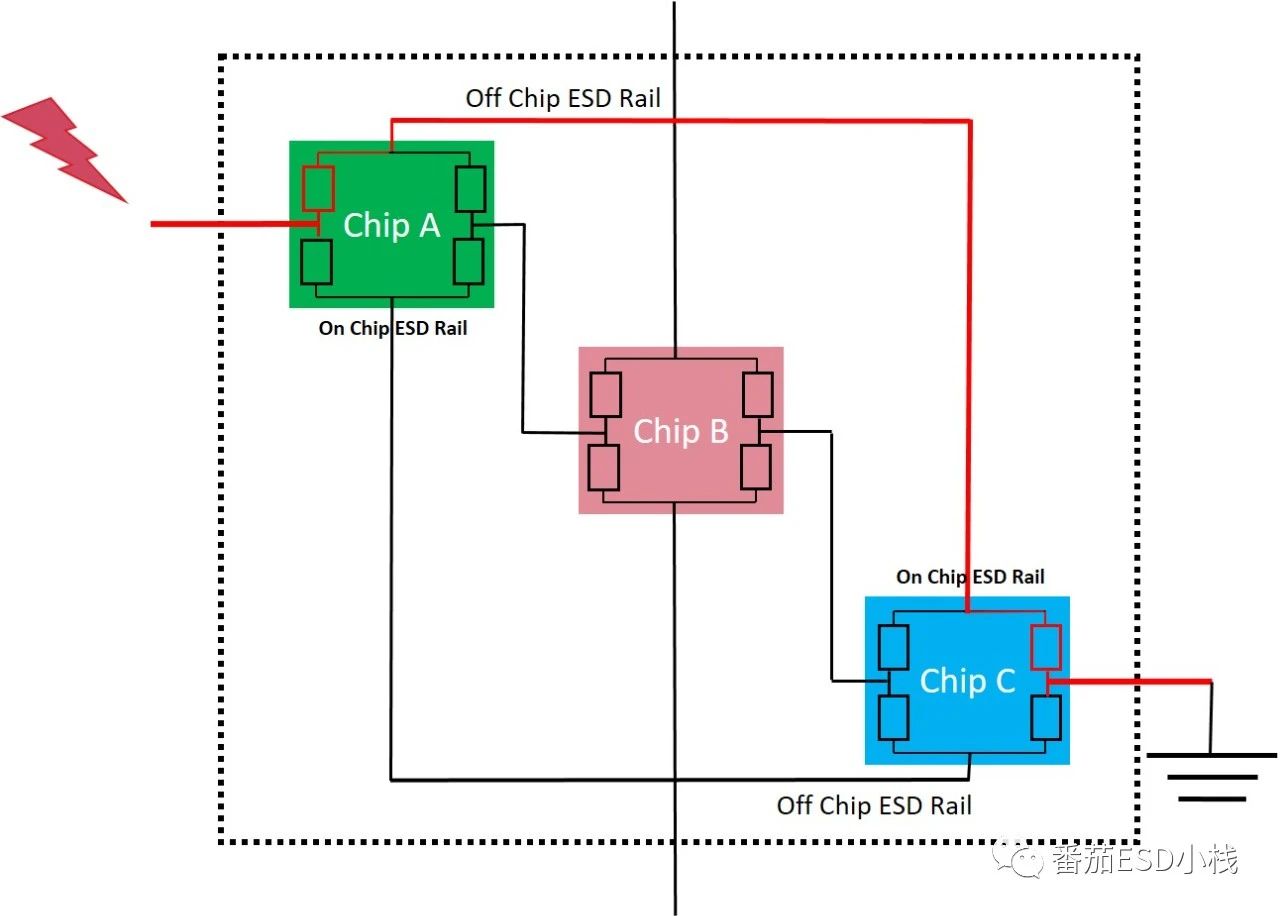

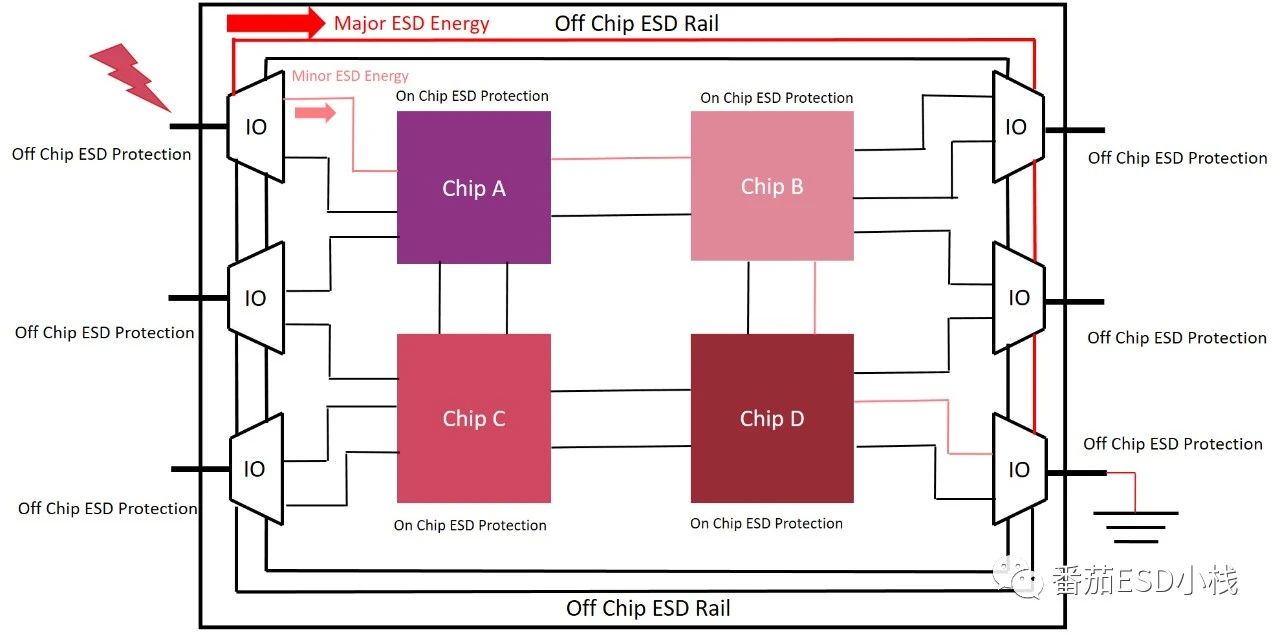

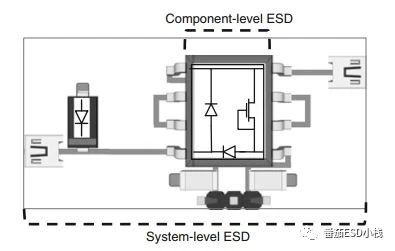

随着IC产业的发展,SIP (System In Package)为复杂的系统设计提供了解决方案。通过将不同的裸Die通过基板或者金线封装到同一框架内成为一个新的芯片,将多个芯片组合成一个微系统。SIP是一种自由度很高的设计方法,可以把不同功能,不同工艺,不同线宽的芯片通过封装的方式组合到一起,目前受到很多设计公司的青睐。但是这也为ESD设计带来了挑战,对多个芯片进行SIP封装可能会涉及到多电压域,正负电压输入范围,功率/信号隔离等ESD设计难点,对微系统进行ESD防护设计的难度远远大于对单个芯片进行ESD防护设计。 图一.SIP示意图。 通过SIP技术将多个Chip组成一个芯片,在赋予芯片更强大的功能时,也带来了更加复杂ESD情况,SIP封装后的芯片不仅需要拥有元器件级ESD防护能力(HBM,MM,CDM)同时还需要具有一定的系统级ESD防护能力。这里列出几点SIP ESD防护需要注意的技术关键点: 一.上下电顺序与上下电状态隔离。 如图二所示,SIP内的不同芯片上电/下电的状态与顺序无关,上电顺序不会对整个微系统的上电/下电状态产生影响。  图二.上下电顺序无法决定上下电状态。 Chip 1,Chip 2,Chip 3的上下电顺序不能影响整个系统的上下电状态。因为外部来源的VDD并非完全可靠,电源上总是会存在波动,浪涌,迟滞,过冲等非理想情况。尤其是针对一个系统,其电源来源于外部,上电过程并不能完全按照设想,所以不能以上电顺序来决定系统状态。尤其是模拟IC,有些项目的外接电源都不能满足IEC的相关标准。 二.信号引脚与任意电源轨间ESD防护策略的一致性。 任一信号引脚与任一电源轨之间的ESD防护器件都采用统一的防护策略,这样面对ESD时各个Chip能保证步调一致同步开启。如图三所示,Chip A和Chip B通过SIP键合到一起,Chip A采用Rail Based策略,Chip B采用Pad Based策略。当ESD由Chip A流入系统,Chip A 采用Rail Based策略,面对ESD时能瞬间启动。而Chip B采用Pad Based策略,需要等GGNMOS击穿才能构成泄放通路,这可能导致Chip A的ESD防护效率下降。  图三.芯片间防护策略的不一致。 反之,情况更差。当ESD由Chip B流入系统,Chip B内的寄生电容会改变ESD的本征波形,此时Chip A中RC静电检测网络对ESD的响应能力下降,会降低BigMOSFET的泄放能力。所以信号引脚与不同电源轨之间最好采用统一的ESD防护策略。 三.确保ESD通路的完整性。SIP内芯片与芯片之间可以没有连接关系,但是需要保持ESD通路的完整性。  图四.芯片间通过Off Chip ESD Rail建立ESD通路。 如图四所示,Chip C与其他Chip没有连接关系,但是处于同一Off Chip ESD Rail上,当Chip C有ESD事件时,ESD脉冲会通过Off Chip ESD Rail流出系统,降低了失效风险。如果没有Off Chip ESD Rail,Chip C上的ESD事件就会造成内部损坏。 如图五所示,虽然Chip A 和Chip C 没有直接的连接关系,但是这两个芯片通过Chip B建立了ESD泄放通路,当发生ESD事件时,ESD脉冲从Chip A流经Chip B到达Chip C,从而流出系统。这种方式比较简单,通过每个芯片的IO与On Chip ESD Rail实现ESD泄放,但是封装内的芯片工艺节点不一,ESD防护策略不同,ESD防护能力不同,整条通路的ESD防护能力由中间薄弱的环节决定,整个SIP的ESD防护等级都受制于其中最弱的芯片。且ESD路径较长,每个芯片的ESD防护单元都需要参与ESD泄放,会削弱整个SIP的ESD防护能力。  图五.芯片间直接建立ESD通路。 而为了提高SIP的ESD防护性能,就可以采用图六的Off Chip ESD Rail,利用金线或者基板将每个芯片的On Chip ESD Rail连接到一起构成Off Chip ESD Rail ,从而实现ESD泄放。  图六.芯片间Off Chip ESD Rail示意图。 因为SIP内部芯片复杂的电压域和芯片设计,对于ESD Rail的建立需要结合实际情况具体分析。而为了进一步提高系统可靠性,降低设计复杂度,可采用Off Chip IO设计。  图七.Off Chip IO/Off Chip ESD Rail设计。如图七所示,可以将SIP的IO分立设计,采用大线宽工艺制备IO Chip,将其作为Off Chip IO,对IO信号进行预处理并集成ESD防护设计,其与整个封装内部的Off Chip ESD Rail构成Off Chip ESD防护网络。而相对脆弱的芯片内部On Chip ESD防护网络协助ESD进行防护,这样Off chip ESD网络与On Chip ESD网络构成二极防护模式。当发生系统级ESD或HBM时,大部分能量通过Off Chip IO泄放到Off chip ESD Rail流出系统,小部分能量进入芯片,从芯片自身的On chip ESD防护电路泄放出系统。而发生CDM时,On Chip ESD网络响应速度快,能实现对CDM的防护。因为Off Chip IO的工艺选择余地较大,拥有很高的ESD防护潜力,而较为薄弱的Core Chip只需要面对小部分的ESD能量,而怎样设计First ESD Rail和Second ESD Rail就得具体问题具体分析了。进行SIP封装的芯片很多会涉及到不同的电压域和工作模块,SIP跨电压域/跨模块的ESD设计与片内跨电压域/跨模块的设计思路大同小异,都是需要在不同的电压域/模块间建立ESD泄放通道和隔离器件。 浅谈ESD防护—跨电压域ESD设计(一) 浅谈ESD防护—跨模块ESD设计 四.系统级防护与元器件级防护集成。如图八所示,芯片上PCB板后还需要进行ESD防护设计,以针对空气放电、接触放电、热插拔等系统级ESD现象进行防护。  图八.元器件级ESD设计与系统级ESD防护设计示意图。 以往Component-Level ESD设计与System-Level ESD设计分别归属不同的岗位,但是这种界限越来越模糊,现在模拟IC的大趋势就是赋予芯片System-Level ESD防护能力,这样可以增加集成度,降低设计成本。虽然没有准确的数字关系,但是Component-Level ESD的防护能力与System-Level ESD防护能力是呈正相关的,HBM的防护能力越高,针对IEC 61000-4-2和IEC 61000-4-5空气放电与接触放电的防护等级也越高。如图九所示,现阶段很多项目会把TVS/ESD Chip与芯片进行SIP封装,把独立的有源ESD防护器件与芯片连接到一起,从而实现System-Level ESD防护。  图九.芯片与TVS设计集成。 目前关于SIP ESD防护的文献相对较少,笔者只能以工作经验浅谈SIP中的ESD防护。笔者目前所做的SIP项目是全自主设计,每个进行SIP封装的芯片都是自家产品,每个Chip的ESD设计笔者都心知肚明,基于此点笔者能在设计之初就能统筹规划:每个芯片采用统一的ESD防护策略,预留跨电压域的ESD防护单元,统一ESD Rail电位,预留PAD作为ESD Rail接口,基板走线的规划,对IO寄生容忍度等。但是很多SIP设计不可避免的需要货架产品,这会大幅度提升SIP的ESD设计难度,留给工程师腾挪的余地有限。目前很多SIP产品是不需要ESD防护能力这个指标的,因为很多情况下SIP的设计很难兼顾ESD。但是笔者认为针对工业级和车规级去给SIP做ESD防护是件很划算的生意,因为封装内的芯片自身已经有ESD防护设计了,只需要在SIP内部进行小部分的设计就能利用芯片自身的ESD防护设计构成整个SIP的ESD防护网络,事半功倍。 |