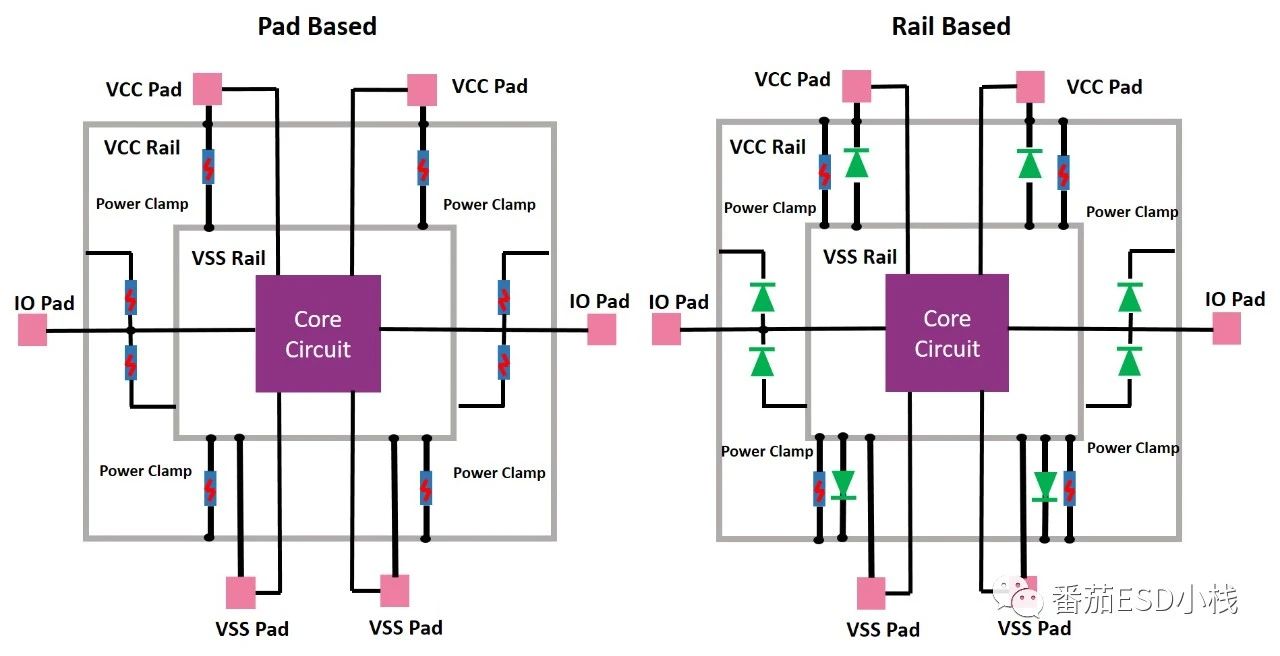

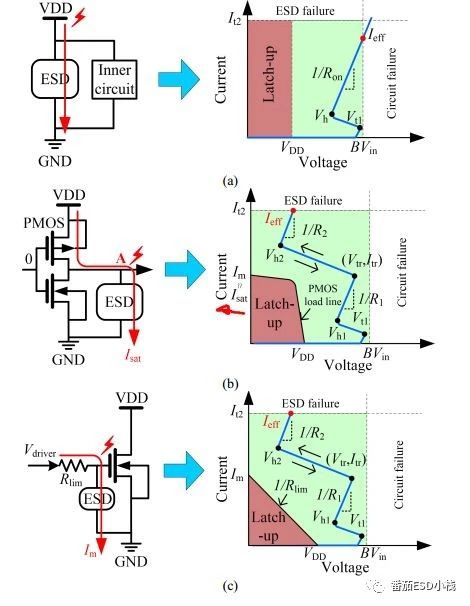

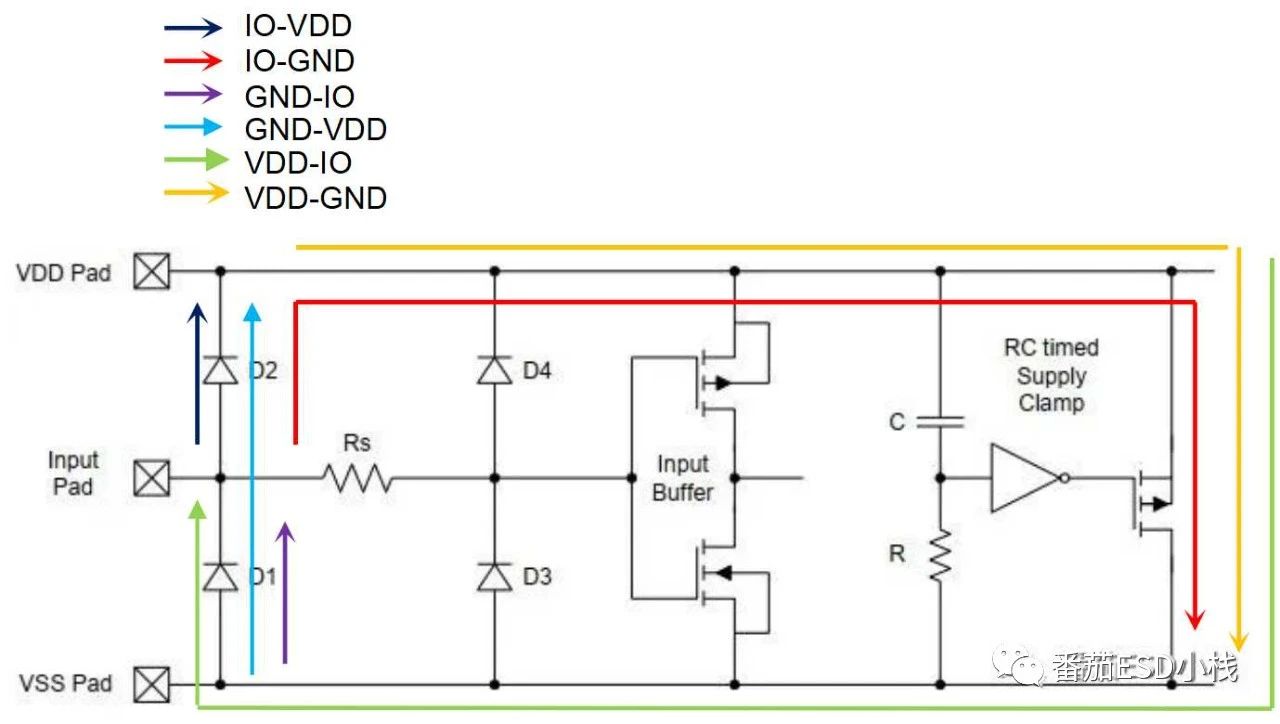

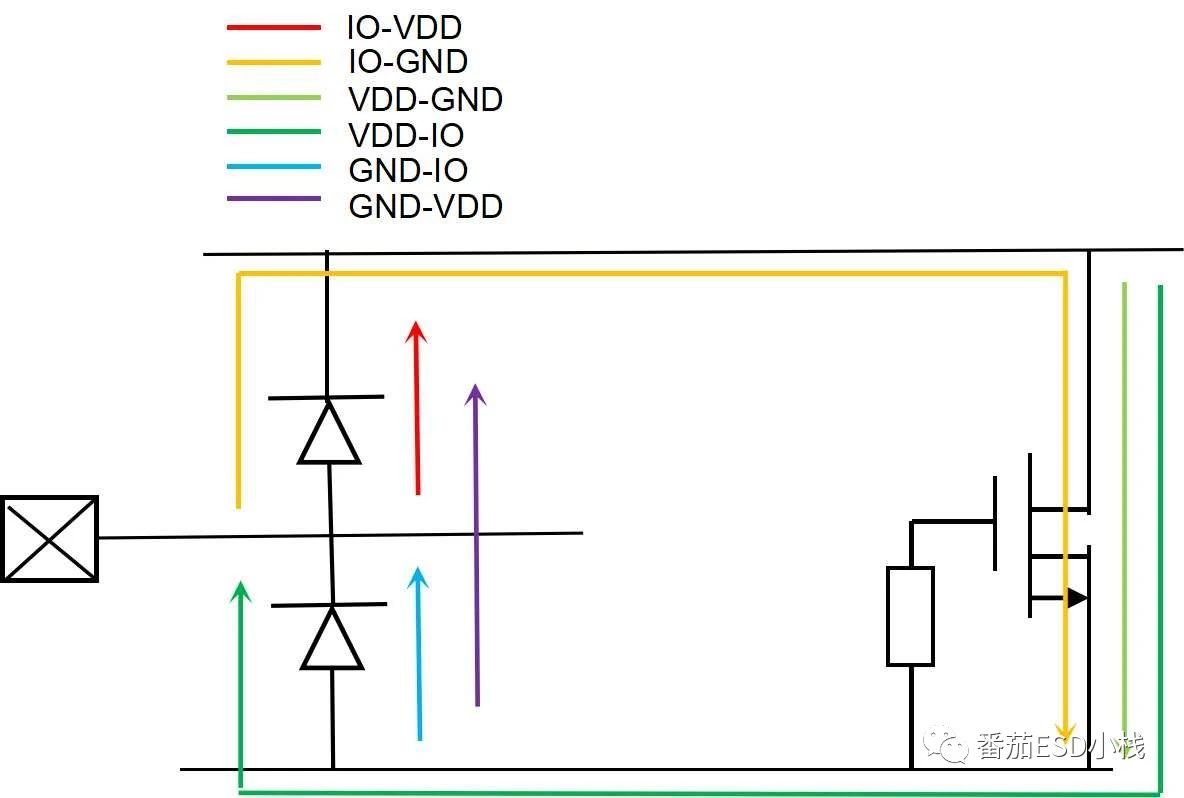

ESD设计遵循木桶原理,整个芯片的ESD防护能力由最弱处决定,所以ESD设计的核心思想之一就是牺牲局部最优解,换取全局最优解。工程师在进行全片ESD设计之前需要对芯片功能,SPEC等关键指标有一定认知。除此之外更要对工艺游刃有余,ESD设计与工艺有极强的相关性,虽然大部分fab都会提供ESD标准单元库,但是越来越多的定制化需求使得标准单元愈发捉襟见肘,很多时候需要工程师提供定制化解决方案。这就需要工程师具有器件设计能力,而这些都基于对工艺的熟悉程度。 一.ESD设计纪要: 在进行全片ESD防护设计前需要制定ESD设计纪要: 1. 芯片是否存在高低压混合的情况。 针对该问题笔者已经给出了常见情况下的设计方案,这里并不赘述。 浅谈ESD防护—跨电压域ESD设计(一) 2. 芯片是否存在多个模块类型。 针对该问题笔者也已经给出了常见情况下的设计方案,这里并不赘述。 浅谈ESD防护—跨模块ESD设计 3. 端口对于信号完整性是否有特殊要求。 在高速信号类的芯片设计中,对端口的寄生参数有很严格的要求,放置在端口的ESD器件会对信号产生负面影响,所以要设计低寄生ESD防护结构。 4. 是否存在特殊IO(负摆幅、高摆幅输入端)。 常规ESD防护结构都只能对摆幅在VSS与VCC间的信号进行防护,如果输入信号的摆幅超过上下限,就会带来风险。针对该类端口需要定制ESD防护电路与端口的隔离结构。笔者日后会专门讲解。 5. 高HBM/CDM防护等级。 常规模拟芯片只要求达到2000V HBM,500V CDM,但是在某些应用场景下会提出更高要求的ESD防护等级。 6. 系统级ESD需求。 接口芯片除了要面对芯片级的ESD风险外,有时还需要应对系统级ESD风险,诸如浪涌、空气放电、接触放电、雷击等。这类需求就涉及到片外防护与片内防护相兼容的问题,系统级ESD事件的能量是远高于芯片级ESD事件的能量。笔者日后会专门讲解。 7. 版图面积、布局布线约束等。 在设计之初就需要与版图工程师进行沟通,确保ESD设计能满足版图约束条件。 二.ESD防护策略: 笔者之前已经对大部分的ESD防护器件进行过介绍,但是在设计中各个器件的协同与整体电路的设计还需要一定的策略。如图所示,ESD防护有两种策略:Pad Based 和Rail Based策略。  图一.Pad Based和Rail Baesd策略示意图。 2.1 Pad Based全片防护策略: 通过ESD防护器件在PAD处就将ESD电流泄放到ESD Rail,Pad Based 防护策略大多采用Snap-back型器件,诸如GGNMOS,GDPMOS,SCR,Bipolar等,这类器件表现出负微电阻特性,正常工作时关断,ESD时开启。 浅谈ESD防护设计—NMOS的妙用(一) 浅谈ESD防护设计—NMOS的妙用(二) 浅谈ESD防护—SCR(一) 浅谈ESD防护—SCR(二) 浅谈ESD防护—三极管的应用 浅谈ESD防护—PMOS的应用 Pad Baesd策略的设计重点是Design Window,要让ESD器件在正常工作时不会启动,以避免发生短路或闩锁的情况。关于不同端口的Design Window之前已经提过,这里就重复一下: 浅谈Latch-up(一)  图二.不同端口的Design Window。 如图二所示:a)作用于VDD与GND之间的Power Clamp,其Holding Voltage不能小于VDD+10%。VDD的驱动能力近似是无穷大的,如果ESD器件的Holding Voltage进入latch up区,使用过程中一旦VDD的扰动开启ESD器件,ESD器件的低阻通路会一直开启,直到烧毁。 b)作用于输出级的ESD防护器件,其Design Window为VDD+10%,Im+10%的PMOS负载曲线,因为PMOS进入饱和区后存在沟道夹断效应,其过电流能力有限,所以Latch-up区的电流上限有限。ESD器件的Holding Voltage和Holding Current一旦进入PMOS的Latch-up区,PMOS会形成对ESD器件的持续上拉,带来失效风险。 c)作用于输入级的ESD防护器件,其Design Window为VDD+10%,Im+10%的栅级负载曲线,大部分ESD器件都能避免Latch-up风险。 如果是ESD器件是作用于端口与VDD之间,其栅极输入的Design Window与端口对GND一致,而输出级的Design Window需要关注NMOS的负载曲线,避免进入NMOS的下拉负载区内,形成导电通路。 2.2 Rail Based防护策略: 在PAD处放置二极管,另在VDD Rail与VSS Rail之间放置Power Clamp。具体工作情况如图所示: 浅谈ESD防护—二极管的应用(一) 浅谈ESD防护——二极管的应用(二)  图三.二极管+GCNMOS ESD网络工作原理图。 Rail Based全片防护策略普遍采用GCNMOS作为Power Clamp。这种防护策略只需要做频率特性,不用考虑Design Window,且GCNMOS能通过仿真得出栅电,对于设计比较友好。 浅谈ESD防护设计—GCNMOS(一) 浅谈ESD防护—GCNMOS(二) 如图四所示,也有设计师采用GGNMOS作为Power Clamp,虽然都是利用NMOS构成Power Clamp,但是两种设计的工作原理与TLP曲线差异很大,所以在某些设计细节上这两种器件会有一定差异。  图四.二极管+GGNMOS ESD网络工作原理图。 Pad Based策略在端口处会有较大的寄生电容,对高频信号不友好,且需要兼顾器件的Design Window,面积需求少。但是在高压端口、特殊输入端口、TTL电路以及负电压供电下只能应用此种策略。而Rail Based策略需要很大的面积去放置RC,同时需要在VCC Rail和VSS Rail中插入很多Power Clamp,但是寄生电容弱且对CDM防护性能优异。这两种策略本身并不冲突,数字IO可以采用Rail Based防护策略,而特殊端口可采用Pad Based 防护策略,但是设计时需要确保ESD的一致性和完整性。总之,笔者认为全片ESD防护设计是一种自上而下的设计方法,需要先从顶层需求、芯片工艺等方面制定设计大纲,然后再考虑设计策略与端口的特性,其次再落实到具体的ESD防护设计,期间还要不停的和版图与电路设计人员进行沟通,trade off贯穿整个设计流程。 |