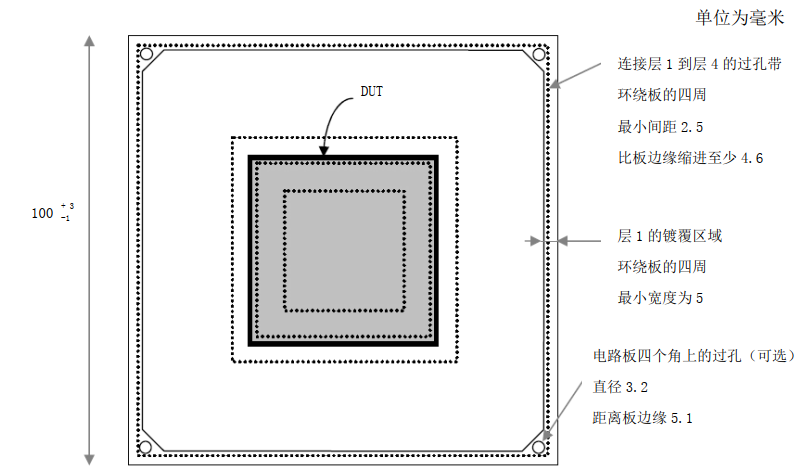

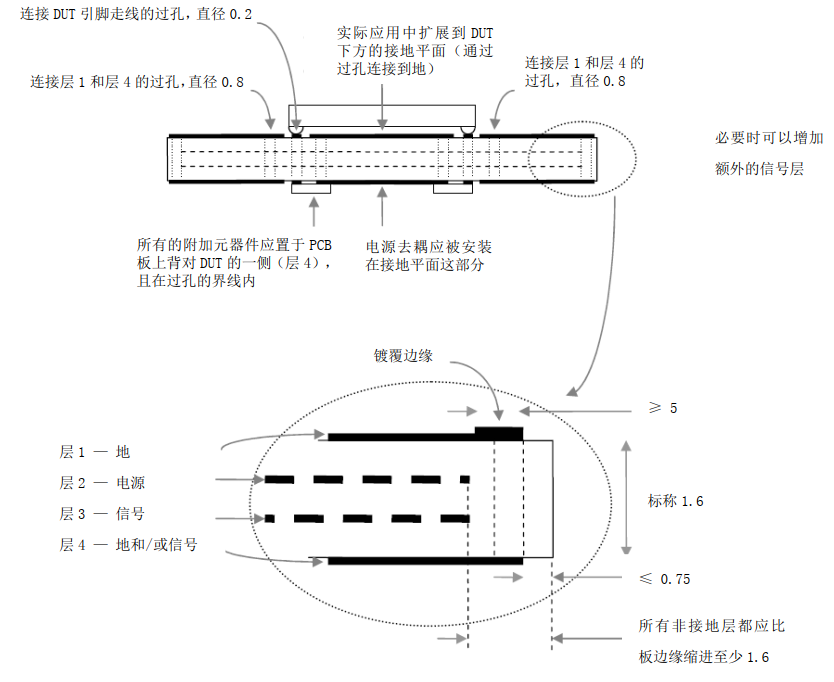

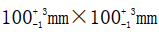

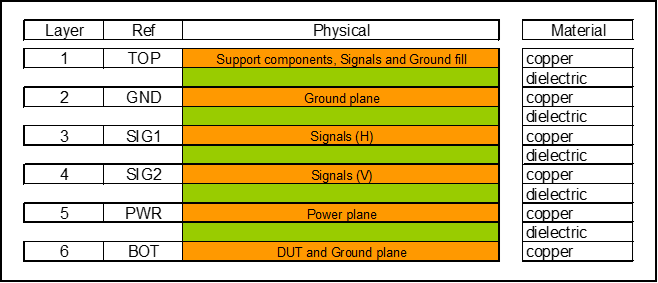

这期给大伙介绍下芯片电磁兼容测试的专用测试板的设计指南。通常,系统级的电磁兼容测试都是针对产品(成品板卡),应用场景怎么用就怎么搭建测试环境。而芯片不同,芯片种类繁多,单颗芯片应用场景也不是单一的,因此为了保证实验的可重复性和一致性,以及适配专用的EMC测试环境和设备,需要取典型的应用场景,设计专用的测试板来进行测试。PCB测试板的最小要求如下图所示,下面分别对各项设计规则进行说明。  板子的结构 板子的大小为  ,推荐板厚为1.6mm,在板角处可以加孔,板的所有边缘参考地至少应镀锡或露铜5mm,使之导电以便与TEM(横电磁波小室)小室的参考地良好接触(使用TEM小室时),也可以选择在板子的边缘镀金。板边缘的过孔应距离边缘至少5mm远。 ,推荐板厚为1.6mm,在板角处可以加孔,板的所有边缘参考地至少应镀锡或露铜5mm,使之导电以便与TEM(横电磁波小室)小室的参考地良好接触(使用TEM小室时),也可以选择在板子的边缘镀金。板边缘的过孔应距离边缘至少5mm远。板子的叠层与布局 建议最小叠层为2层板,可根据测试系统的复杂程度、布局布线的复杂程度和信号完整性要求,采用4层板、6层板或更多层的叠层结构。6层的叠层设置举例见下图,被测芯片放置在有完整接地平面的层6,所有其它的辅助电路模块都放置在层1,尽可能完整地铺地。  板子过孔 在芯片外侧的所有过孔直径应为0.8mm,所有其他过孔直径应不小于0.2mm。因为测量达到1GHz,需要考虑最大横向过孔间距。连接第1层和第4层的过孔的最大间距10mm。 连接信号走线的过孔应尽可能靠近连接第1层和第4层的过孔,以减小信号回路。 其它设计要求 板子上的电源去耦和IO的负载设计需结合芯片的典型应用场景的推荐电路进行设计。此外,针对传导耦合测试,对应耦合网络的走线还需要保证50Ω的阻抗,使之与测试设备的特征阻抗匹配。 |