|

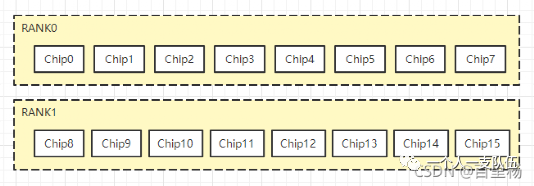

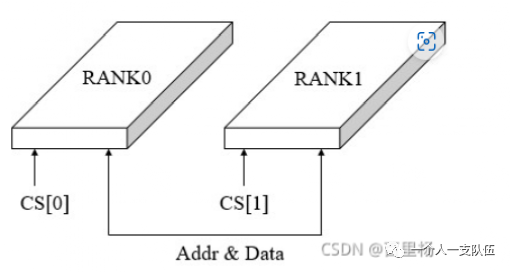

3.3.2 多RANK的意义 假设内存通道位宽为64bit,即一个RANK为64bit,每一个64bit位宽背后都是由若干个颗粒组成的。 比如,使用16颗8bit位宽内存芯片,分别组成2个RANK,如下图所示:  我们可以把原本两根物理DIMM的内存颗粒全部安装在一块内存印刷电路板上,使得一根内存条具备两倍的内存容量。 这就相当于,物理上虽然只有一根内存条,但是通过划分不同的RANK,在逻辑上可以看成是2根内存条。 同一个RANK内部的所有内存颗粒chips,连接到同一个CS(Chip Select,片选)信号线上,内存控制器能够对同一个RANK的所有chips同时进行读写操作,而在同一个RANK的chip也分享同样的控制信号。在RANK选择好后,RANK内部的所有内存颗粒一起被选中,共提供64bit的数据。  对于上面图中,也就是说,RANK0和RANK1共享同一组addr/command信号线,利用cs片选线选择欲读取或是写入的那一组内存颗粒,之后,就可以对这一组内存颗粒进行读写。

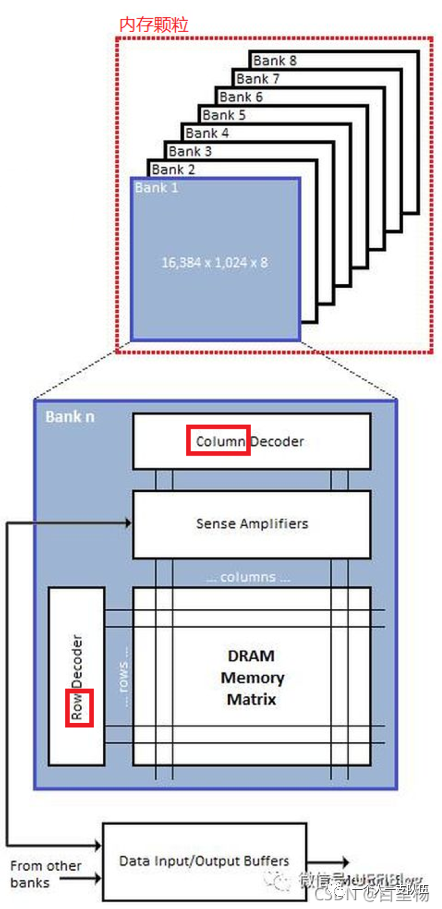

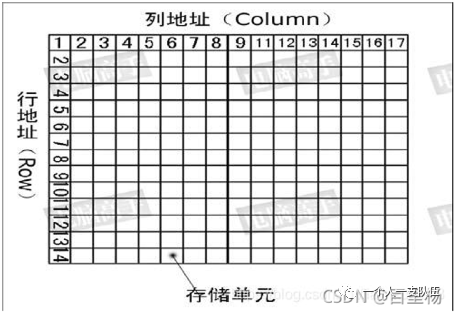

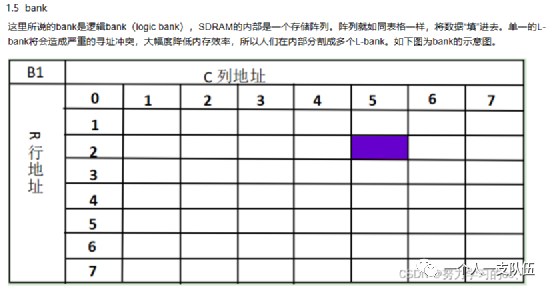

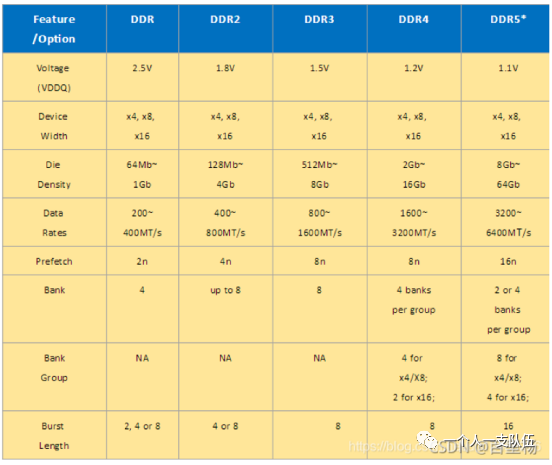

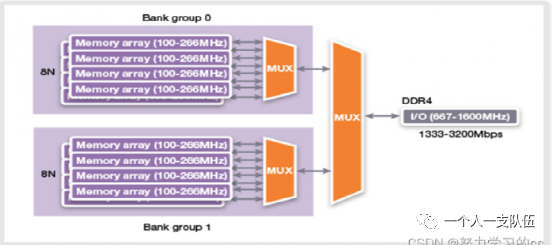

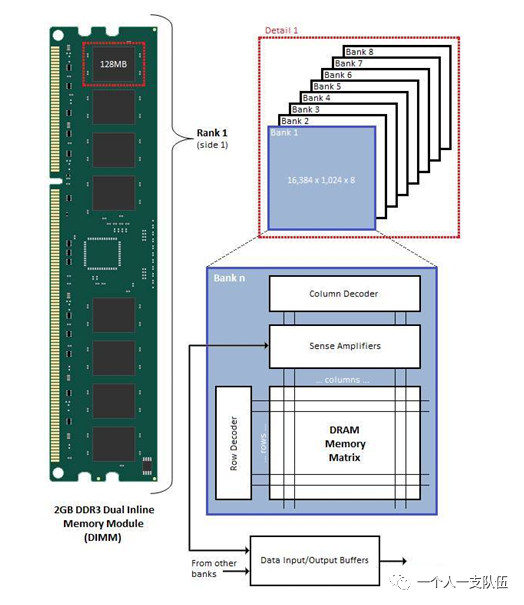

3.4 Chip 1Chip是内存条上的一个芯片,俗称内存颗粒。由图中是由8个bank组成了一个memory device。  3.5 Bank 我们把某型号128MB内存颗粒拆开来看,它是由8个Bank组成,我们也称为Logical Bank(逻辑Bank)。每个Bank就是一个存储矩阵,就像一个大方格子阵。一般来讲,每个Bank中格子数量是相同的。这个格子阵有很多列(Column)和很多行(Row),这样我们想存取某个格子,只需要告知是哪一行哪一列就行了,这也是为什么内存可以随机存取而硬盘等则是按块存取的原因。   图中,1638410248字样,表示一个Bank中由16384行,1024列组成,每个格子可保存8bit,也就是1字节数据。那么每行可以存储1024*8bit=1KB。每行的存储容量,称为Page Size。 内存颗粒内部逻辑层次,如下:  1Bank:Bank是一个逻辑上的概念。一个Bank可以分散到多个Chip上,一个Chip也可以包含多个Bank.Bank和Chip的关系可以参考下面的图,每次读数据时,选定一个Rank,然后同时读取每个chip上的同一bank.  3.6 Bank group 随着颗粒容量提升,bank数越来越多,到DDR4时出现Bank Group,我们可以理解为,将多个Bank编成一个组,这个组就是Bank Group。如下:  Device Width:颗粒位宽,常见为4/8/16bit。 Die Density:颗粒密度,也就是容量,随着DDR代数迭代,容量越来越大。 Bank:DDR4以前是没有Bank Group的,所以该值就表示整个颗粒中Bank数量。但是在DDR4和DDR5中,就表示每个Bank Group中Bank的数量,整个颗粒Bank数量 = Bank Group * Bank。 Bank Group:Bank分组数量,该特性只存在于DDR4和DDR5中。 在DDR4中才有的概念,每个Bank Group可以独立读写数据,这样一来内部的数据吞吐量大幅度提升,可以同时读取大量的数据,内存的等效频率在这种设置下也得到巨大的提升。DDR4架构上采用了8n预取的Bank Group分组,包括使用两个或者四个可选择的Bank Group分组,这将使得DDR4内存的每个Bank Group分组都有独立的激活、读取、写入和刷新操作,从而改进内存的整体效率和带宽。如此一来如果内存内部设计了两个独立的Bank Group,相当于每次操作16bit的数据,变相地将内存预取值提高到了16n,如果是四个独立的Bank Group,则变相的预取值提高到了32n。  1Row/Column组成的Memeory Array:Bank可以理解为一个二维数组bool Array[Row][Column]。而Row/Column就是指示这个二维数组内的坐标。注意读取时每个Bank都读取相同的坐标。 这次我们来看看rank和Chip里面有什么,如下图:  这是个DDR3一个Rank的示意图。我们把左边128MB Chip拆开来看,它是由8个Bank组成,每个Bank核心是个一个存储矩阵,就像一个大方格子阵。这个格子阵有很多列(Column)和很多行(Row),这样我们想存取某个格子,只需要告知是哪一行哪一列就行了,这也是为什么内存可以随机存取而硬盘等则是按块存取的原因。 实际上每个格子的存储宽度是内存颗粒(Chip)的位宽,在这里由8个Chip组成一个Rank,而CPU寻址宽度是64bit,所以64/8=8bit,即每个格子是1个字节。选择每个格子也不是简单的两组信号,是由一系列信号组成,以这个2GB DDR3为例:  |