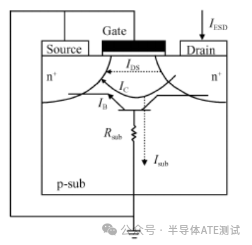

静电放电(Electrostatic Discharge, ESD)是不同静电电位物体间的电荷快速转移现象,对集成电路而言,其瞬时能量释放可产生数十安培电流与数千伏电压,远超IC正常工作的物理极限(如 28nm 工艺栅氧化层仅能承受约 100V 电压)。今天我们将从IC 各阶段ESD 风险点,ESD 对IC的影响,ATE 测试过程实例分析等方面对ESD 进行相关探讨。一、ESD 背景及简介:从现象到行业刚需ESD 威胁贯穿 IC 全生命周期,各阶段风险点明确: 制造与封装阶段 晶圆切割、引线键合、芯片贴装过程中,机械摩擦(如晶圆与载具、塑封料与芯片)易积累静电荷,若未及时中和,可能击穿薄栅氧化层或烧毁金属互联线; 测试阶段(ATE) · 探针卡与引脚的高速接触、测试插座(Socket)的机械动作、机械手臂的传送摩擦,均为 ESD 高风险环节,尤其CDM(带电器件模型)事件频发; 系统应用阶段 终端用户插拔设备(如 USB、HDMI 接口)、人体直接接触端口,可能引入ESD 应力,对汽车电子、航空航天等可靠性敏感领域威胁更大。 当前,JEDEC JESD22 系列标准(如 HBM 测试的 JESD22-A114、CDM 测试的 JESD22-C101)已成为行业统一规范,ESD 防护也从 “可选优化” 升级为保障芯片良率、可靠性与企业声誉的强制性要求。 二、静电对 IC 器件的影响:从物理损伤到隐性风险ESD 对 IC 的破坏源于热二次击穿与高电场击穿两大核心机制,具体表现为三类显性失效与两类隐性影响,直接增加 ATE 测试的复杂度与误判风险: 1. 显性物理损伤:瞬时不可逆破坏 2. 结区烧毁(Junction Burnout):最常见的 HBM 失效模式。ESD 电流流经PN 结时,局部焦耳热使温度骤升至数千摄氏度,形成熔融通道,导致PN结短路或漏电(如二极管正向压降异常、三极管电流放大系数骤降); 氧化层击穿(Gate-Oxide-Breakdown):IC中数纳米厚的栅氧(如 65nm 工艺约3-5nm)无法承受ESD高压,发生介电击穿后,栅极与沟道直接短路,MOS管彻底丧失开关功能,这是高速逻辑芯片(如CPU、FPGA)的主要 ESD 失效形式; 金属互联熔断(Metal Melt):ESD 大电流(如CDM 放电可达上千安培)流过金属互联线(尤其是宽度< 1μm 的铜线)时,焦耳热使其熔化断裂,通常伴随其他失效发生(如结区烧毁后电流集中导致金属线熔断)。 2. 隐性性能劣化:潜伏性风险 参数漂移:低强度ESD未造成显性损伤,但会导致器件电学参数偏移(如 MOS管阈值电压 ±0.1V 偏移、运算放大器输入失调电压增大),ATE 测试中可能表现为 “边缘合格”,长期使用后易出现早期失效; 可靠性下降:受损部位(如氧化层局部缺陷)在高温、高湿环境下逐渐恶化,使IC寿命缩短(如消费类芯片从5年寿命降至2年),这类风险在ATE常规功能测试中难以察 三、ESD 元器件测试模型详解:场景模拟与 ATE 测试启示为量化 IC 抗 ESD 能力,行业定义了四类测试模型,分别模拟不同应用场景的放电事件,其特性差异直接决定 ATE 测试的设备配置、流程设计与风险防控重点:

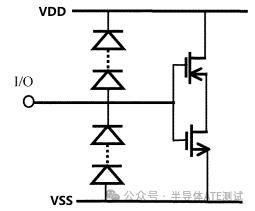

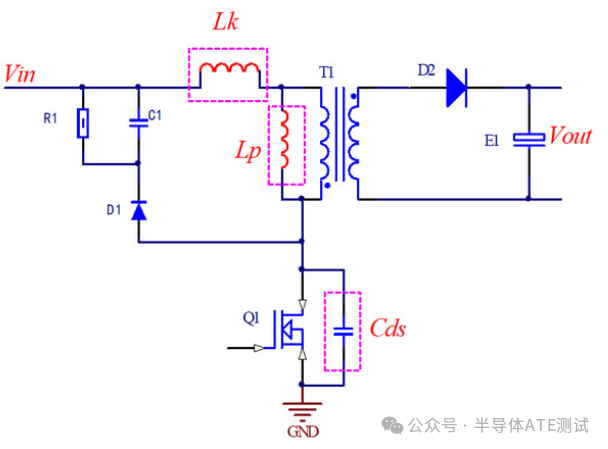

四、IC 常见 ESD 失效场景总结:全生命周期风险图谱结合ATE测试实践与产业链痛点,IC 的 ESD 失效可按阶段归纳为五大场景,其中测试阶段的失效因 “批量性” 与 “误判风险” 对企业影响最直接: 制造阶段:源头风险 晶圆加工:离子注入时高能离子与晶圆摩擦生电,若静电未中和,可能导致光刻图形偏移;切割过程中晶圆边缘与刀片摩擦,易引发边缘芯片氧化层击穿; 封装环节:引线键合时焊头与焊盘的接触分离产生静电,可能烧毁焊盘金属层;塑封料与芯片表面摩擦(尤其固化收缩时),易破坏钝化层,形成ESD放电通道。 ATE测试阶段:高风险核心环节 探针接触失效:探针卡与引脚接触瞬间,若存在电位差(如探针未接地),易引发CDM 放电,导致IC 内部防护器件误触发(如SCR 闩锁),ATE 误判为“功能失效”; Handler操作风险:芯片在Pick-and-Place过程中与吸嘴摩擦带电,接触地测试座时发生 CDM 放电 人工操作疏漏:工程验证阶段,人工拿取芯片未戴防静电手环,引入HBM损伤,这类失效具有潜伏性,可能流入客户端后爆发。 仓储与运输阶段:隐性风险 普通塑料包装(如聚乙烯)与芯片摩擦生电,且无法释放电荷,导致芯片长期处于高静电环境; 运输箱堆叠过高,芯片间挤压摩擦产生静电,若缺乏防静电泡沫,可能引发 “批量轻微损伤”。 五、IC 片上 ESD 保护器件结构及功能解析 片上ESD保护器件是IC的“内置免疫系统”,核心功能是快速开启低阻抗泄放通道,将引脚电压钳位在安全范围,保护核心电路。其设计需兼顾防护性能ATE测试兼容性,常见结构及防护网络如下: 核心保护器件:特性与应用场景 二极管型防护器件 结构:普通二极管、齐纳二极管、双向二极管,利用PN结正向导通或反向击穿特性; 工作原理:I/O引脚接正向二极管到VDD、反向二极管到VSS,正向 ESD 时 VDD 侧二极管导通泄流,反向 ESD 时 VSS 侧二极管导通; 优势:响应速度<1ns,工艺兼容性好(可与CMOS 工艺集成); 局限:钳位电压较高(普通二极管~0.7V,齐纳管5-20V),适用于中低压I/O接口(如UART)  栅极接地NMOS(GG-nMOS) 结构:NMOS管栅极接地,漏极接I/O引脚,源极接VSS,利用寄生NPN 晶体管的雪崩击穿特性; 工作原理:ESD 高压使漏极- 衬底 PN 结雪崩击穿,产生的载流子触发寄生NPN 导通,形成漏极- 源极泄放通道; 优势:电流承载能力强(可达数百毫安),适用于电源轨VDD-VSS防护; 注意:需控制栅极氧化层厚度,避免ESD 高压击穿。  晶闸管(SCR)型防护器件 结构:P-N-P-N 四层结构,阳极接 I/O 引脚,阴极接 VSS,栅极可控制触发; 工作原理:ESD电压超过击穿电压时,SCR导通,钳位电压(1~5V),泄流能力强; 风险:易发生闩锁效应(如保持电压< 正常工作电压) 电源钳位电路(Power Clamp) 结构:RC 触发网络+ SCR/GGNMOS,连接在 VDD 与 VSS 之间; 工作原理:ESD 快速电压瞬变使 RC 网络充电,触发钳位器件导通,泄放电源轨上的 ESD 电流; 应用:防止ESD通过电源轨扩散到核心电路,是CPU、GPU等高端芯片的必备防护结构。  HighLight: ESD完整防护网络--三条核心路径 一个可靠的 I/O 引脚 ESD 防护系统需形成 “保护环”,包含三条协同路径: 1.I/O→VSS路径:由GG-nMOS或反向二极管构成,泄放I/O引脚的负向ESD流; 2.I/O→VDD路径:由正向二极管或齐纳管构成,泄放 I/O 引脚的正向ESD电流; 3.VDD→VSS路径:由电源钳位电路构成,泄放电源轨间的ESD电流,避免核心电路受电源域 ESD 冲击。

|