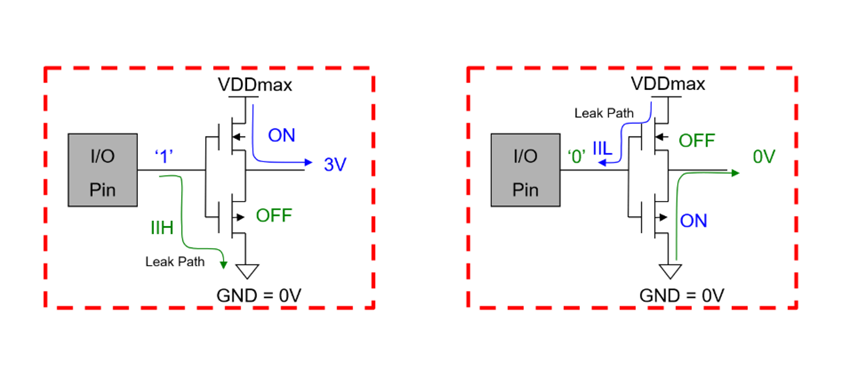

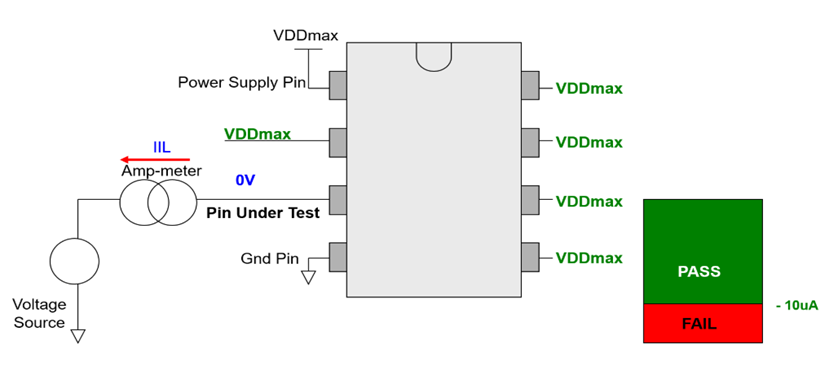

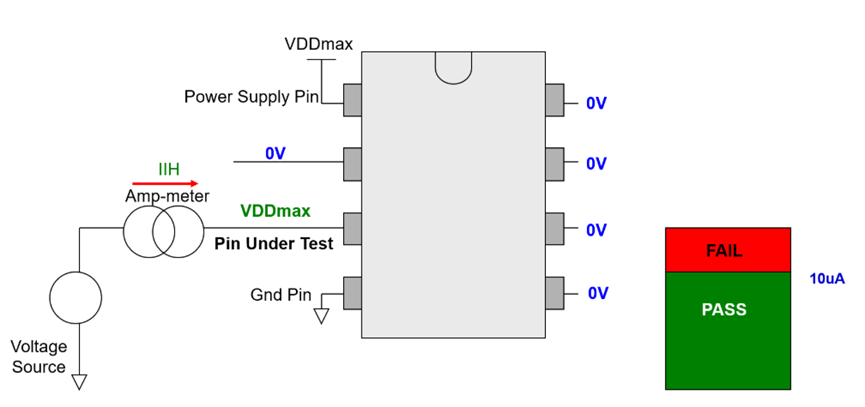

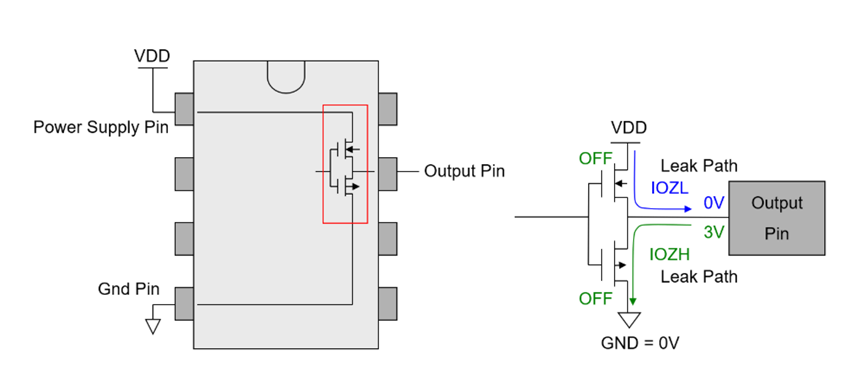

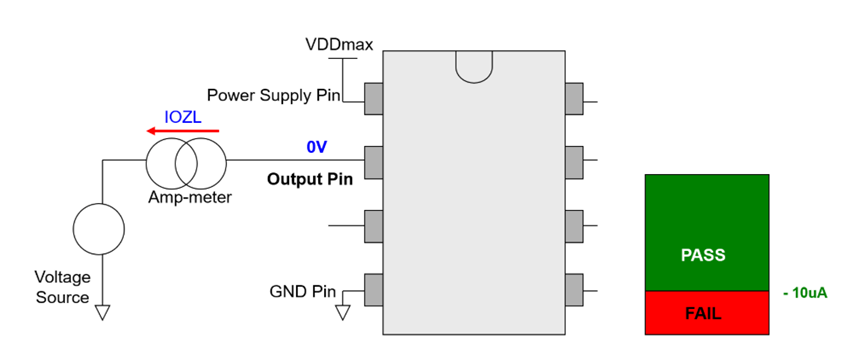

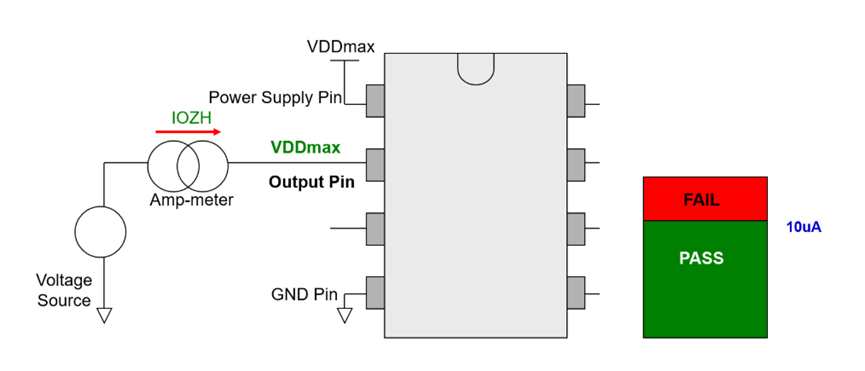

ATE-芯片漏电流测试Leakage Test输入漏电流测试(IIL和IIH) IIH/IIL是属于直流DC测试中leakage测试范畴,IIH和IIL是两个测试,测试方式都是针对输入管脚进行加压测流。  IIH(input current high)指的是输入管脚为逻辑高电平(H)时,输入管脚到地VSS的漏电流,也可以说是针对输入阻抗的衡量。 IIL(input current low)指的输入管脚为逻辑低电平(L)时,输入管脚到地VDD的漏电流,同IIH一样也可以说是针对输入阻抗的衡量,只是路径的差异。 漏电流测试包括输入漏电流测试(IIL&IIH)和输出三态漏电测试 (IOZL&IOZH)。输入漏电发生在输入引脚的缓冲电路中。IIH是DUT驱动为“1”时从输入引脚到GND的漏电路径,而IIL是驱动为“0”时从 VDD到输入引脚的漏电路径:  实际上,IIL的测量值是输入引脚到 VDD的电阻值,而IIH是输入引脚到GND的电阻值。输入漏电测试是为了确保引脚的输入缓冲器不会产生或吸收超过规定的不必要电流。 测试方法(串行) 串行输入漏电测试(IIL和IIH)是通过施加VDDmax 电压,将特定输入引脚强制至VDDmax(对于IIH)或0V(对于IIL),同时将其他输入引脚强制至被测引脚的对侧。 Test Method (Serial)  1.将VDDmax应用于VDD引脚(带有电流钳)。 2.将所有输入引脚(除测试引脚外)的VDDmax设置为最大值。 3.将0V施加到测试引脚下,并测量流出的电流: · 高于规格值(>-10uA):通过 · 低于规格值(<-10uA):失败 4.重复以测试下一个引脚 IIH Test (Serial)  1.将VDDmax应用于VDD引脚(带有电流钳) 2.对所有输入引脚(除测试引脚外)施加 OV 电压。 3.将VDDmax施加到测试引脚下,并测量流入: · 高于规格值(>10μA):失败 · 规格值(<10微安):通过 4.重复以测试下一个引脚。 测试方法(并行) 由于串行方法可以识别输入引脚之间的漏电流,但效率太低。并行测试法实际上更常用。并行法中使用PPMU,将所有输入引脚驱动到最大VDD(对于 IIH)或 0V(对于IIL),然后测量每个输入引脚的电流。 并联方法的唯一缺点是无法检测到引脚间的漏电,因为所有引脚都会同时被强制到相同的电压水平。 输出三态漏电流测试(IOZL 和 IOZH) 三态也称为高阻态或浮动态,表示DUT引脚外部出现高阻抗。输出三态漏电流发生在DUT的输出引脚上施加高电平或低电平时,而该引脚的先决条件是禁用。IOZL表示施加低电平时流出的电流,IOZH 表示施加高电平时流入的电流。  基本上,IOZL 表示禁用时输出引脚到VDD的电阻,IOZH表示到 GND的电阻。该测试确保引脚不会源入或源出超过规定的多余电流。 此外,该测试还需要一个控制输入(使能信号),以将特定输出引脚控制为低电平、高电平或高电平Z(禁用)状态。 Test Method (Serial) IOZL Test (Serial)  将VDDmax应用于VDD引脚(带有电流钳) 2.将特定的输出引脚预置为Hi-Z(禁用)状态。 3.将0V施加到测试引脚下,并测量流出的电流: · 高于规格值(>-10uA):通过 · 低于规格值(<-10uA):失败 4.重复以测试下一个引脚 IOZH Test (Serial)  1.将VDDmax应用于VDD引脚(带有电流钳)。 2.将特定的输出引脚预置为Hi-Z(禁用)状态。3.将VDDmax施加到测试引脚下,并测量流入: · 高于规格值(>10μA):失败 · 低于规格值(<10微安):通过 4.重复以测试下一个引脚 Test Method (Parallel) 并联法实际上更常用于PPMU,将所有输出引脚驱动到最大VDD(对于IOZH)或0V(对于IOZL),然后测量每个输出引脚的电流。 |